完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

和所有的數字電路一樣,毛刺也是FPGA電路中的棘手問題,它的出現會影響電路工作的穩定性,可靠性,嚴重時會導致整個數字系統的誤動作和邏輯紊亂。...

執行算法邏輯(加、減、乘、除及復雜的組合運算)優化。例如,乘法器有多種實現方式, 相應地會產生多種時序、功耗及面積,如何根據目標設定選出最合適的結構將對最后的綜合結果有重大影響。...

現場可編程門陣列 (FPGA) 是數字 IC(集成電路),使硬件設計工程師能夠根據他們的要求對定制的數字邏輯進行編程。術語“現場可編程”意味著IC的數字邏輯在其制造(或制作)期間不是固定的,而是由最終用戶(設計人員)編程。...

原先的時序報告: 根據時序報告中的路徑提示,在ILA的某個路徑上建立時間過長,而程序中并未例化ila的核,只是使用了chipscrop.。所以猜測是chipscrop部分的路徑時序不收斂。 于是去除了名為AD9739_dds的chipscrop,發現時序就滿足了。 證明時序是chipscrop中插入...

該項目基于AMD Xilinx Varium C1100 FPGA加速卡,為 Filecoin 區塊鏈應用中的Poseidon哈希算法提供了一套完整的硬件加速方案。...

定義一個函數指針,指向的函數有兩個int形參并且返回一個函數指針,返回的指針指向一個有一個int形參且返回int的函數?下面哪個是正確的?...

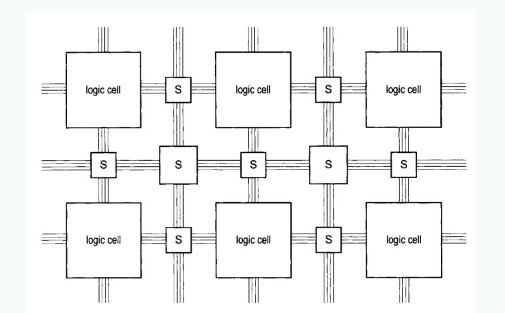

雖然現場可優化CPLD和FPGA都包含大量的可編程邏輯單元,但它們的系統結構存在很大的差別。與CPLD相比,FPGA的連接單元更多,雖然靈活卻也更加復雜;而CPLD的連接單元較少,延遲時間更加方便估計。...

首先,文章使用GPU最擅長處理的工作負載:通用矩陣乘(GEMM)來跑GPU的benchmark(什么是GEMM請移步https://spatial-lang.org/gemm),為了測量最佳的GPU性能,對每個器件使用最新的library,這些庫不會出錯,并且分別在使用和不使用張量核的情況下測試性能...

目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。...

完成上述步驟之后,就可以按照正常的BGA出線方式把所有的信號腳進行引出,并按照走線順序對接排列,但非連接上,如圖12-4所示,飛線是交叉的,但是不直接連上。最后保存好所有文檔。...

由時序圖可知初始化大概的過程為:上電后等待電源VDD和時鐘信號穩定100μs(期間命令為空命令),同時在100μs內設置CKE(時鐘使能)信號為高。隨后對所有Bank發送預充電(PRECH ARGE)命令,發送兩次自動刷新(REFRESH)命令,最后發送裝載模式寄存器(LOAD MODE REGIS...

FPGA(Field-ProgrammableGateArray),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。...

自己動手 (DIY) 制造商運動繼續發展,鼓勵硬件和軟件供應商在更高性能和更低成本方面相互跨越。他們還積極爭取社區參與,以添加更多軟件并擴大其關鍵的支持生態系統,作為回報,他們正在增強其核心產品,包括物聯網項目的無線連接。...

與雙極晶體管不同,在不同的晶片之間以及在不同的批次之間,MOSFETs 參數變化很 大。為了在一定程度上減輕電路設計任務的困難,工藝工程師們要保證器件的性能在某 個范圍內。...

FPGA可針對數據包步驟數量搭建同等數量流水線(流水線并行結構),數據包經多個流水線處理后可即時輸出。GPU數據并行模式依托不同數據單元處理不同數據包,數據單元需一致輸入、輸出。針對流式計算任務,FPGA流水線并行結構在延遲方面具備天然優勢。...

FPGA采用SRAM進行功能配置,可重復編程,但系統掉電后,SRAM中的數據丟失,因此,需要在FPGA外加EPROM,將配置數據寫入其中,系統每次上電自動將數據引入SRAM中。...

今天給大俠帶來基于FPGA的 模擬 I2C 協議設計,由于篇幅較長,分三篇。今天帶來第三篇,下篇,程序的仿真與測試。話不多說,上貨。...

FPGA收發器GTX/GTH參考時鐘接口提供兩種連接方式:LVDS(如圖1所示)和LVPECL(如圖2所示)。我們在選擇晶振時,至少要支持其中一種接口輸出電平標準。圖2所示的電阻值為一般推薦值,實際偏置電阻值需要參考晶振手冊。圖1和圖2中交流AC耦合電容作用:1)阻斷外部晶振和GTX/GTH收發器Q...