完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

共阻干擾是由PCB上大量的地線造成。當兩個或兩個以上的回路共用一段地線時,不同的回路電流在共用地線上產生一定壓降,此壓降經放大就會影響電路性能;當電流頻率很高時,會產生很大的感抗而使電路受到干擾。...

如果阻抗變化只發生一次,例如線寬從8mil變到6mil后,一直保持6mil寬度這種情況,要達到突變處信號反射噪聲不超過電壓擺幅的5%這一噪聲預算要求,阻抗變化必須小于10%。這有時很難做到,以 FR4板材上微帶線的情況為例,我們計算一下。如果線寬8mil,線條和參考平面之間的厚度為4mil,特性阻抗...

印制電路板是電子產品中電路元件和器件的支撐件,它提供電路元件和器件之間的電氣連接。為提高印制板的抗振、抗沖擊性能,板 上的負荷應合理分布以免產生過大的應力。對 大而重的元件(重量超過15g或體積超過27cm3) 盡可能布置在靠近固定端,并降低其重心或加 金屬結構件固定。...

電路原理圖的設計:電路原理圖的設計主要是PROTEL099的原理圖設計系統(AdvancedSchematic)來繪制一張電路原理圖。在這一過程中,要充分利用PROTEL99所提供的各種原理圖繪圖工具、各種編輯功能,來實現我們的目的,即得到一張正確、精美的電路原理圖。...

PCB表面一般涂有一層漆保護金屬,回收處理之前應先脫除漆。脫漆劑有有機脫漆劑和堿性脫漆劑,有機脫漆劑毒性大,對人體和環境危害大,堿性脫漆劑毒性相對較小。我們通過實驗得到脫漆最佳配方:將剪好的PCB小片放入10%氫氧化鈉溶液中。加入0.5%助劑A,0.5%助劑B,0.05%的緩蝕劑巰基苯并三氮唑,水浴...

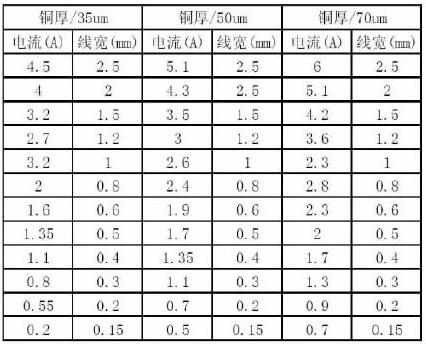

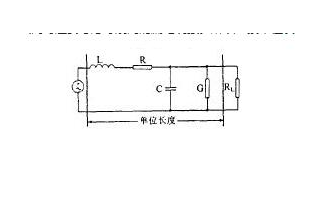

PCB上的印制導線通電后在直流或交流狀態下分別對電流呈現電阻或感抗,而平行導線之間存在電感效應,電阻效應,電導效應,互感效應;一根導線上的變化電流必然影響另一根導線,從而產生干擾;PCB板外連接導線甚至元器件引線都可能成為發射或接收干擾信號的天線。印制導線的直流電阻和交流阻抗可以通過公式和公式來計算...

高速數字電路設計方面的問題突出體現為以下類型:(1)工作頻率的提高和信號上升/下降時間的縮短,會使設計系統的時序裕量縮小甚至出現時序方面的問題;(2)傳輸線效應導致的信號震蕩、過沖和下沖都會對設計系統的故障容限、噪聲容限以及單調性造成很大的威脅;(3)信號沿時間下降到1ns以后,信號之間的串擾就成為...

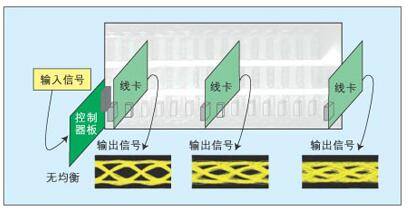

不斷部署的高帶寬業務逐漸逼近已有網絡和通信系統基礎設施的極限,推動了新系統的發展。在升級現有設備或設計新系統以獲得更高速鏈路時,背板互連的信號完整性是需要解決的一個基本問題,較集中的高速鏈路為背板互連、以及任何網絡或通信系統帶來了壓力。應用密集的高速鏈路引入了噪聲、串擾和信號劣化,當在跨背板或電纜環...

隨著工藝技術的發展,導致信號串擾的機會增加了。金屬布線層數持續增加:從0.35um工藝的4層或者5層增加到0.13um工藝中的超過7層金屬布線層。隨著布線層數的增加,相鄰的溝道電容也會增加。另外,目前復雜設計中的電路門數的劇增使得更多、更長的互連線成為必要。長線上的電阻會增加,而越來越細的金屬線同樣...

如果是人工焊接,要養成好的習慣,首先,焊接前要目視檢查一遍PCB板,并用萬用表檢查關鍵電路(特別是電源與地)是否短路;其次,每次焊接完一個芯片就用萬用表測一下電源和地是否短路;此外,焊接時不要亂甩烙鐵,如果把焊錫甩到芯片的焊腳上(特別是表貼元件),就不容易查到。...

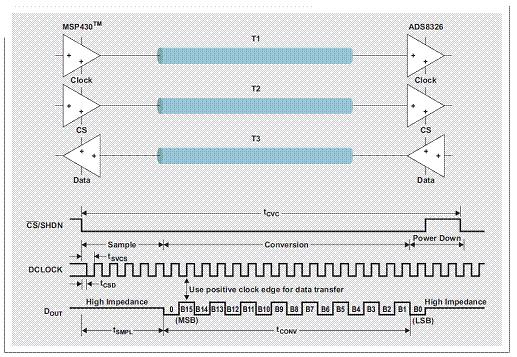

本文是關于在印刷電路板(PCB)開發階段使用數字輸入/輸出緩沖信息規范(IBIS)模擬模型的文章。本文將介紹如何使用一個IBIS模型來提取一些重要的變量,用于信號完整性計算和確定PCB設計解決方案。請注意,該提取值是IBIS模型不可或缺的組成部分。...

信號完整性(SignalIntegrity),是指信號未受到損傷的一種狀態。它表明信號通過信號線傳輸后仍保持其正確的功能特性,信號在電路中能以正確的時序和電壓作出響應,由IC的時序可知,如果信號在穩態時間(為了正確識別和處理數據,IC要求在時鐘邊沿前后輸入數據保持不變的時間段)內發生了較大的跳變,I...

本文所討論的工具包括:Allegro和SpecctraQuest、Hspice、Spicelink和HFSS:Allegro是目前通用的版圖設計工具;由于具備與Allegro相同的數據庫,SpecctraQuest被用做板級仿真的主要工具,避免了數據轉換的問題;Hspice是實現更精確分析的工具;S...

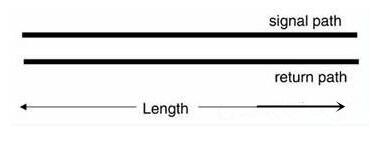

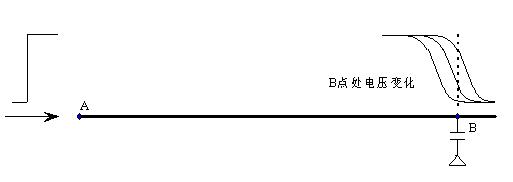

信號在這條走線上向前傳播,傳輸到走線盡頭需要10ns,返回到源端又需要10ns,則總的往返時間是20ns。如果把上面的信號往返路徑看成普通的電流回路的話,返回路徑上應該沒有電流,因為在遠端是開路的。但實際情況卻不是這樣,返回路徑在信號上后最初的一段時間有電流。...

信號沿傳輸線向前傳播時,每時每刻都會感受到一個瞬態阻抗,這個阻抗可能是傳輸線本身的,也可能是中途或末端其他元件的。對于信號來說,它不會區分到底是什么,信號所感受到的只有阻抗。如果信號感受到的阻抗是恒定的,那么他就會正常向前傳播,只要感受到的阻抗發生變化,不論是什么引起的(可能是中途遇到的電阻,電容,...

信號振鈴的過程可以用反彈圖來直觀的解釋。假設驅動端的輸出阻抗是10歐姆,PCB走線的特性阻抗為50歐姆(可以通過改變PCB走線寬度,PCB走線和內層參考平面間介質厚度來調整),為了分析方便,假設遠端開路,即遠端阻抗無窮大。驅動端傳輸3.3V電壓信號。我們跟著信號在這條傳輸線中跑一次,看看到底發生了什...

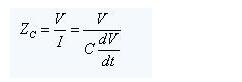

信號的接收端可能是集成芯片的一個引腳,也可能是其他元器件。不論接收端是什么,實際的器件的輸入端必然存在寄生電容,接受信號的芯片引腳和相鄰引腳之間有一定的寄生電容,和引腳相連的芯片內部的布線也會存在寄生電容,另外引腳和信號返回路徑之間也會存在寄生電容。...

首先按看一下對信號發射端的影響。當一個快速上升的階躍信號到達電容時,電容快速充電,充電電流和信號電壓上升快慢有關,充電電流公式為:I=C*dV/dt。電容量越大,充電電流越大,信號上升時間越快,dt越小,同樣使充電電流越大。...

信號布線在以前通常被看作是一種簡單的概念,從布線角度看,視頻信號、語音信號或數據信號之間沒有什么區別。因此過去很少有人關心信號布線問題。然而,現在情況有了完全的改變。視頻信號傳輸速度目前已經達到每個通道3.3Gbps,數據信號更是遠超過每通道5Gbps。...

信號完整性技術經過幾十年的發展,其理論和分析方法都已經較為成熟。對于信號完整性問題,信號完整性不是某個人的問題,它涉及到設計鏈的每一個環節,不但系統設計工程師、硬件工程師、PCB工程師要考慮,甚至在制造時也不能忽視。解決信號完整性問題,必須借助先進的仿真工具。...