本文轉(zhuǎn)自公眾號,歡迎關(guān)注

基于DWC2的USB驅(qū)動開發(fā)-USB連接詳解 (qq.com)

一.前言

之前一直在閱讀手冊,規(guī)格書,練習招式,學習心法,從這一篇開始我們就要真刀實槍的干了,當然不是一味蠻干。驅(qū)動編寫,調(diào)試,實踐的過程會結(jié)合閱讀規(guī)格書,手冊,理論結(jié)合實踐,招式和心法要同步進行。

二.USB連接需要幾步?

進行USB連接需要幾步?我們參考把大象裝進冰箱需要幾步:第一步打開冰箱門,第二步把大象裝入冰箱,第三步關(guān)閉冰箱門,完成。USB連接同樣的簡單,第一步插上開發(fā)板USB接口到電腦,第二步電腦識別到USB設(shè)備,第三步恭喜你獲得一個黃色告警對話框!完美完成!也許很不幸,你沒有獲得黃色告警對話框,那么就是失敗了,后面我們會詳細介紹怎么去分析調(diào)試。

三.USB連接原理

前面我們已經(jīng)完成了USB連接的操作,實踐了師傅教的第一招黑虎掏心,but what?我干了什么?前面我們說過需要理論結(jié)合實踐,招式結(jié)合心法,招式已經(jīng)嘗試了,但是到底是什么原理呢?到底是怎么做到的呢?那么就要從心法去探究,USB江湖的最基礎(chǔ)的心法,就是USB2.0的規(guī)格書。當然招式也有招式的拳譜劍譜,我們這里就對應(yīng)的使用的USB控制器IP的規(guī)格書(這里是新思的DDC2)和PHY的規(guī)格書(microChip的USB334x)。

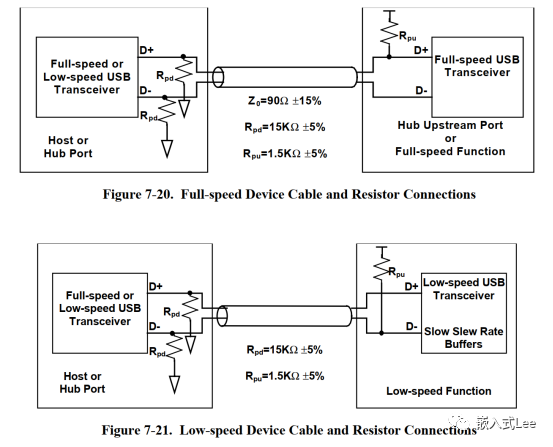

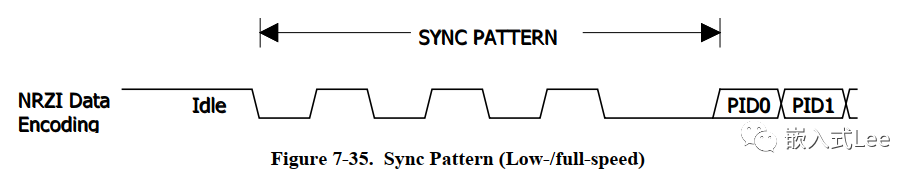

我們打開USB2.0規(guī)格書,翻到141頁看到如下圖,主機(或HUB)端D+和D-均由Rpd=15KΩ的電阻下拉,未接入設(shè)備時此時D+和D-都是0V。設(shè)備(或者下級HUB)端通過D+或D-上拉Rpu=1.5KΩ來區(qū)分是全速還是低速設(shè)備,全速設(shè)備D+上拉,低速設(shè)備D-上拉。設(shè)備端的上拉電阻和主機端下拉電阻分壓得到和未接設(shè)備時不一樣的電平,主機檢測該電平即可知道有設(shè)備插入,原理就是這么簡單,牛逼的武功也往往是很簡單,比如六脈神劍也就那么一彈手指。

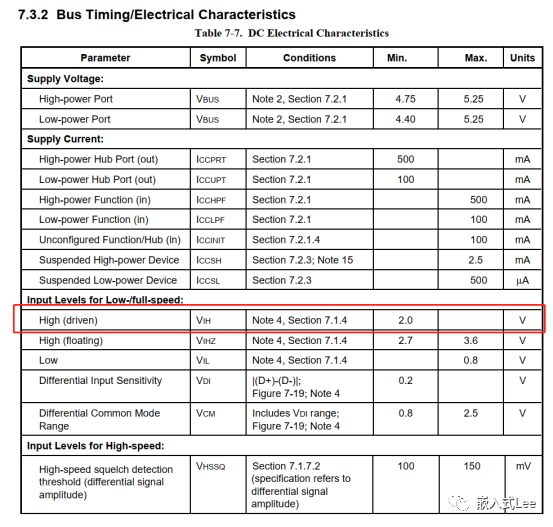

為什么是上拉1.5K呢,因為上拉電阻要保證分壓值不小于VIH(min),因為只有滿足該條件才能被識別為高,為什么這個電壓能識別為高呢,那就是硬件電氣特性決定的了,我喜歡死纏爛打的追問的伙伴,可以繼續(xù)深挖到收發(fā)器,晶體管,半導體.... ,如果能追到這一層的那么肯定是孤獨求敗級別的高手了,膜拜之。VIH在規(guī)格書中的要求如下至少要為2V(可以規(guī)格書中搜索找到)

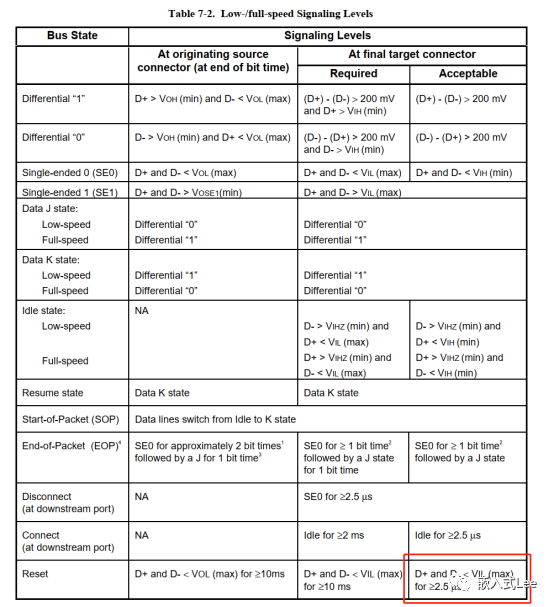

除了上述要求,上拉電阻還要保證能夠在2.5μs的最小復位時間內(nèi)將D+或D-從0V上拉至VIH(min),因為在復位結(jié)束時要進行總線狀態(tài)評估。

2.5uS的要求在如下表格中說明,即復位最短時間是2.5uS.

綜上要求,具有可拆卸電纜的設(shè)備使用1.5 k? ±5%電阻器連接到3.0 V和3.6 V之間的電壓源(VTERM),以滿足這些要求。帶有固定電纜的設(shè)備可以使用替代端接方式。但是,任何終端的Thevenin(戴維寧)電阻必須不小于900?.注:終端的Thevenin(戴維寧)電阻不包括主機/集線器上的15 k±5%的電阻。

上拉電阻器上的電壓源必須來源于USB電纜上提供的電源或由USB電纜上的電源控制,以便在移除VBUS時,上拉電阻器不會在其連接的數(shù)據(jù)線上提供電流。即VBUS斷開時上拉也應(yīng)該斷開。

上述表中描述的是針對低速和高速設(shè)備連接檢測,高速呢,高速設(shè)備的連接檢測和全速一樣,只是后面速度枚舉有不同,這個先按下不表,后面再講解。

四.USB連接驅(qū)動

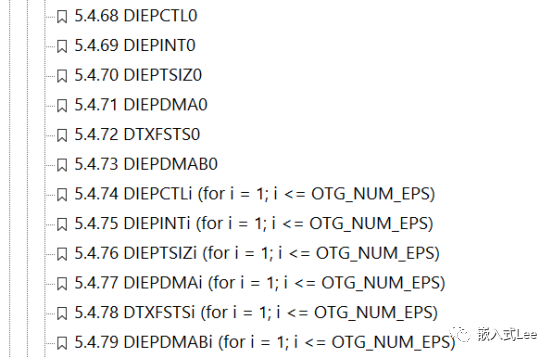

驅(qū)動編寫我們參考控制器IP的手冊,找到如下寄存器

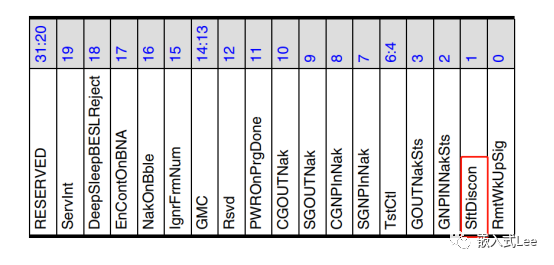

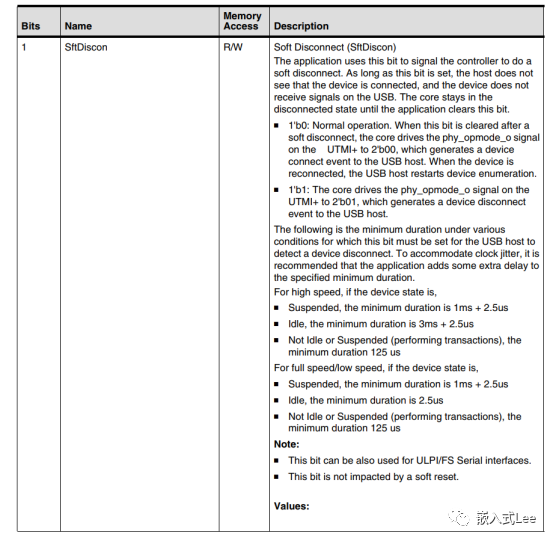

手冊P529的5.4.48 DCTL,Offset: 0x804,bit1

可以看到默認值是1,即默認是斷開上拉電阻的,注意這里的邏輯,這個bit表示斷開連接。

軟件寫0上拉電阻,這樣在DP或者DM上上拉電阻(根據(jù)速度而定,如何設(shè)置速度枚舉速度后面再講),這樣主機就可以檢測到了。

注意軟件操作這個bit時不要過于頻繁,一般留個10mS以上充足的間隔時間,大于上述手冊中的描述時間。

注意該位不受控制器軟件復位影響。

我們的驅(qū)動代碼如下,寄存器的操作封裝,參考之前的文章,為什么用宏不用結(jié)構(gòu)體,也有專門的文章講解,可以去瞅瞅。

static void usb_dev_crtl_sft_discon(uint8_t dis)

{

if (dis) {

REG_OTG_DCTL |= DCTL_SOFT_DISCONN;

} else {

REG_OTG_DCTL &= ~(DCTL_SOFT_DISCONN);

}

}

我們之前一直強調(diào),要了解根本原理,不管學習招式還是學習心法,一定要追其核心根本原理。那么這個bit寫0就能上拉,到底是怎么實現(xiàn)的呢,

我們這里操作的是控制器即LINK,但是實際工作是由PHY去完成的,所以寫了這個bit之后,

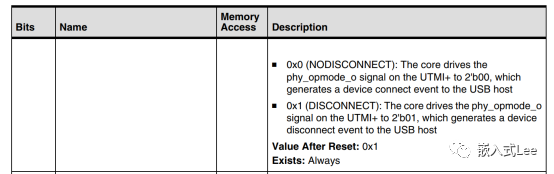

LINK會通過PHY和LINK之間的UTMI或者ULPI接口告訴PHY,最終由PHY去完成這個上拉工作。于是乎我們?nèi)シ哖HY的手冊這里是USB334x,看到如下圖,正是PHY將如下上拉電阻拉高來實現(xiàn)連接,至此我們已經(jīng)了解了整個過程。

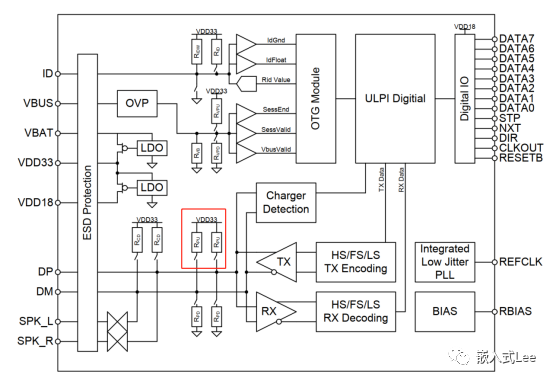

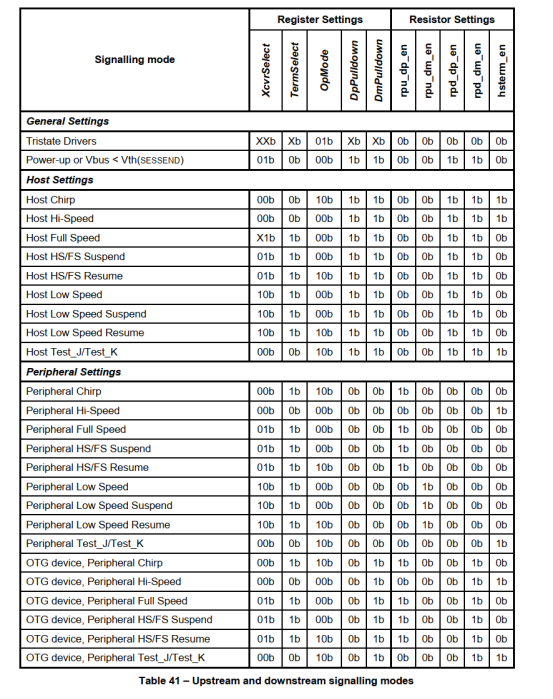

從ULPI的規(guī)格書中還可以看到實際是通過PHY對應(yīng)的寄存器相關(guān)位配置為不同的模式來控制的

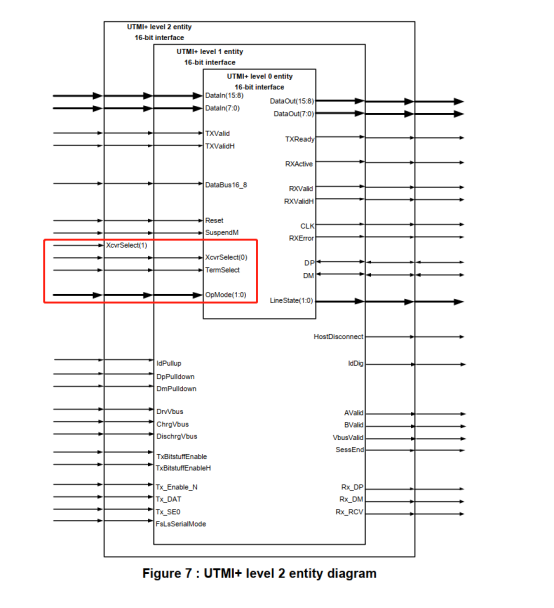

而UTMI接口中直接對應(yīng)的是信號線

這里順便提一下,ULPI對UTMI引腳的縮減,實際就是通過將一些信號線直接控制轉(zhuǎn)為寄存器控制來達到的。

但是有好問者,會問那么LINK是怎么告訴PHY要去上拉電阻的呢,問得很好,高手總是從刨根問底開始的。這個就要了解UTMI和ULPI協(xié)議了,可以參考本系列文章,講解了ULPI協(xié)議,甚至講解了如何使用邏輯分析儀抓包ULPI,那么你就可以抓到ULPI接口上具體的數(shù)據(jù),來調(diào)試分析了,比如最終沒能上拉,通過ULPI抓包可以確定是沒有發(fā)送到PHY還是PHY沒有執(zhí)行,進一步縮小范圍。

https://mp.weixin.qq.com/s/e4MCpASUXW4oKzfYOdMRwg

https://mp.weixin.qq.com/s/7oTIgxvrui_ZdjCktFo87g

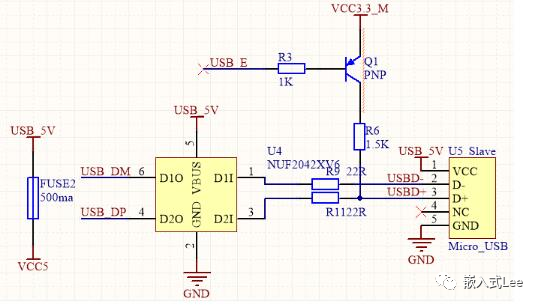

還有更細致的會問,那么這個上拉電阻是所有芯片都會有嗎,答案是否,有些芯片是沒有的,比如一些STM32的MCU,這個時候需要外部提供上拉電路,使用IO控制。如下(網(wǎng)上隨便找的一張圖),USB_E來控制上拉。

五.調(diào)試

上面我們?nèi)绻芸吹诫娔X彈出黃色告警的對話框,恭喜你,你已經(jīng)練就了第一招黑虎掏心。如果不幸沒有彈出呢,那么我們就需要進行調(diào)試。那么就要派出示波器出來一展身手了。

我們直接使用示波器監(jiān)控DP和DM的電平,查看初始是否都為0,然后connect后DP,DM是否對應(yīng)的拉高,拉高的值是否符合要求達到了VIH(min)。如果沒有拉高則從以下方面去分析:

1.硬件檢查,使用萬用表測量DP DM到芯片的相應(yīng)引腳是否聯(lián)通,測試DP,DM是否和地或者VCC短路。如果外置PHY則檢查PHY是否工作,通過時鐘等關(guān)鍵引腳判斷。

2.將DP DM配置為普通IO,翻轉(zhuǎn)IO使用示波器查看硬件連通性。強調(diào)下該方式是嵌入式一種常用的測試方法,用于確認IO到硬件上是否正常聯(lián)通,有時還可以使用IO做時序分析測試,即在一定的事件發(fā)生時翻轉(zhuǎn)IO,用示波器測量,這比使用軟件定時器和串口打印更精確。多個通道還可以可視化展現(xiàn)相位關(guān)系,簡單的一招確是調(diào)試的大招。

3.檢查DP DM是否按照芯片手冊配置為了對應(yīng)的功能,包括輸入輸出模式,功能選擇等,有些芯片可能需要重映射。

4.檢查USB相關(guān)的初始化是否正確,包括時鐘使能,IO模塊使能,外設(shè)模塊使能,時鐘配置(比如48M時鐘源等),檢查模塊復位,模塊寄存器保護等。回讀寄存器確認相應(yīng)的寄存器是否確實配置成功,回讀總是必要的,可靠性編程中需要考慮,寫入不一定成功的,芯片也是有出錯概率的。

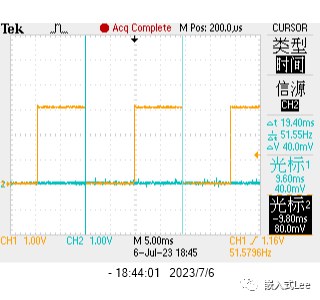

我這里針對DWC的IP,測試代碼如下,10mS進行一次斷開和連接使用示波器查看

while(1)

{

usb_dev_crtl_sft_discon(0);

iot_timer_delay_ms(10);

usb_dev_crtl_sft_discon(1);

iot_timer_delay_ms(10);

}

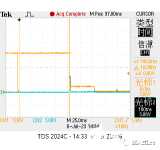

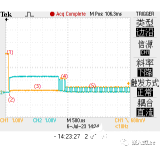

我這里是高速模式,示波器測試DP波形(黃色)如下:

六.總結(jié)

以上可以看出USB連接原理很簡單,就是一個上拉電阻,就好比將大象裝進冰箱一樣簡單。招式雖簡單,但是其背后的心法,原理確很重要,細節(jié)也很重要。這就是為什么喬峰使出黑虎掏心如此威力巨大,而一些綠林大漢使出來確平平無奇,這是心法和招式理解是否達到了爐火純晴的地步的區(qū)別。USB連接也是如此,只是知道上拉,還是知道LINK的寄存器如何配置,還是知道LINK和PHY如何通訊告訴PHY去上拉,甚至知道如何去抓包確認,還是知道上拉電阻為什么是1.5K有什么要滿足的條件,還是知道芯片不帶上拉如何去外置上拉等等,都是對應(yīng)不同的級別。看來一招USB連接,一招黑虎掏心也可以分為18級,只有練到最高級爐火純青才能所向披靡,遇BUG解BUG,遇fault殺fault。

審核編輯 黃宇

-

usb

+關(guān)注

關(guān)注

60文章

8139瀏覽量

270787 -

USB驅(qū)動

+關(guān)注

關(guān)注

1文章

138瀏覽量

20620 -

驅(qū)動開發(fā)

+關(guān)注

關(guān)注

0文章

133瀏覽量

12253 -

DWC2

+關(guān)注

關(guān)注

0文章

35瀏覽量

230

發(fā)布評論請先 登錄

基于DWC2的USB驅(qū)動開發(fā)-0x01開篇介紹與新思DWC2 USB2.0控制器簡介

基于DWC2的USB驅(qū)動開發(fā)-0x02 DWC2 USB2.0 IP功能特征介紹

基于DWC2的USB驅(qū)動開發(fā)-IAD描述符詳解

基于DWC2的USB驅(qū)動開發(fā)-USB復位詳解

基于DWC2的USB驅(qū)動開發(fā)-高速設(shè)備枚舉為全速設(shè)備問題案例分析

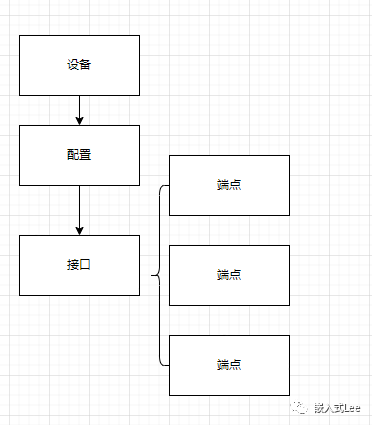

基于DWC2的USB驅(qū)動開發(fā)-設(shè)備類驅(qū)動框架

基于DWC2的USB驅(qū)動開發(fā)-發(fā)送相關(guān)的寄存器DMA寄存器詳解

基于DWC2的USB驅(qū)動開發(fā)-USB包詳解

基于DWC2的USB驅(qū)動開發(fā)-數(shù)據(jù)不能發(fā)送問題分析案例

新思 DWC2 的參考手冊從哪里可以下載

RK3399平臺上USB控制器和PHY的連接方式和配置說明

如何對基于hal庫的DWC2 USB IP進行調(diào)試呢

無法讓USB主機正常工作是我做錯了什么嗎?

基于DWC2的USB驅(qū)動開發(fā)-高速設(shè)備速度握手詳解

基于DWC2的USB驅(qū)動開發(fā)-抽絲剝繭再論切換到狀態(tài)階段標志DOEPINTn.StsPhseRcvd

基于DWC2的USB驅(qū)動開發(fā)-USB連接詳解

基于DWC2的USB驅(qū)動開發(fā)-USB連接詳解

評論