完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 先進(jìn)封裝

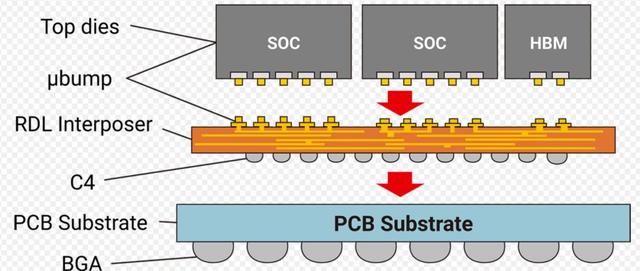

先進(jìn)封裝可以提高加工效率,提高設(shè)計(jì)效率,減少設(shè)計(jì)成本,降低芯片尺寸等優(yōu)勢(shì)。半導(dǎo)體器件有許多封裝形式,半導(dǎo)體封裝經(jīng)歷了多次重大革新,芯片級(jí)封裝、系統(tǒng)級(jí)封裝技術(shù)指標(biāo)一代比一代先進(jìn)。現(xiàn)在涌現(xiàn)了倒裝類(FlipChip,Bumping),晶圓級(jí)封裝(WLCSP,F(xiàn)OWLP,PLP),2.5D封裝等。

文章:466個(gè) 瀏覽:616次 帖子:0個(gè)

推動(dòng)AI高性能計(jì)算的先進(jìn)封裝解決方案

在半導(dǎo)體前段制程微縮日趨減緩后,異質(zhì)整合先進(jìn)封裝技術(shù)已然成為另一個(gè)實(shí)現(xiàn)功能整合與元件尺寸微縮的重要技術(shù)發(fā)展潮流。伴隨著人工智能物聯(lián)網(wǎng) (AI-centr...

2023-12-19 標(biāo)簽:芯片半導(dǎo)體封裝設(shè)計(jì) 1376 0

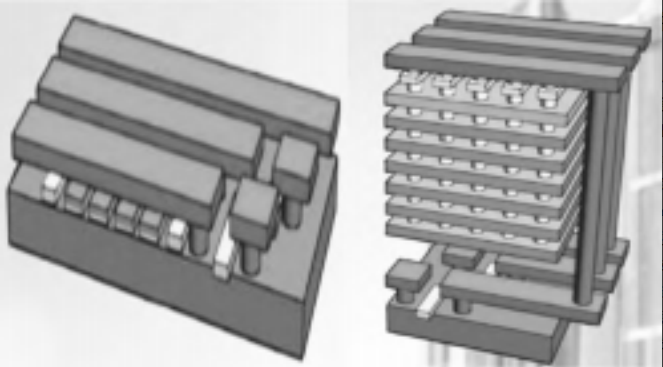

先進(jìn)封裝形式及其在三維閃存封裝中的可能應(yīng)用

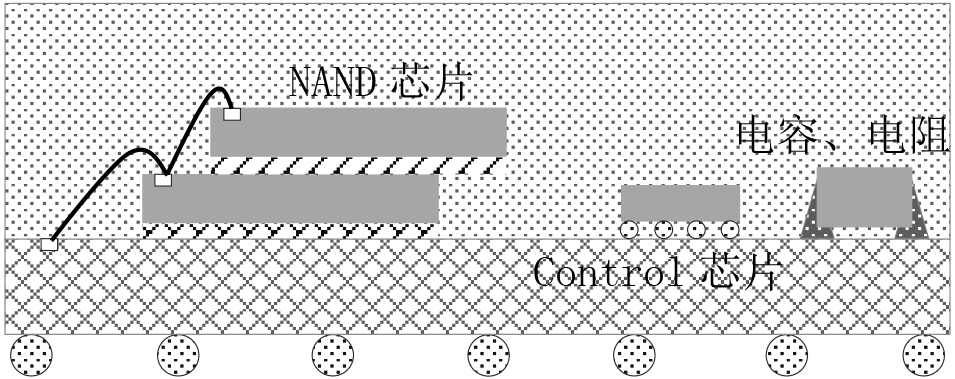

SiP 是將不同功能的芯片(例如存儲(chǔ)器、處理器無(wú)源器件等)封裝在同一個(gè)塑封體中,以此來實(shí)現(xiàn)一個(gè)完整功能的封裝形式4.具有高集成、低功耗、良好的抗機(jī)械和化...

先進(jìn)封裝技術(shù)在三維閃存中的應(yīng)用

近年來,隨著人工智能、物聯(lián)網(wǎng)和 5G 等技術(shù)的蓬勃發(fā)展和應(yīng)用,市場(chǎng)對(duì)數(shù)據(jù)處理以及存儲(chǔ)的需求逐漸增大。根據(jù) IDC 預(yù)測(cè),全球數(shù)據(jù)圈每年被創(chuàng)建、采集或復(fù)制...

隨著摩爾定律逐步達(dá)到極限,大量行業(yè)巨頭暫停了 7 nm 以下工藝的研發(fā),轉(zhuǎn)而將目光投向先進(jìn)封裝領(lǐng)域。其中再布線先行( RDL-first ) 工藝作為先...

半導(dǎo)體芯片封裝的目的無(wú)非是要起到對(duì)芯片本身的保護(hù)作用和實(shí)現(xiàn)芯片之間的信號(hào)互聯(lián)。在過去的很長(zhǎng)時(shí)間段里,芯片性能的提升主要是依靠設(shè)計(jì)以及制造工藝的提升。

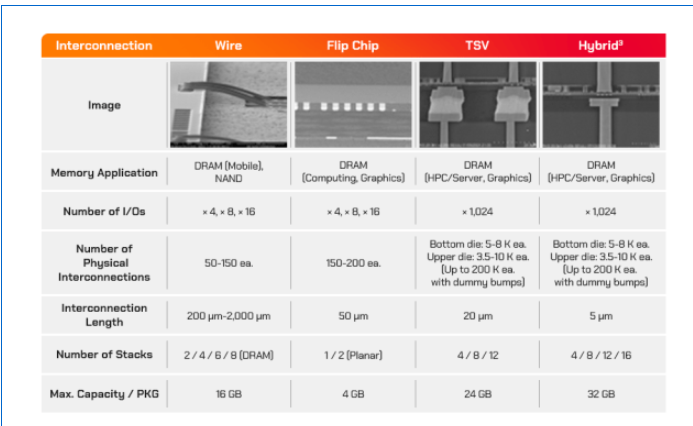

互連技術(shù)是封裝的關(guān)鍵和必要部分。芯片通過封裝互連,以接收功率、交換信號(hào)并最終進(jìn)行操作。由于半導(dǎo)體產(chǎn)品的速度、密度和功能隨互連方式的不同而不同,互連方法也...

HRP晶圓級(jí)先進(jìn)封裝替代傳統(tǒng)封裝技術(shù)研究(HRP晶圓級(jí)先進(jìn)封裝芯片)

隨著晶圓級(jí)封裝技術(shù)的不斷提升,眾多芯片設(shè)計(jì)及封測(cè)公司開始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝。其中HRP(Heat?Re-distribution?...

數(shù)據(jù)中心處理器采用Chiplet有何優(yōu)勢(shì)?

生成式人工智能和大模型的驅(qū)動(dòng)下,我們正置身于一個(gè)算力領(lǐng)域千載難逢的拐點(diǎn):一個(gè)類似于個(gè)人電腦、互聯(lián)網(wǎng)、移動(dòng)設(shè)備和云誕生的時(shí)刻。

在設(shè)計(jì)過程的早期階段,需要參與系統(tǒng)和封裝的分析,將設(shè)計(jì)劃分為各種芯片片段,并評(píng)估在計(jì)算、數(shù)據(jù)傳輸和制造成本方面的必要權(quán)衡。設(shè)計(jì)和驗(yàn)證工具(例如Syste...

2023-11-03 標(biāo)簽:數(shù)據(jù)傳輸人工智能封裝系統(tǒng) 703 0

先進(jìn)封裝技術(shù)如何助力實(shí)現(xiàn)工業(yè)4.0?

工業(yè) 4.0 工廠幾乎在每個(gè)制造過程中都將電子控制和監(jiān)控與有線或無(wú)線連接相結(jié)合。在多數(shù)情況下,需要將電子模塊安裝到狹小空間內(nèi),而這些空間最初并非出于容納...

什么是先進(jìn)封裝?先進(jìn)封裝技術(shù)包括哪些技術(shù)

半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip),凸塊(Bu...

先進(jìn)封裝技術(shù)中最常見的10個(gè)術(shù)語(yǔ)介紹

將大型SoC分解為較小的小芯片,與單顆裸晶相比具有更高的良率和更低的成本。Chiplet使設(shè)計(jì)人員可以充分利用各種IP,而不用考慮采用何種工藝節(jié)點(diǎn),以及...

先進(jìn)封裝技術(shù)以SiP、WLP、2.5D/3D為三大發(fā)展重點(diǎn)。先進(jìn)封裝核心技術(shù)包括Bumping凸點(diǎn)、RDL重布線、硅中介層和TSV通孔等,依托這些技術(shù)的...

2023-09-28 標(biāo)簽:晶圓芯片設(shè)計(jì)SiP技術(shù) 4200 0

彎道超車的Chiplet與先進(jìn)封裝有什么關(guān)聯(lián)呢?

Chiplet也稱芯粒,通俗來說Chiplet模式是在摩爾定律趨緩下的半導(dǎo)體工藝發(fā)展方向之一,是將不同功能芯片裸片的拼搭

有機(jī)基板的材料主要由類似 PCB 的材料和編織玻璃層壓板制成,允許通過芯片路由相當(dāng)多的信號(hào),包括基本的小芯片設(shè)計(jì),例如英特爾的移動(dòng)處理器(具有單獨(dú)的 P...

傳統(tǒng)封裝 Vs.先進(jìn)封裝的區(qū)別及優(yōu)勢(shì)

集成電路封裝是指將制備合格芯片、元件等裝配到載體上,采用適當(dāng)連接技術(shù)形成電氣連接,安裝外殼,構(gòu)成有效組件的整個(gè)過程,封裝主要起著安放、固定、密封、保護(hù)芯...

先進(jìn)封裝增速高于整體封裝,將成為全球封裝市場(chǎng)主要增量。根據(jù)Yole的數(shù)據(jù),全球封裝市場(chǎng)規(guī)模穩(wěn)步增長(zhǎng),2021 年全球封裝 市場(chǎng)規(guī)模 約達(dá) 777 億美元...

2023年以來,AIGC迅速發(fā)展,帶動(dòng)AI芯片與AI服務(wù)器熱潮,而由臺(tái)積電推出、被稱為CoWoS的2.5D先進(jìn)封裝技術(shù)更是扮演關(guān)鍵角色。然而,突如其來的...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |