電子發(fā)燒友網(wǎng)核心提示:本文為玩轉(zhuǎn)賽靈思Zedboard開發(fā)板(3):基于Zynq PL的流水燈,內(nèi)容精彩,敬請(qǐng)對(duì)電子發(fā)燒友網(wǎng)保持密切關(guān)注。基于Zynq PL的流水燈是使用PL做流水燈實(shí)驗(yàn),目的是為

2012-12-05 14:25:41 12770

12770 電子發(fā)燒友網(wǎng)核心提示 :本文介紹了最新的Xilinx Zynq-7000 FPGA開發(fā)板 Zedboard 。Zedboard是基于Xilinx Zynq-7000擴(kuò)展式處理平臺(tái)(EPP)的低成本開發(fā)板,也是行業(yè)首個(gè)面向開源社區(qū)的Zynq-7000擴(kuò)展

2012-11-26 15:09:01 55135

55135 。AXI4-Lite接口的特性如下: 1) 突發(fā)長度為1。 2) 所有訪問數(shù)據(jù)的寬度和數(shù)據(jù)總線寬度相同。 3) 支持?jǐn)?shù)據(jù)總線寬度為32位或64位。 4) 所有的訪問相當(dāng)于AWCACHE和ARCACHE

2020-09-27 11:33:02 8051

8051

FPGA+ARM是ZYNQ的特點(diǎn),那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個(gè)實(shí)驗(yàn)是創(chuàng)建一個(gè)基于AXI總線的GPIO IP,利用PL的資源來擴(kuò)充GPIO資源。通過這個(gè)實(shí)驗(yàn)迅速入門開發(fā)

2020-12-25 14:07:02 2957

2957

電子發(fā)燒友網(wǎng)核心提示 : ZedBoard開發(fā)板 上的Zynq是一個(gè)ARM PS(processing system, 雙核A9 + 存儲(chǔ)管理 + 外設(shè))+ PL(programable Logic) 結(jié)構(gòu),如果不使用PL,zynq的開發(fā)和普通的ARM 開發(fā)一樣。不同

2012-11-26 15:49:47 14399

14399 電子發(fā)燒友網(wǎng)編輯現(xiàn)為讀者整合《玩轉(zhuǎn)賽靈思Zedboard開發(fā)板》系列文章, 其中包括在ZedBoard開發(fā)板上的一些應(yīng)用實(shí)例。本文主要講述Zedboard上的嵌入式linux應(yīng)用,包括使用SDK設(shè)計(jì)最簡單的linux應(yīng)用程序、linux交叉編譯環(huán)境搭建、設(shè)備驅(qū)動(dòng)編寫等內(nèi)容...

2013-01-24 13:38:18 16892

16892 ( - 用戶在此處添加端口 - 用戶端口結(jié)束 - 請(qǐng)勿修改此行之外的端口 - Axi從設(shè)備總線接口S00_AXIS的端口s00_axis_aclk:在std_logic中;s00_axis_aresetn:在

2020-08-20 13:59:52

PL端的編寫和使用,接下來是PS端的介紹AXI_Lite總線使用方法(上)pl端讀寫B(tài)RAM一、總覽如圖,main函數(shù)實(shí)現(xiàn)的功能主要是初始化中斷,中斷來自WRRD模塊發(fā)送數(shù)據(jù)完畢,中斷觸發(fā)為上升沿。具體功能往下看。我們首先來看#define。不知道還有沒有記得..

2022-01-10 08:00:55

電子發(fā)燒友網(wǎng)訊:由賽靈思(xilinx)公司和華強(qiáng)PCB網(wǎng)贊助,電子發(fā)燒友網(wǎng)主辦的玩轉(zhuǎn)FPGA,賽靈思設(shè)計(jì)大賽已經(jīng)圓滿結(jié)束。本活動(dòng)旨在建立一個(gè)FPGA技能展示和技術(shù)交流平臺(tái),鼓勵(lì)廣大參賽者發(fā)揮

2012-09-06 11:52:48

Spartan-6開發(fā)板 二等獎(jiǎng)獎(jiǎng)品: Xilinx Spartan-6開發(fā)板 三等獎(jiǎng)獎(jiǎng)品: 電子發(fā)燒友T恤+賽靈思小禮品 大賽獲獎(jiǎng)名單 一等獎(jiǎng) 姚佳毅(yjysdu)——車牌

2012-09-06 11:54:16

與技術(shù)學(xué)院教授史治國:浙江大學(xué)信息與電子工程學(xué)系副教授徐文波:畢業(yè)于北京郵電大學(xué)碩士研究生,F(xiàn)PGA圖書作者活動(dòng)獎(jiǎng)品一等獎(jiǎng)二等獎(jiǎng)三等獎(jiǎng)幸運(yùn)獎(jiǎng)1名5名10名若干iPad2+Xilins Spartan-6開發(fā)板Xilins Spartan-6開發(fā)板電子發(fā)燒友T恤賽靈思官方期刊雜志`

2012-04-23 09:31:16

)二等獎(jiǎng):Xilinx Spartan-6開發(fā)板(5名)三等獎(jiǎng):電子發(fā)燒友T恤(10名)小獎(jiǎng)品:賽靈思官方期刊雜志【活動(dòng)時(shí)間及流程】4月23日—7月31日?qǐng)?bào)名階段:4月23日至7月20日期間,參賽者報(bào)名

2012-04-24 14:40:58

經(jīng)過準(zhǔn)備,"玩轉(zhuǎn)FPGA,賽靈思超值開發(fā)板等你拿"設(shè)計(jì)大賽正式上線,現(xiàn)已開始接受報(bào)名.報(bào)名地址:http://www.asorrir.com/activities/fpga/

2012-04-23 15:31:01

LZAedkCwQtllAEyw提取碼:ld9cFPGA軟件無線電開發(fā)(全階視頻教程+開發(fā)板+實(shí)例)詳情鏈接:http://url.elecfans.com/u/5e4a12f2ba`

2019-11-12 10:23:42

芯片可以做到了最優(yōu)狀態(tài)。因此,對(duì)于用Zynq做開發(fā)的工程師而言,如何玩轉(zhuǎn)AXI HP總線就成為了必修課。本實(shí)例(zstar_ex56)通過一個(gè)簡單的AXIHP總線主機(jī)的讀時(shí)序和寫時(shí)序邏輯,來帶領(lǐng)讀者掌握

2019-11-26 09:47:20

無線電開發(fā)(全階視頻教程+開發(fā)板+實(shí)例)詳情鏈接:http://url.elecfans.com/u/5e4a12f2ba`

2019-11-28 10:11:38

`玩轉(zhuǎn)Zynq連載3——AXI總線協(xié)議介紹1 更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s 1 AXI協(xié)議簡介AMBA AXI(Advanced

2019-05-06 16:55:32

。ROHM與安富利公司共同開發(fā)賽靈思7系列FPGA及Zynq?–7000 All Programmable SoC的評(píng)估套件Mini-Module Plus 用的電源模塊。安富利公司已經(jīng)開發(fā)出多款賽靈思

2018-12-04 10:02:08

`賽靈思FPGA原理圖例子之s3astarter 賽靈思一向是FPGA領(lǐng)域里的領(lǐng)先者,運(yùn)用FPGA需要深入的理解它的工作原理,小編親子整理了s3astarter 的經(jīng)典fpga原理圖分享給電子工程師們。賽靈思FPGA原理圖例子之s3astarter [hide][/hide]`

2012-03-16 10:41:19

賽靈思公司(Xilinx)日前宣布NEC子公司NEC Display Solutions有限公司的三款DLP數(shù)字影院投影儀產(chǎn)品,均采用了賽靈思Virtex?-5 FPGA系列產(chǎn)品。

2019-08-19 07:12:03

賽靈思Spartan開發(fā)板使用困境記錄原理圖和接口主要是對(duì)照核心板的原理圖,一般的接法就是賽靈思系列的單片機(jī),連接好電源和下載器,記得預(yù)先安好驅(qū)動(dòng),驅(qū)動(dòng)安裝成功與否能夠在設(shè)備管理器處查看。作者困境

2021-07-13 08:42:10

賽靈思Verilog(FPGACPLD)設(shè)計(jì)小技巧

2012-08-19 22:52:02

尊敬的賽靈思客戶朋友們:在此,我謹(jǐn)代表賽靈思公司與您分享一個(gè)激動(dòng)人心的喜訊: 3 月1 日,賽靈思公司宣布全球第一片28nmFPGA 芯片(7K325T) 成功量產(chǎn)了!該里程碑式信息的發(fā)布,不僅是賽

2012-03-22 15:17:12

賽靈思有哪幾種ISE設(shè)計(jì)套件配置版本 ?

2021-04-30 06:30:50

最近在用賽靈思的DDR3,用的AXi4接口,我寫入的地址是按照突發(fā)長度來的,連續(xù)給8個(gè)讀的地址,但是在DDR3端,dq_addr 一直在1418,1000,1010,0003,0002 等幾個(gè)地址中

2016-06-24 10:38:18

賽靈思的FPGA用什么開發(fā)工具編程,有沒有大佬分享一下安裝包

2018-05-24 17:51:38

賽靈思(XILINX)全新7系列FPGA詳述

2012-08-14 12:20:22

FPGA是用altera多還是賽靈思的多呢,我買的開發(fā)板是altera的,但是很多人推薦說學(xué)習(xí)賽靈思的好

2016-01-09 21:27:25

`FPGA設(shè)計(jì)大賽獎(jiǎng)品.蘋果iPad2+賽靈思Xilinx Spartan-6開發(fā)板 等你拿,FPGA發(fā)燒友、工程師們,心動(dòng)了么,那就趕快猛戳這里報(bào)名吧一等獎(jiǎng)獎(jiǎng)品:iPad2+Xilinx

2012-04-25 09:32:46

N32G430C8L7_STB開發(fā)板用于32位MCU N32G430C8L7的開發(fā)

2023-03-31 12:05:12

賽靈思 EGO1 口袋實(shí)驗(yàn)開發(fā)板-全套包括:開發(fā)板使用手冊(cè)、及配置實(shí)驗(yàn)共8個(gè),都有原碼和公司每個(gè)實(shí)驗(yàn)指導(dǎo)書的pdf 還包括:EGO1板卡文件、引腳約束文件、及硬件手冊(cè)。

2018-10-05 22:22:18

` 本帖最后由 MGJOY 于 2017-4-10 15:07 編輯

本周三,4月12日,賽靈思FPGA技術(shù)及應(yīng)用線上公開課。歡迎大家觀看、學(xué)習(xí)交流~分享主題【賽靈思FPGA人工智能領(lǐng)域技術(shù)及應(yīng)用】嵌入式視覺領(lǐng)域技術(shù)和解決方案機(jī)器學(xué)習(xí)方面的技術(shù)和解決方案ADAS/自動(dòng)駕駛方面的應(yīng)用`

2017-04-10 15:06:16

能做賽靈思方案的,請(qǐng)聯(lián)系

2019-01-21 19:31:40

圖如下:需要強(qiáng)調(diào)的是,AXI的五個(gè)通道,每個(gè)通道都有握手機(jī)制,接下來我們就來分析一下AXI-Lite的源碼來更深入的了解AXI機(jī)制。突發(fā)式讀當(dāng)?shù)刂烦霈F(xiàn)在地址總線后,傳輸?shù)臄?shù)據(jù)將出現(xiàn)在讀數(shù)據(jù)通道上。設(shè)備

2018-01-08 15:44:39

`{:4_122:}{:4_122:}搶樓啦!!“賽靈思”搶樓活動(dòng)第二輪中獎(jiǎng)樓層公布號(hào)外號(hào)外{:4_104:}:為了答謝各位壇友們的大力支持,我和我的小伙伴們決定在增加5個(gè)中獎(jiǎng)樓層,讓各位中獎(jiǎng)的幾率

2013-10-11 10:40:34

小弟我是學(xué)習(xí)FPGA嵌入式的新手,最近在學(xué)習(xí)使用zedboard開發(fā)板,在研究zedboard_CTT_V14.4官方例程的時(shí)候,按照附錄的程序,一直報(bào)錯(cuò),表示添加的外設(shè)DEVICE_ID沒有定義

2015-04-22 20:54:49

系列,為用戶從端點(diǎn)到邊緣再到云端多種不同技術(shù)的快速創(chuàng)新提供支持。 Peng的戰(zhàn)略包括三大要點(diǎn): “數(shù)據(jù)中心加速”提為發(fā)展新重點(diǎn): 賽靈思正在加強(qiáng)與關(guān)鍵數(shù)據(jù)中心客戶、生態(tài)系統(tǒng)合作伙伴及軟件應(yīng)用開發(fā)

2018-03-23 14:31:40

PYNQ-Z2平臺(tái)完善該項(xiàng)目的開源設(shè)計(jì),并進(jìn)一步提升性能。項(xiàng)目計(jì)劃①根據(jù)文檔,對(duì)賽靈思PYNQ-Z2快速入門②通過學(xué)習(xí)賽靈思PYNQ-Z2的軟件和系統(tǒng),了解實(shí)際應(yīng)用案例,熟悉開發(fā)過程③基于賽靈思PYNQ-Z2

2019-01-09 14:49:25

` 非常感謝此次發(fā)燒友論壇和芯靈思舉辦的芯靈思開發(fā)板前樓活動(dòng),讓本人此次有機(jī)會(huì)體驗(yàn)SINA31s的開發(fā)板套件。快遞很給力,前天貼出快遞單號(hào)今天下午就收到了板子。越是迫不及待的打開欣賞了一番,現(xiàn)在

2015-11-06 01:00:03

感謝電子發(fā)燒友、感謝芯靈思這次獲得了芯靈思八核A83T開發(fā)板套件的試用機(jī)會(huì),昨天收到貨包裝非常精致,采用青色硬紙盒包裝(包含上下蓋),產(chǎn)品包裝正面右上角用白色中英文標(biāo)注了芯靈思的品牌標(biāo)示,左側(cè)

2017-05-01 14:20:17

折騰此類開發(fā)板,比如普中科技51單片機(jī)、威銳視Red 5 FPGA開發(fā)板等,閑話少說,直奔主題,很高興和大家分享這一期的芯靈思A83T開發(fā)套件試用體驗(yàn)。二、開箱體驗(yàn)昨天中午收到了這款難得芯靈思A83T

2017-04-30 17:46:23

本帖最后由 可樂丸子 于 2017-7-5 21:36 編輯

項(xiàng)目概述:芯靈思A83T開發(fā)板可以配合樹莓派、網(wǎng)絡(luò)攝像頭、USB攝像頭打造家庭網(wǎng)絡(luò)監(jiān)控,芯靈思A83T開發(fā)板可以作為家庭網(wǎng)絡(luò)監(jiān)控

2017-07-01 10:58:03

Altera和賽靈思20年來都在FPGA這個(gè)窄眾市場(chǎng)激烈的競(jìng)爭(zhēng)者,然而Peter Larson基于對(duì)兩個(gè)公司現(xiàn)金流折現(xiàn)法的研究表明,賽靈思是目前FPGA市場(chǎng)的絕對(duì)領(lǐng)先者。

2019-09-02 06:04:21

今年年初,賽靈思率先在FPGA領(lǐng)域提出目標(biāo)設(shè)計(jì)平臺(tái)概念,旨在通過選用開放的標(biāo)準(zhǔn)、通用的開發(fā)流程以及類似的設(shè)計(jì)環(huán)境,減少通用工作對(duì)設(shè)計(jì)人員時(shí)間的占用,確保他們能集中精力從事創(chuàng)新性的開發(fā)工作。

2019-08-13 07:27:15

賽靈思 MATLAB & Simulink Add-on插件是將 ModelComposer 和 System Generator forDSP完美結(jié)合的統(tǒng)一工具。

2021-01-28 06:33:40

大家好,我正在使用vivado 2014.4制作zc702板,我想使用axi lite ipif ip。首先我不能把它稱為IP,因?yàn)閂ivado找不到它,所以我直接使用vhdl文件到我的項(xiàng)目

2020-04-09 12:23:27

[]合成了內(nèi)存),輸出端口合成為ap_fifo,這意味著,由于AXi4Lite不支持fifo結(jié)構(gòu),因此只能使用AXI4Stream接口/總線從輸出端口result []讀取數(shù)據(jù)。我也是這個(gè)嵌入式總線和接口

2019-02-28 13:47:30

回收Xilinx帶板芯片, 回收工廠賽靈思XILINX系列IC:XC3S1500FGG676EGQ、XC5VLX50-1FFG676、XC5

2021-12-17 10:02:19

國外的融合技術(shù)專家展示了一項(xiàng)基于FPGA的數(shù)據(jù)采集系統(tǒng),用于合成孔徑成像技術(shù)。采用了Xilinx ISE設(shè)計(jì)軟件,支持ARM AMBA AXI4接口。文風(fēng)犀利,觀點(diǎn)新穎,F(xiàn)PGA中使用ARM及AMBA總線中不可多得的資料在賽靈思FPGA中使用ARM及AMBA總線[hide][/hide]

2012-03-01 15:48:17

基于賽靈思的FPGA的EtherCAT主站總線控制 ,論壇有做運(yùn)動(dòng)控制這方面的技術(shù)嗎?目前我已實(shí)現(xiàn)帶32軸同步運(yùn)行,同步抖動(dòng)±75ns,控制精度125us。感興趣的可以一起探討下

2018-07-23 12:00:39

和功能測(cè)試覆蓋了完整LTE協(xié)議棧及其應(yīng)用。射頻前端采用本地多輸入多輸出(MIMO)設(shè)計(jì),可支持5MHz、10MHz、15MHz和20MHz多種不同帶寬。 這個(gè)仿真器中心采用三個(gè)賽靈思Virtex?-5

2019-06-17 06:36:10

`Zing是一塊由北京威視銳公司推出的基于賽靈思可擴(kuò)展處理平臺(tái)架構(gòu)的高性能開發(fā)板。它使用了賽靈思最新推出的Zynq-7000系列芯片,它采用 28nm制程工藝,具有高性能、低功耗等特點(diǎn),其最主要

2020-10-21 14:32:12

FAST包處理器的核心功能是什么如何使用賽靈思FPGA加速包處理?

2021-04-30 06:32:20

全球可編程邏輯解決方案領(lǐng)導(dǎo)廠商賽靈思公司 (Xilinx Inc.) 宣布,為推進(jìn)可編程勢(shì)在必行之必然趨勢(shì),正對(duì)系統(tǒng)工程師在全球發(fā)布賽靈思新一代可編程FPGA平臺(tái)。和前代產(chǎn)品相比,全新的平臺(tái)功耗降低

2019-08-09 07:27:00

嗨,我開始使用Vivado了。我正在嘗試配置從Dram讀取數(shù)據(jù)的自定義IP,處理它們?nèi)缓髮⒔Y(jié)果發(fā)送到Bram控制器。我想過使用AXI主接口制作自定義IP。但是,我不知道將AXI主信號(hào)連接到我的自定義邏輯,以便我可以從Dram讀取數(shù)據(jù)并將結(jié)果發(fā)送到Bram。謝謝。

2020-05-14 06:41:47

怎么利用賽靈思FGPA實(shí)現(xiàn)降采樣FIR濾波器?這種濾波器在軟件無線電與數(shù)據(jù)采集類應(yīng)用中都很常見。

2019-08-15 08:21:22

“玩轉(zhuǎn)FPGA:iPad2,賽靈思開發(fā)板等你拿”活動(dòng)持續(xù)火爆進(jìn)行中……………………活動(dòng)得到了廣大電子工程師積極強(qiáng)烈的支持,為了回報(bào)電子工程師和網(wǎng)站會(huì)員,現(xiàn)在只需提交fpga設(shè)計(jì)方案,就有機(jī)會(huì)獲得賽靈

2012-07-06 17:24:41

嗨,我將通過測(cè)試驗(yàn)證這一點(diǎn),但我對(duì)AXI-Lite外設(shè)“寄存器寫入”如何出現(xiàn)在AXI-Lite總線上有疑問。AXI標(biāo)準(zhǔn)表明數(shù)據(jù)和地址可以非常相互獨(dú)立地出現(xiàn),從靈活性的角度來看這是很好的,但是

2019-04-12 13:45:01

了空洞位于球的BGA側(cè),而不是PCB側(cè)。從同一托盤檢查其他BGA設(shè)備顯示焊球有一些斑駁的外觀,沒有預(yù)期的光澤和光滑。有沒有類似的經(jīng)歷?結(jié)果是你的CM的流程問題了嗎?有沒有人從賽靈思獲得有缺陷的BGA?你們中有多少人做5DX排尿檢查?

2020-06-17 13:27:03

剛開始學(xué)賽靈思的FPGA,求他的ISE軟件下載地址,我在網(wǎng)上沒搜到。謝謝了

2012-08-02 09:52:12

請(qǐng)問各位大神,誰有賽靈思XC7V2000T這塊FPGA的開發(fā)板原理圖,求一份,多謝

2015-09-07 17:05:03

,ar)共用一組信號(hào)的接口(arw,w,b,r)。關(guān)于總線互聯(lián)的設(shè)計(jì)凡是設(shè)計(jì)中用到Axi4總線的設(shè)計(jì)總離不開總線互聯(lián)。在Xilinx FPGA使用中,VIvado針對(duì)Axi4總線提供了豐富的IP,對(duì)于

2022-08-02 14:28:46

` 本帖最后由 HelloWii 于 2015-9-9 11:52 編輯

買了一塊芯靈思開發(fā)板,這款板子總的來說是相當(dāng)不錯(cuò)的,性能穩(wěn)定,資源相當(dāng)豐富,而且還配有學(xué)習(xí)視頻,這些呢,是我自己通過學(xué)習(xí)

2015-09-09 11:38:25

芯靈思SinImx6ul開發(fā)板支持三種啟動(dòng)方式,分別是SD卡、 NandFLASH 、 USB下圖是啟動(dòng)模式選擇NXP Imx6ul芯片的特點(diǎn)是接口多,功耗低,A7處理器,全工業(yè)級(jí),性價(jià)比好。

2018-10-30 09:53:53

芯靈思SinlinxA33開發(fā)板 使用MIPI DSI屏幕我這里用的是從芯靈思買的mipi屏幕,其它型號(hào)屏幕也可以參考首先準(zhǔn)備好相關(guān)屏幕驅(qū)動(dòng)mb709_mipi.c將到mb709_mipi.c

2019-01-02 09:49:36

芯靈思的開發(fā)板子有用過的朋友嗎?這款板子怎么樣啊

2015-07-13 10:07:31

詳解賽靈思All Programmable Smarter Vision解決方案

2021-06-02 06:56:12

嗨,我在Vivado 2016.3模塊設(shè)計(jì)中集成了PCIe DMA BAR0 AXI Lite接口和AXI IIC IP。在DMA IP端,它顯示S_AXI_Lite端口,但在AXI_IIC IP端

2020-05-14 09:09:35

,永久,_0_0_0tri_mode_eth_macIP:Design_Linking常駐2017.04節(jié)點(diǎn)鎖定C:\賽靈思\ Vivado \ 2017.1 \ DATA \ IP

2020-08-21 11:07:27

絲印查不到系列型號(hào),引腳數(shù)量也對(duì)不上賽靈思所有型號(hào)規(guī)格,賽靈思也沒有韓國產(chǎn)地

2023-02-24 17:01:32

電子發(fā)燒友網(wǎng)訊:賽靈思FPGA 7系列芯片正以燎原之勢(shì)席卷整個(gè)行業(yè)。在本文,電子發(fā)燒友網(wǎng)小編將帶領(lǐng)大家一起走近Xilinx的FPGA 7系列芯片,從全新FPGA 7系列芯片的介紹、芯片優(yōu)點(diǎn)、芯片

2012-09-06 16:24:35

) 的靈活可編程 VESADisplayPort v.1.1a 解決方案。該 IP 可隨時(shí)提供給賽靈思的客戶,但在用戶展開設(shè)計(jì)之前,建議先了解與該標(biāo)準(zhǔn)的部分關(guān)鍵功能有關(guān)的其它背景信息,如olicy Maker

2012-03-01 11:10:18

高價(jià)回收

賽靈思系列IC長期回收

賽靈思系列IC,高價(jià)求購

賽靈思系列IC。深圳帝歐長期回收ic電子料,帝歐趙生***QQ1816233102/879821252郵箱

[email protected]。帝歐回收

2021-04-06 18:07:50

Spartan-6開發(fā)板 三等獎(jiǎng)獎(jiǎng)品: 電子發(fā)燒友網(wǎng)T恤+賽靈思小禮品 那接下來我們就展示一下獎(jiǎng)品陣容吧!先給大家看看我們的iPad 2吧。圖 一等獎(jiǎng)獎(jiǎng)品之iPad 2#p#賽靈思Spartan-6開發(fā)板

2012-09-06 14:33:50

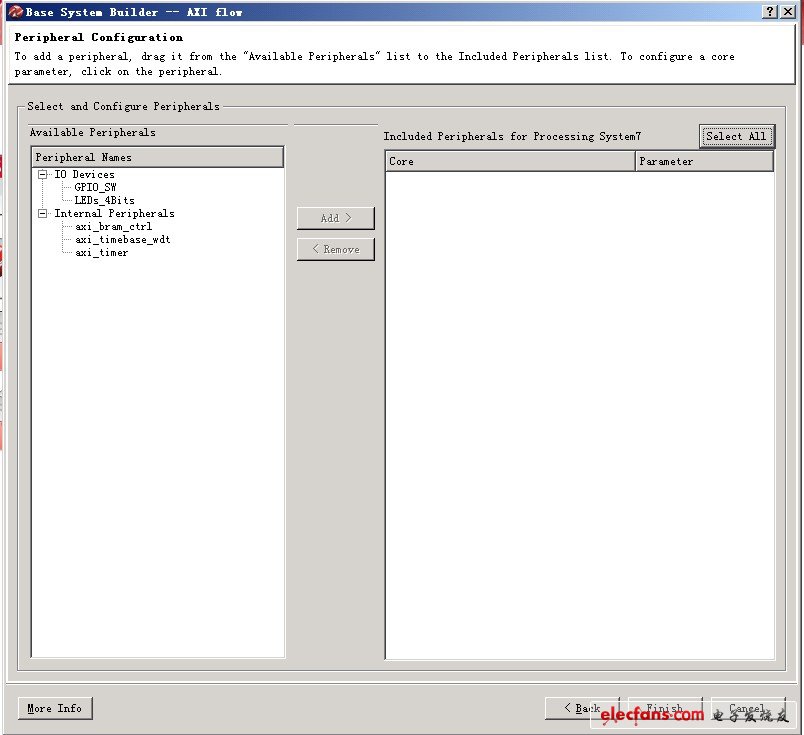

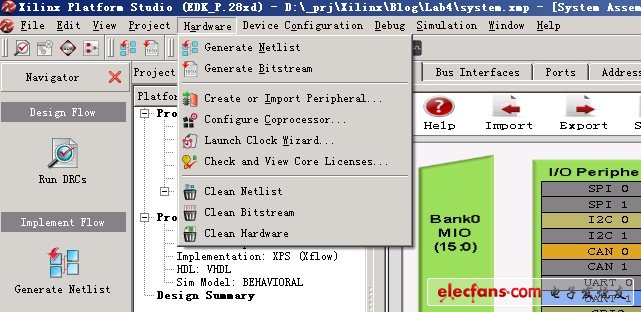

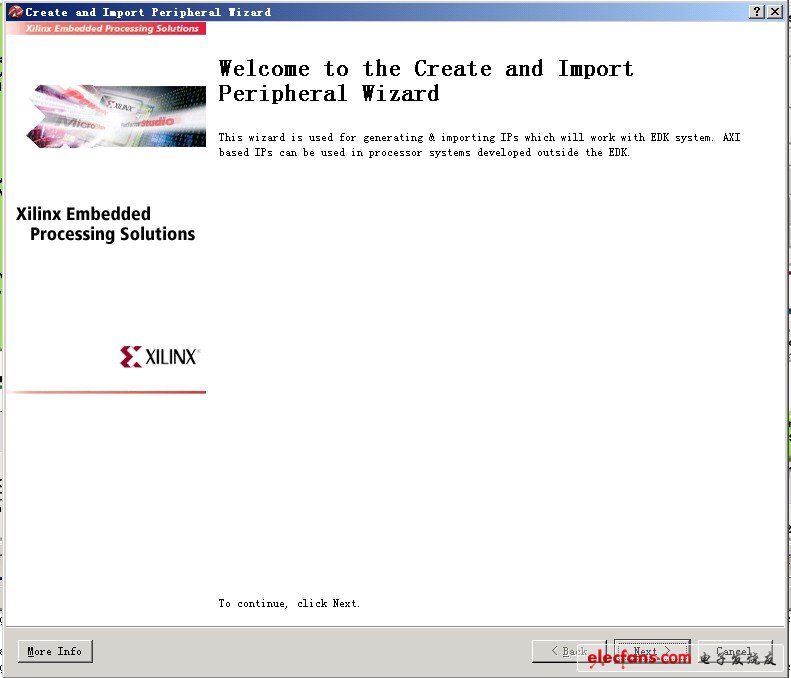

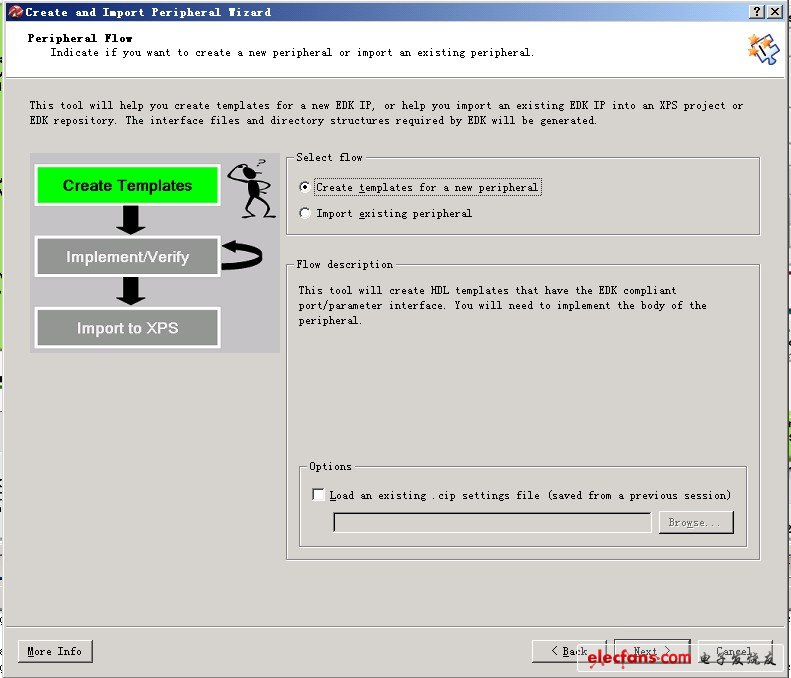

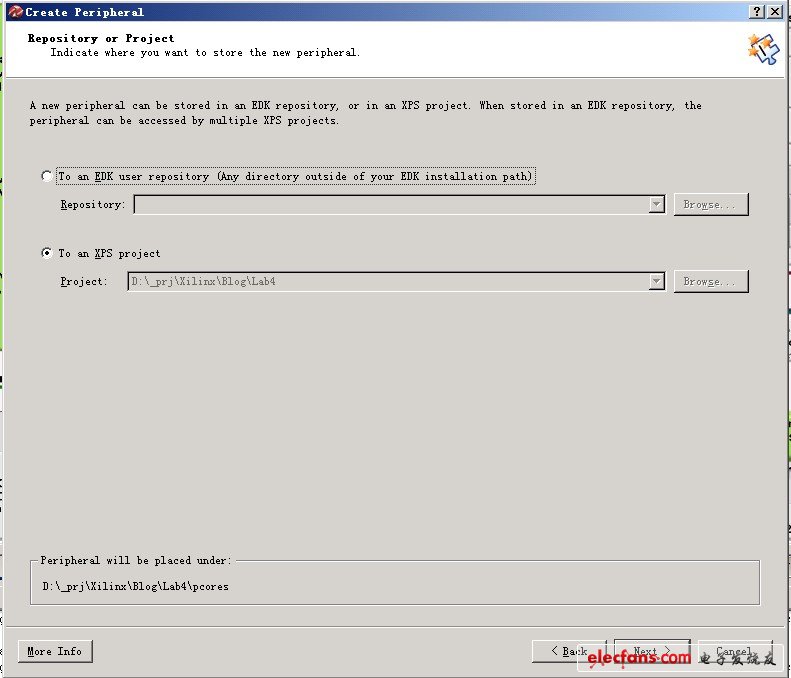

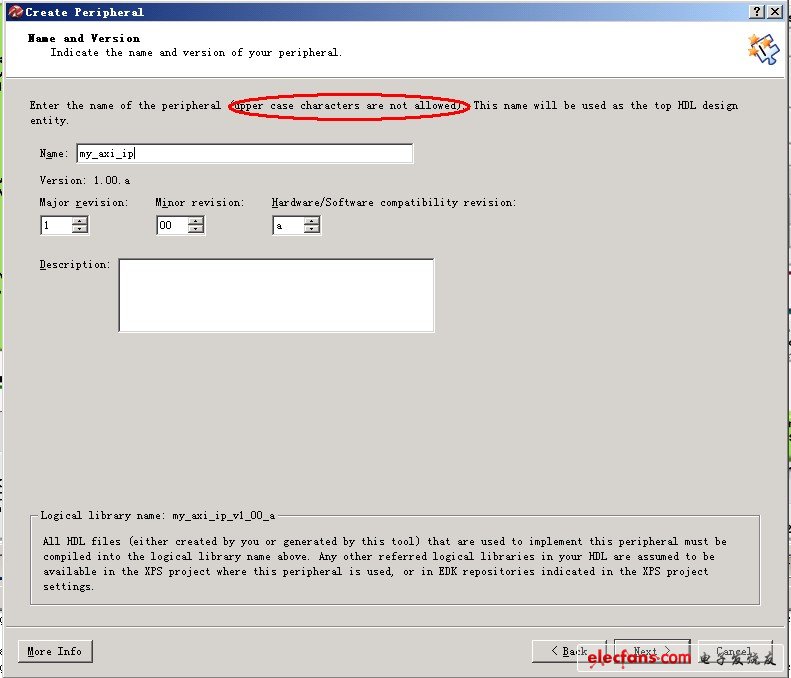

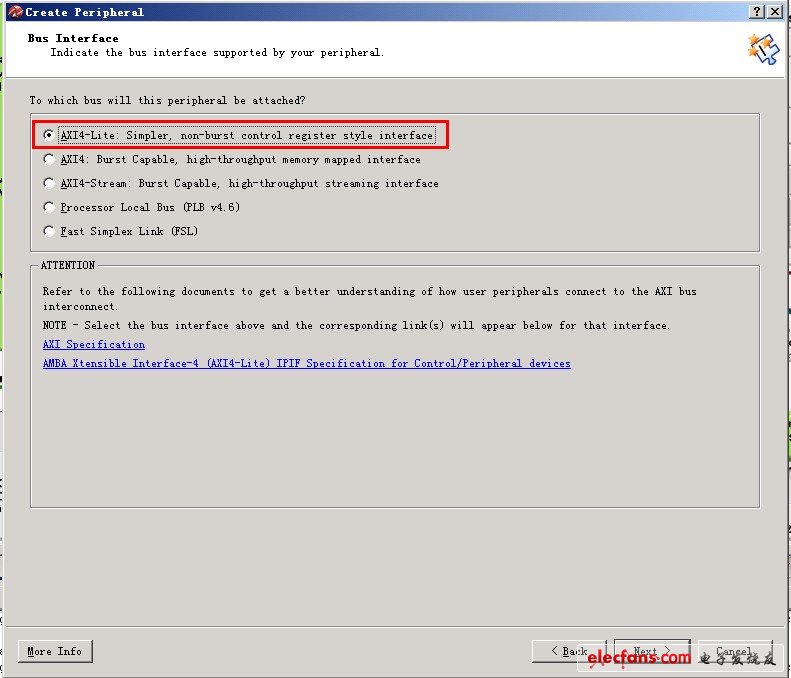

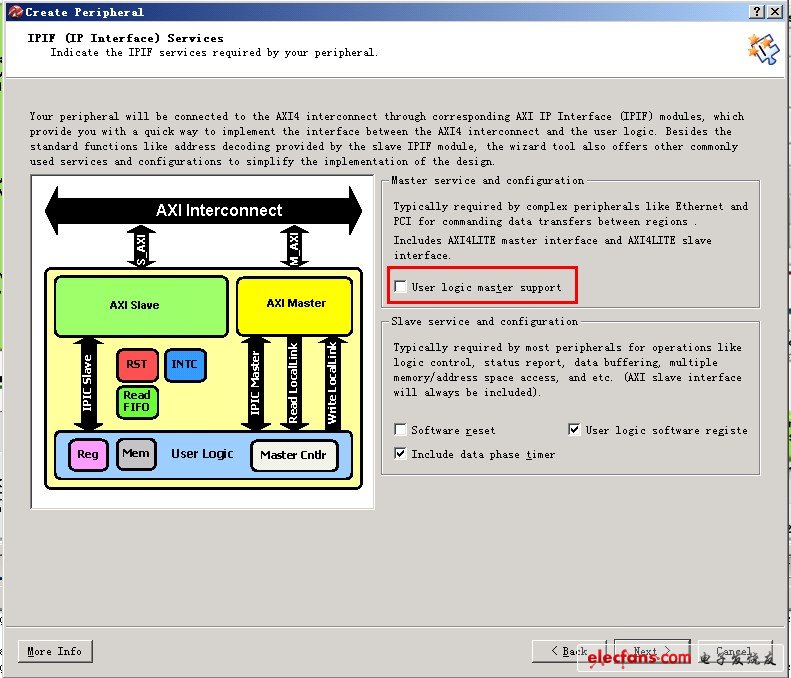

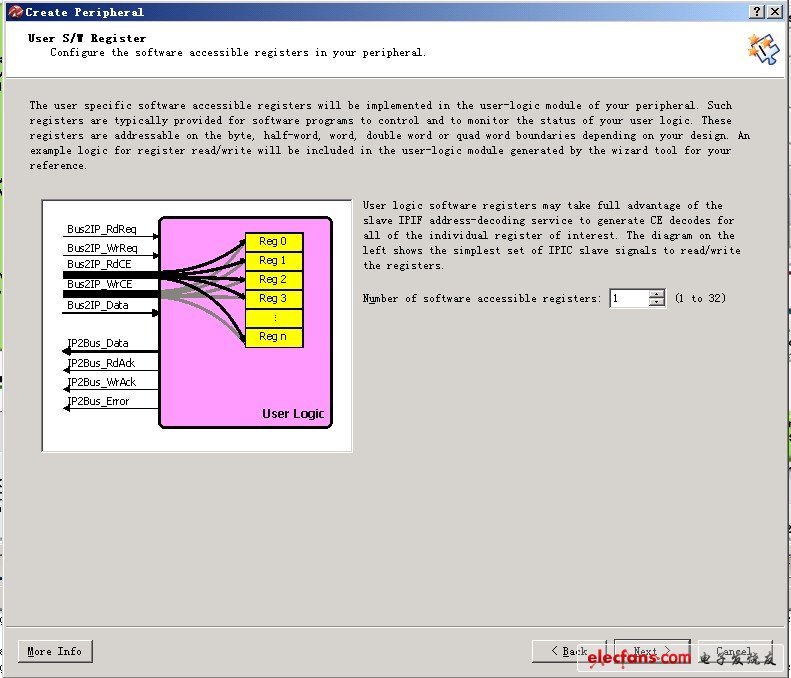

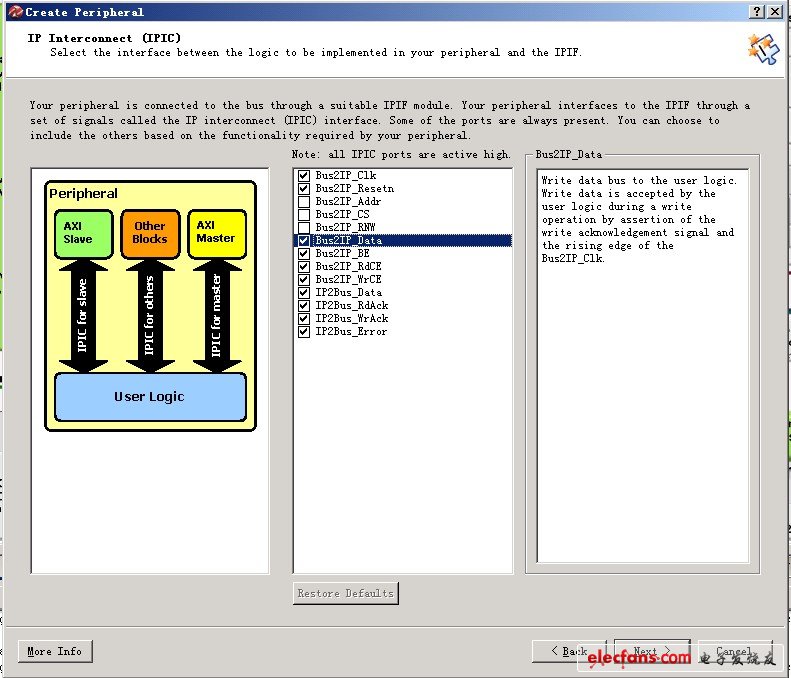

本小節(jié)通過使用XPS中的定制IP向?qū)?ipwiz),為已經(jīng)存在的ARM PS 系統(tǒng)添加用戶自定IP(Custom IP ),了解AXI Lite IP基本結(jié)構(gòu),并掌握AXI Lite IP的定制方法,為后續(xù)編寫復(fù)雜AXI IP打下基礎(chǔ)。

2017-02-10 20:37:12 5407

5407 本文先總結(jié)不同AXI IP核的實(shí)現(xiàn)的方法,性能的對(duì)比,性能差異的分析,可能改進(jìn)的方面。使用的硬件平臺(tái)是Zedboard。 不同的AXI總線卷積加速模塊的概況 這次實(shí)現(xiàn)并逐漸優(yōu)化了三個(gè)版本的卷積加速模塊,先簡要描述各個(gè)版本的主要內(nèi)容。

2018-06-29 14:34:00 7834

7834

這將創(chuàng)建一個(gè)附帶 BD 的 Vivado 工程,此 BD 包含 AXI VIP (設(shè)置為 AXI4-Lite 主接口) 和 AXI GPIO IP。這與我們?cè)?AXI 基礎(chǔ)第 3 講一文 中完成的最終設(shè)計(jì)十分相似。

2020-04-30 16:24:50 2068

2068

XDMA是Xilinx封裝好的PCIE DMA傳輸IP,可以很方便的把PCIE總線上的數(shù)據(jù)傳輸事務(wù)映射到AXI總線上面,實(shí)現(xiàn)上位機(jī)直接對(duì)AXI總線進(jìn)行讀寫而對(duì)PCIE本身TLP的組包和解包無感。

2020-12-28 10:17:23 2692

2692 在《AXI-Lite 自定義IP》章節(jié)基礎(chǔ)上,添加ilavio等調(diào)試ip,完成后的BD如下圖: 圖4?53 添加測(cè)試信號(hào) 加載到SDK,并且在Vivado中連接到開發(fā)板。 Trigger Setup

2020-10-30 17:10:22 2041

2041

和接口的構(gòu)架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過

2020-11-02 11:27:51 3880

3880

AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解

2022-07-04 09:40:14 5818

5818 在 AXI 基礎(chǔ)第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,使用 C 語言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。在本篇博文中,我們將學(xué)習(xí)如何導(dǎo)出 IP

2022-08-02 09:43:05 579

579

在 Vivado 中自定義 AXI4-Lite 接口的 IP,實(shí)現(xiàn)一個(gè)簡單的 LED 控制功能,并將其掛載到 AXI Interconnect 總線互聯(lián)結(jié)構(gòu)上,通過 ZYNQ 主機(jī)控制,后面對(duì) Xilinx 提供的整個(gè) AXI4-Lite 源碼進(jìn)行分析。

2023-06-25 16:31:25 1914

1914

中的一個(gè)參數(shù)來選擇。 集成設(shè)計(jì)環(huán)境(IDE)。AXI數(shù)據(jù)總線的寬度可定制。該IP可通過AXI4互連驅(qū)動(dòng)AXI4-Lite或AXI4內(nèi)存映射從站。運(yùn)行時(shí)間與該內(nèi)核的交互需要使用Vivado邏輯分析器功能。

2023-10-16 10:12:42 410

410

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關(guān)IP核中,經(jīng)常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論