摘要本文提出了一種基于FPGA的通用位同步器設(shè)計方案。方案中的同步器是采用改進后的Gardner算法結(jié)構(gòu),其中,內(nèi)插濾波器采用系數(shù)實時計算的Farrow結(jié)構(gòu),定時誤差檢測采用獨立于載波相位偏差的GA-TED算法,內(nèi)部控制器和環(huán)路濾波器的參數(shù)可由外部控制器設(shè)置,因而可以適應(yīng)較寬速率范圍內(nèi)的基帶碼元。

2013-10-14 13:58:10 5266

5266

本文介紹了集中式插入法幀同步系統(tǒng)的原理,分析了幀同步系統(tǒng)的工作流程。采用模塊化的設(shè)計思想,利用VHDL設(shè)計了同步參數(shù)可靈活配置的幀同步系統(tǒng),闡述了關(guān)鍵部件的設(shè)計方法,提出了一種基于FPGA的幀同步系統(tǒng)設(shè)計方案。

2013-11-11 13:36:01 4431

4431

為了研究數(shù)字化γ能譜儀,本文提出一種基于FPGA的數(shù)字核脈沖分析器硬件設(shè)計方案,該方案采用現(xiàn)場可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設(shè)計。用QuartusⅡ軟件在FPGA平臺上完成了數(shù)字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 1997

1997

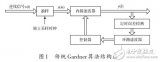

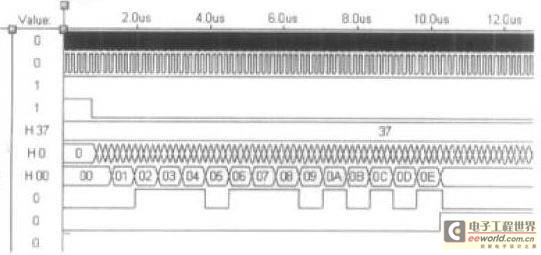

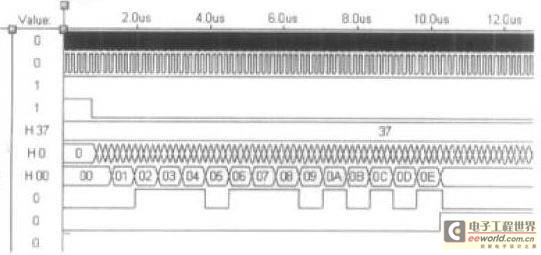

本文以標(biāo)準(zhǔn)的I2C 總線協(xié)議為基礎(chǔ),提出了一種基于FPGA的I2C SLAVE 模式總線的設(shè)計方案。方案主要介紹了SLAVE 模式的特點。給出了設(shè)計的原理框圖和modelsim 下的行為仿真時序

2014-02-26 11:39:13 12543

12543 本文描述了復(fù)位的定義,分類及不同復(fù)位設(shè)計的影響,并討論了針對FPGA和CPLD的內(nèi)部自復(fù)位方案。

2016-07-11 14:33:49 6296

6296

時鐘網(wǎng)絡(luò)反映了時鐘從時鐘引腳進入FPGA后在FPGA內(nèi)部的傳播路徑。

2019-09-10 15:12:31 6428

6428

跨時鐘域處理是FPGA設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還是在校的學(xué)生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。 在本篇文章中,主要

2020-11-21 11:13:01 3361

3361

當(dāng)我剛開始我的FPGA設(shè)計生涯時,我對明顯更小、更不靈活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常簡單的時鐘規(guī)則之一是盡可能只使用單個時鐘。當(dāng)然,這并不總是可能的,但即便如此,時鐘的數(shù)量仍然有限。

2022-09-30 08:49:26 1393

1393 FPGA典型設(shè)計方案精華匯總

2012-08-16 16:29:32

信號是FPGA內(nèi)部鎖相環(huán)產(chǎn)生的與DSP鏈路口時鐘異步的32ns時鐘信號,用來校驗令牌指令;W_FIFO_EN信號足寫緩存使能信號,當(dāng)令牌驗證后使能接收緩存;DSP_DAT信號是DSP通過鏈路門傳輸

2019-06-21 05:00:04

各位FPGA設(shè)計大賽參賽者注意了:小編這里幫大家解釋一下設(shè)計方案提交規(guī)則和活動時間安排

自4月23日比賽開始,參賽者報名之后即可提交設(shè)計方案。設(shè)計方案提交的截止日期是活動結(jié)束,暨設(shè)計方案評選的最后

2012-05-04 10:27:46

在設(shè)計中想用上AD9254作為ADC,在設(shè)計過程中發(fā)現(xiàn)datasheet內(nèi)部提供了多種時鐘設(shè)計方案,由于設(shè)計的限制,想要省去所有方案中均推薦使用的AD951x芯片,請問是否有曾經(jīng)使用過該款A(yù)D的同仁,使用直接從FPGA差分時鐘引腳引出的時鐘信號,是否能夠滿足設(shè)計的要求?

2018-11-02 09:14:32

從ASIC到FPGA的轉(zhuǎn)換系統(tǒng)時鐘設(shè)計方案

2011-03-02 09:37:37

請教下 避障小車 的設(shè)計方案 有幾種選擇? 超聲波 避障 如何?有沒有其它設(shè)計方案

2012-08-31 11:54:02

使用。但是現(xiàn)在我面臨著問題,即當(dāng)我給fpga提供時鐘時,電壓從5v下降到2.4v,因此我想在不干擾電路板制造的情況下從fpga內(nèi)部斷開時鐘。對此有什么解決方案嗎?我,閱讀Ug331文檔第61頁它告訴我們可以

2020-03-18 08:35:08

一種基于FPGA的簡易頻譜分析儀設(shè)計方案,其優(yōu)點是成本低,性能指標(biāo)滿足教學(xué)實驗所要求的檢測信號范圍。

2021-04-30 06:43:21

分享一款不錯的采用FPGA的集群通信移動終端設(shè)計方案

2021-05-25 06:32:04

提出一種基于FPGA和USB的通用CCD采集系統(tǒng)設(shè)計方案。該系統(tǒng)在不改變硬件的情況下可以采集多種CCD,并上傳至PC機,使用軟件處理采集到的數(shù)據(jù)。

2021-04-22 06:23:40

本文以星載測控系統(tǒng)為背景,提出了一種基于 Actel Flash FPGA的高可靠設(shè)計方案。采用不易發(fā)生單粒子翻轉(zhuǎn)的 flash FPGA芯片,結(jié)合 FPGA內(nèi)部的改進型三模冗余、分區(qū)設(shè)計和降級重構(gòu),實現(xiàn)了高實時、高可靠的系統(tǒng)。

2021-05-10 06:58:47

利用FPGA的無線通信收發(fā)模塊設(shè)計方案[hide][/hide]

2009-11-26 10:25:56

壓電馬達原理壓電馬達的驅(qū)動設(shè)計方案

2021-03-04 07:17:42

了非常廣泛的應(yīng)用。本文為大家介紹幾種變頻器的設(shè)計方案,包含完整軟硬件方案。基于Simulink的數(shù)字下變頻器設(shè)計及其FPGA實現(xiàn)

2019-08-28 07:42:25

如果我正確讀取Spartan3數(shù)據(jù)表,每個Spartan3中都有一個內(nèi)部硅振蕩器,可以配置為CCLK時鐘,用于在主串行模式下配置FPGA,并且有一個PERSIST選項可以在配置后保持時鐘開啟。我

2019-05-07 13:40:54

各路大神,FPGA內(nèi)部時鐘能達到1.5625GHz嗎?如輸入時鐘156.25MHz,經(jīng)過pll等倍頻到1.5625GHz?因為要處理100G的數(shù)據(jù)流,數(shù)據(jù)位寬為64位,就需要這么大的頻率。

2014-01-10 22:19:19

FPGA入門嵌入式塊RAM使用為FIOF(First In First Out)單時鐘FIOF、雙時鐘FIOF(普通雙時鐘和混合寬度雙時鐘)由于單時鐘FIOF只有一個時鐘信號,所以可以在FPGA內(nèi)部中使用單時鐘FIOF用以其他模塊數(shù)據(jù)的緩存。...

2021-12-17 07:59:18

基于51單片機的時鐘-跑表設(shè)計方案(程序+仿真)

2018-11-29 12:07:49

本帖最后由 eehome 于 2013-1-5 10:11 編輯

基于FPGA及VHDL的LED點陣漢字滾動顯示設(shè)計方案

2012-08-19 23:20:48

上學(xué)時做的變頻器設(shè)計方案,利用simulink仿真,基于FPGA的變頻器設(shè)計方案。

2014-09-10 10:40:12

基于FPGA的數(shù)據(jù)無阻塞交換設(shè)計方案,不看肯定后悔

2021-04-29 06:48:07

的,其編程簡單、控制靈活,但缺點是控制周期長、速度慢,特別是對高速轉(zhuǎn)換的數(shù)據(jù)來說,單片機的慢速度極大地限制了數(shù)據(jù)傳輸速度。而FPGA(現(xiàn)場可編程門陣列)具有單片機無法比擬的優(yōu)勢。FPGA時鐘頻率高,內(nèi)部

2020-11-25 06:17:24

外部晶振方案/內(nèi)部晶振方案/時鐘芯片方案都有哪些優(yōu)缺點?

2022-02-22 06:53:15

多種EDA工具的FPGA設(shè)計方案

2012-08-17 10:36:17

如何用FPGA實現(xiàn)DVB碼流分析功能的嵌入式設(shè)計方案?

2021-04-28 06:19:10

型號XC7VX690T-2FFG1761CPart編號XC7A200T-2FBG676C我們計劃使用MMCM在FPGA內(nèi)部生成時鐘。這將在PCB中布線MGT時鐘引腳,以饋送MGT參考時鐘GTP

2020-03-18 09:53:15

“玩轉(zhuǎn)FPGA:iPad2,賽靈思開發(fā)板等你拿”活動持續(xù)火爆進行中……………………活動得到了廣大電子工程師積極強烈的支持,為了回報電子工程師和網(wǎng)站會員,現(xiàn)在只需提交fpga設(shè)計方案,就有機會獲得賽靈

2012-07-06 17:24:41

提高FPGA的時鐘精度的方案有哪些,哪位大神告訴一下

2015-10-13 08:22:31

PCI總線特點及開發(fā)現(xiàn)狀PCI接口配置空間的實現(xiàn)求一款在PCI總線上利用FPGA技術(shù)設(shè)計PCI總線接口的設(shè)計方案

2021-04-15 06:17:20

討論了一種基于FPGA的64點FFT處理器的設(shè)計方案,輸入數(shù)據(jù)的實部和虛部均以16位二進制數(shù)表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發(fā)平臺對處理器各個的模塊進行設(shè)計,在Stratix系列中的EP1S25型FPGA通過了綜合和仿真,運算結(jié)果正確。

2021-04-29 06:25:54

求一種基于FPGA的HDLC協(xié)議控制器設(shè)計方案

2021-04-30 06:53:06

求一種基于FPGA的永磁同步電機控制器的設(shè)計方案。

2021-05-08 07:02:07

一種基于FPGA技術(shù)的多按鍵狀態(tài)識別系統(tǒng)的設(shè)計方案

2021-05-06 08:44:59

本文主要提出一種集中式插入法幀同步的FPGA的設(shè)計方案。

2021-06-02 06:07:10

用單片機實現(xiàn)電子時鐘設(shè)計方案時鐘電路在計算機系統(tǒng)中起著非常重要的作用,是保證系統(tǒng)正常工作的基礎(chǔ)。在一個單片機應(yīng)用系統(tǒng)中,時鐘有兩方面的含義:一是指為保障系統(tǒng)正常工作的基準(zhǔn)振蕩定時信號,主要由晶振

2009-12-17 11:20:48

計算FPGA外部引腳的頻率。我需要將其與內(nèi)部FPGA時鐘同步嗎?內(nèi)部參考時鐘以60Mhz運行,外部頻率在10khz到15khz之間變化,不同步的外部頻率是否會導(dǎo)致錯誤或問題?以上來自于谷歌翻譯以下

2019-06-18 09:37:29

針對單片機的時鐘頻率電路有哪幾種設(shè)計方案?分別有何優(yōu)缺點?

2022-02-22 06:20:34

在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎(chǔ)上,提出了一種基于FPGA 的GPS同步時鐘裝置的設(shè)計方案,實現(xiàn)了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 45

45 一種FPGA時鐘網(wǎng)絡(luò)中鎖相環(huán)的實現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時鐘分配網(wǎng)絡(luò)功耗與面積的時鐘布線結(jié)構(gòu)模型。并在時鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時鐘偏差,探

2009-08-08 09:07:22 25

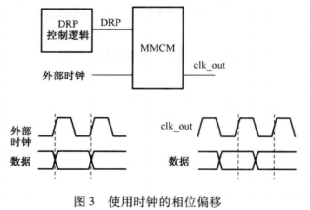

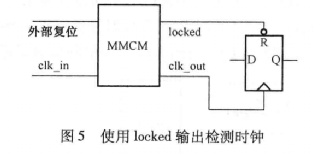

25 DLL在FPGA時鐘設(shè)計中的應(yīng)用:在ISE集成開發(fā)環(huán)境中,用硬件描述語言對FPGA 的內(nèi)部資源DLL等直接例化,實現(xiàn)其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發(fā)板設(shè)計中的

2009-11-01 15:10:30 33

33 簡化Xilinx和Altera FPGA調(diào)試過程:通過FPGAViewTM 解決方案,如混合信號示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內(nèi)部迅速移動探點,而無需重新編譯設(shè)計方案。能夠把內(nèi)部FPGA

2009-11-20 17:46:26 26

26 采用FPGA的嵌入式系統(tǒng)設(shè)計方案

可編程片上系統(tǒng)設(shè)計是一個嶄新的、富有生機的嵌入式系統(tǒng)設(shè)計技術(shù)研究方向。本文在闡述可編程邏輯器件特點及其發(fā)展趨勢的

2010-03-22 11:21:49 16

16 本文闡述了用于FPGA的可優(yōu)化時鐘分配網(wǎng)絡(luò)功耗與面積的時鐘布線結(jié)構(gòu)模型。并在時鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時鐘偏差,探討了FPGA時鐘網(wǎng)絡(luò)中鎖相環(huán)的實現(xiàn)方案。

2010-08-06 16:08:45 12

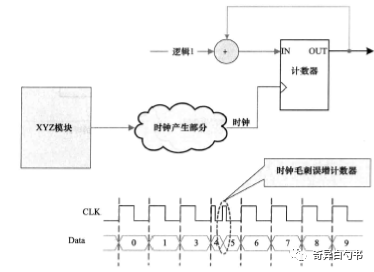

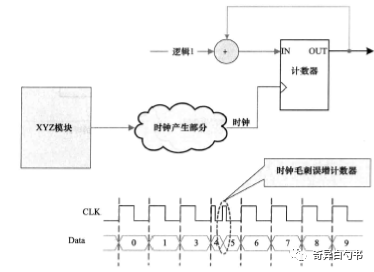

12 提出了一種基于FPGA的時鐘跟蹤環(huán)路的設(shè)計方案,該方案簡化了時鐘跟蹤環(huán)路的結(jié)構(gòu),降低了時鐘調(diào)整電路的復(fù)雜度。實際電路測試結(jié)果表明,該方案能夠使接收機時鐘快速準(zhǔn)確地跟蹤發(fā)

2010-11-19 14:46:54 31

31 基于FPGA的無線通信收發(fā)模塊設(shè)計方案

1 前言

近年來,隨著半導(dǎo)體工藝技術(shù)和設(shè)計方法的迅速發(fā)展,系統(tǒng)級芯片SOC的設(shè)計得以高速發(fā)展,

2009-12-10 10:11:07 1739

1739

基于FPGA的視頻傳輸流發(fā)送系統(tǒng)設(shè)計方案

1 引言

在目前的廣播電視系統(tǒng)中ASI接口是使用非常廣泛的一種接口形式,該接口隨同SPI一起被歐

2009-12-14 09:39:33 1264

1264 基于ADC和FPGA脈沖信號測量的設(shè)計方案

0引言

測頻和測脈寬現(xiàn)在有多種方法。通常基于MCU的信號參數(shù)測量,由于其MCU工作頻率很低,所以能夠達到的精度也

2009-12-21 09:13:23 1541

1541

基于FPGA的高速定點FFT算法的設(shè)計方案

引 言 快速傅里葉變換(FFT)作為計算和分析工具,在眾多學(xué)科領(lǐng)域(如信號處理、圖像處理、生物信息學(xué)、計算物理

2010-02-09 10:47:50 1026

1026

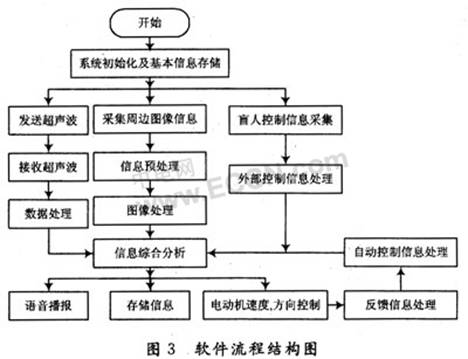

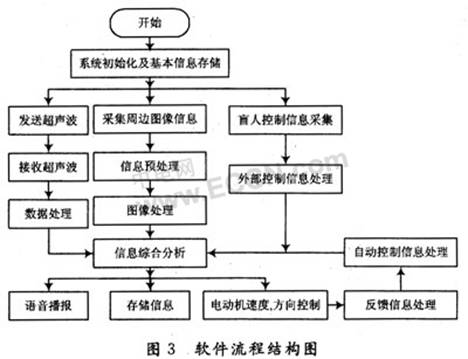

采用FPGA技術(shù)的智能導(dǎo)盲犬設(shè)計方案

眾所周知眼晴是“心靈之窗”,而對于突然失去或從未擁有過“心靈之窗”的盲人來說,生活上的困難與心理上

2010-03-22 09:40:28 920

920

基于Spartan-6的FPGA SP601開發(fā)設(shè)計方案

Spartan-6是Xilinx公司的FPGA批量應(yīng)用有最低成本的FPGA,采用45nm低功耗銅工藝,在成本,性能和功耗上有最好的平衡.該系

2010-04-02 14:25:28 2312

2312 采用VC++程序的FPGA重配置設(shè)計方案利用現(xiàn)場可編程邏輯器件FPGA的多次可編程配置特點,通過重新下載存儲于存儲器的不同系統(tǒng)數(shù)據(jù)

2010-04-14 15:14:57 594

594

多種EDA工具的FPGA設(shè)計方案

概述:介紹了利用多種EDA工具進行FPGA設(shè)計的實現(xiàn)原理及方法,其中包括設(shè)計輸入、綜合、功能仿真、實現(xiàn)、時序仿真、配

2010-05-25 17:56:59 681

681

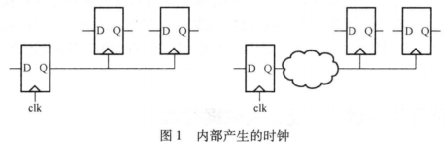

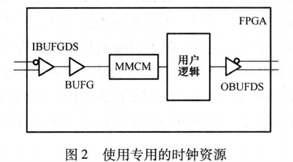

在FPGA設(shè)計中,為了成功地操作,可靠的時鐘是非常關(guān)鍵的。設(shè)計不良的時鐘在極限的溫度、電壓下將導(dǎo)致錯誤的行為。在設(shè)計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3517

3517

SERDES在數(shù)字系統(tǒng)中高效時鐘設(shè)計方案,無論是在一個FPGA、SoC還是ASSP中,為任何基于SERDES的協(xié)議選擇一個參考時鐘源都是非常具有挑戰(zhàn)性的。

2012-02-16 11:23:43 5489

5489

基于FPGA技術(shù)的RS232接口時序電路設(shè)計方案

2017-01-26 11:36:55 29

29 基于FPGA的OLED真彩色顯示設(shè)計方案

2017-01-18 20:35:09 25

25 數(shù)字電路設(shè)計方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 基于FPGA三相正弦波pwm控制器的設(shè)計方案

2018-04-08 17:33:39 30

30 基于FPGA的調(diào)焦電路設(shè)計方案資料下載

2018-05-07 15:53:08 9

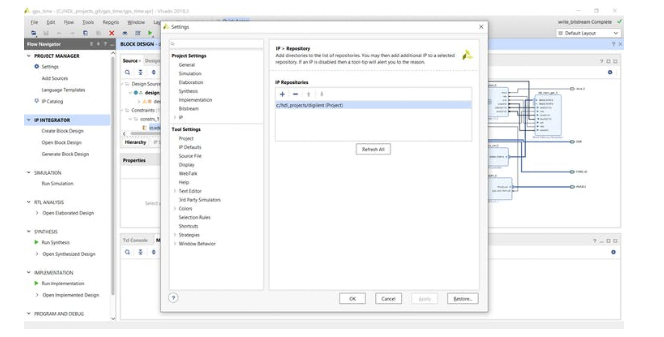

9 時鐘網(wǎng)絡(luò)反映了時鐘從時鐘引腳進入FPGA后在FPGA內(nèi)部的傳播路徑。 報告時鐘網(wǎng)絡(luò)命令可以從以下位置運行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2607

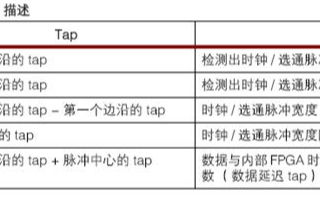

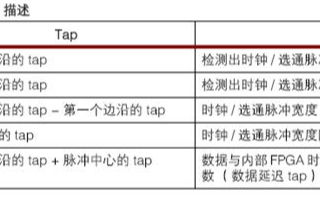

2607 ,并與內(nèi)部 FPGA 時鐘實現(xiàn)中心對齊。在這個方案中,內(nèi)部 FPGA時鐘采集傳出的數(shù)據(jù)。存儲器傳出的時鐘/ 選通脈沖用于決定與數(shù)據(jù)位相關(guān)的延遲值。因此,與選通脈沖相關(guān)的數(shù)據(jù)位的數(shù)量不受限制。由于無需將選通脈沖分配給相關(guān)數(shù)據(jù)位,所以不需要其他時鐘資源。

2020-11-26 10:01:31 1285

1285

對于一個設(shè)計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預(yù)測的時鐘。只要可能就應(yīng)盡量在設(shè)計項目中采用全局時鐘。FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

2021-04-24 09:39:07 5980

5980

基于FPGA的二進制相移鍵控設(shè)計方案

2021-05-28 09:36:50 11

11 基于FPGA的嵌入式信號處理系統(tǒng)設(shè)計方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信號處理系統(tǒng)設(shè)計方案

2021-06-02 11:04:33 0

0 基于CPLD/FPGA的半整數(shù)分頻器設(shè)計方案

2021-06-17 09:37:02 21

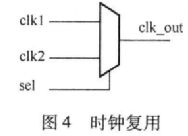

21 時鐘設(shè)計方案在復(fù)雜的FPGA設(shè)計中,設(shè)計時鐘方案是一項具有挑戰(zhàn)性的任務(wù)。設(shè)計者需要很好地掌握目標(biāo)器件所能提供的時鐘資源及它們的限制,需要了解不同設(shè)計技術(shù)之間的權(quán)衡,并且需要很好地掌握一系列設(shè)計實踐

2021-06-17 16:34:51 1589

1589

基于FPGA的偽隨機數(shù)發(fā)生器設(shè)計方案

2021-06-28 14:36:49 4

4 stm32內(nèi)部時鐘有哪些時鐘源 在STM32中,可以用內(nèi)部時鐘,也可以用外部時鐘,在要求進度高的應(yīng)用場合最好用外部晶體震蕩器,內(nèi)部時鐘存在一定的精度誤差。 內(nèi)部時鐘有2個時鐘源可以選分別是HSI

2021-07-22 10:38:57 15974

15974 基于STM32單片機的時鐘樹設(shè)計方案

2021-08-04 16:37:06 38

38 本方案是一個基于FPGA的二進制時鐘,使用GPS作為時間參考。

2022-05-13 17:41:31 1861

1861

本文詳細(xì)描述了FPGA實現(xiàn)圖像去霧的實現(xiàn)設(shè)計方案,采用暗通道先驗算法實現(xiàn),并利用verilog并行執(zhí)行的特點對算法進行了加速;

2023-06-05 17:01:45 909

909

我們設(shè)計時要盡可能避免在內(nèi)部產(chǎn)生時鐘,如果操作不當(dāng),會導(dǎo)致設(shè)計功能和時序問題。總而言之,盡量在代碼中避免操作時鐘。

2023-09-19 09:26:42 561

561

電子發(fā)燒友網(wǎng)站提供《基于FPGA的PCI硬件加解密卡的設(shè)計方案.pdf》資料免費下載

2023-10-18 11:18:03 0

0 電子發(fā)燒友網(wǎng)站提供《基于CPLD/FPGA的多串口擴展設(shè)計方案.pdf》資料免費下載

2023-10-27 09:45:17 3

3 如果FPGA沒有外部時鐘源輸入,可以通過調(diào)用STARTUP原語,來使用FPGA芯片內(nèi)部的時鐘和復(fù)位信號,Spartan-6系列內(nèi)部時鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 1113

1113

電子發(fā)燒友App

電子發(fā)燒友App

評論