作者:龔廣偉;韓方景;陳凡國;喬佩 來源:電子產品世界

數字信號處理模塊是接收機系統的核心部分,系統要求數字信號處理模塊能實時處理ADC變換后的數字信號,并用軟件的方法來實現大量的無線電功能,這些功能包括:多通道校準、編解碼、調制解調、濾波、同步、盲均衡、檢測、數據加密、傳輸加密糾錯、跳擴頻及解擴和解跳、通信環境評估、信道選擇等,而單個DSP根本無法完成這些功能。目前可用的一些高速DSP的性能最快的也不超過5GIPS ,與實際需求相差巨大。這種處理資源的匱乏,被稱之為DSP 瓶頸[1],因此我們在本系統中主要采用Xilinx的FPGA芯片實現后端數字信號處理。

時鐘同步

FPGA硬件設計中,時鐘是整個設計最重要、最特殊的信號,異步信號輸入總是無法滿足數據的建立保持時間,所以需要把所有異步輸入都先進行同步化。時鐘同步的重要性如下:

● 系統內大部分器件的動作都是在時鐘的跳變沿上進行,這就要求時鐘信號時延差要非常小,否則就可能造成時序邏輯狀態出錯;

● 時鐘信號通常是系統中頻率最高的信號;

● 時鐘信號通常是負載最重的信號,所以要合理分配負載。出于這樣的考慮在FPGA這類可編程器件內部一般都設有數量不等的專門用于系統時鐘驅動的全局時鐘網絡。

對于一個設計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。只要可能就應盡量在設計項目中采用全局時鐘。FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

但在許多應用中會出現兩個或兩個以上非同源時鐘,系統設計將面臨復雜的時間問題,數據的建立和保持時間很難得到保證。對于需要多時鐘的時序電路,最好將所有非同源時鐘同步化,即選用一個頻率是它們的時鐘頻率公倍數的高頻主時鐘。各個功能模塊要使用統一的復位電路。在使用帶時鐘的觸發器、計數器等有復位端的庫器件時,一般應盡量使用有同步復位的器件。注意復位時應保證各個器件都能復位,以避免某些寄存器的初始狀態不確定而引起系統工作不可靠。

基于以上分析,在本設計中,將64M的高頻時鐘作為系統時鐘,輸入到所有觸發器的時鐘端。時鐘使能信號Clk_en將控制所有觸發器的使能端。即原來接8M時鐘的觸發器,接64M時鐘,同時Clk_en將控制該觸發器使能;原接64M時鐘的觸發器,還接64M時鐘,Clk_en也將控制該觸發器使能。這樣,就可以將任何非同源時鐘同步化。

多通道校準同步算法

下面以M元陣為例來說明多通道校準過程。接收機開機時,先將選擇開關S切換到位置2(見圖1),進入校準狀態。注入信號s(t)經功分器進入各陣元通道,陣元通道輸出為基帶數字信號 xm(t)。將第一條通道作為參考通道,第一條通道的輸出延時τ后作為參考信號,與其他陣元通道的輸出一起送入相應的自適應校正濾波器。自適應校正濾波器將會對陣元通道的傳輸特性進行補償,使各個陣元通道的傳輸特性趨近參考通道。這里采用LMS自適應算法,待自適應算法收斂后,穩態權矢量將作為自適應校正濾波器的系數固定下來,至此陣元通道的校正結束。最后,將選擇開關S切換到位置1就可進入正常通信狀態。

按圖1所示的模型可知,用L階橫向FIR濾波器模擬通道響應,通過在濾波器的系數上加上小的幅度擾動δ和相位擾動Φ來模擬通道間的失配,這樣可得第m個待校準通道模擬濾波器的傳輸函數為:

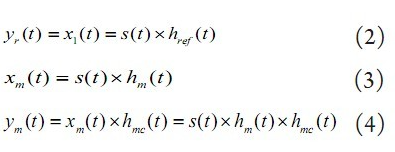

設注入的信號是s(t),href(t)和hm(t)分別為參考通道和待校準的第m條通道的沖激響應,hmc(t)為第m條通道的校準濾波器的沖激響應,那么參考通道的輸出(暫不考慮延時τ)、第m條待校準通道校準前的輸出和校準后的輸出分別為:

自適應濾波器采用MMSE準則,其中,準則選擇是否合理決定了天線陣暫態響應的速度和實現電路的復雜度。可以證明,這個準則的結果可以分解為一個相同的線性矩陣濾波器和一個不同的標量處理器的積,且都收斂于最優維納解。因此,當自適應濾波器收斂到穩態即最優解后,最佳權值應該為:

從而通道特性得到了校準。

本文中的多通道校準算法是在FPGA中實現的,選擇FPGA而不選擇DSP器件的原因是FPGA的引腳眾多且可以定制,這樣就可以在相對較低的工作頻率下做到很高的數據吞吐率,而這是DSP難以做到的。

FPGA實現

在本設計中應該綜合考慮各方面因素,選擇一種最佳模塊結構和模塊規模。本設計中的結構化層次是由一個頂層模塊和若干個子模塊組成,每個子模塊根據需要再包含自己的子模塊,以此類推,共5層,如圖2所示。

本設計中,整個通道失配校準模塊共需要90個乘法器。這些乘法器如果采用FPGA的邏輯資源直接構建,不僅難以保證理想的運算速度,而且硬件開銷非常巨大。而FPGA芯片內部已經集成了18×18位的硬件乘法器模塊,其速度快,實現簡單,能有效節省FPGA的邏輯資源。由于系統設計時選用的FPGA芯片型號為Xilinx公司的xc2v8000ff1152-5,它集成了幾百個硬件乘法器,因此可以全部使用硬件乘法器來完成相應的乘法運算。

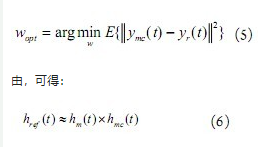

采用VHDL語言編寫實現程序,開發環境為ISE 8.2i,綜合工具為Synplify Pro v8.1,仿真工具為ModelSim SE 6.3f。圖3所示的是程序經Synplify Pro v8.1綜合后得到的LMS自適應校正濾波器頂層模塊RTL視圖。RTL視圖即寄存器傳輸級視圖,該圖高度抽象為模塊化結構,它是在對源代碼編譯后再現設計的寄存器傳輸級原理圖。

所有算法模塊均在全局使能信號clk_en不同狀態的控制下進行工作,從而使算法運行達到8M周期,直至找到最佳權值,最終完成多通道校準的任務,實現多個通道的幅相一致性。

表1為多通道校準算法的FPGA資源占用列表,從系統資源占用情況可以看出:多通道校準算法FPGA實現過程中,如果再加上前后端處理程序一起編譯,則輸入輸出端口將減少,資源占用也將減少,并不影響系統實現。其它各種資源占用量都較少,完全符合FPGA設計要求。

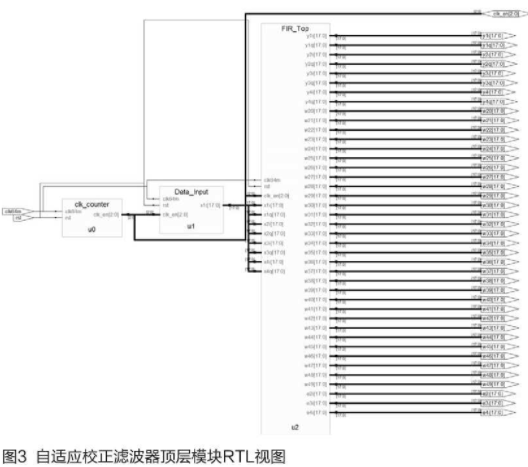

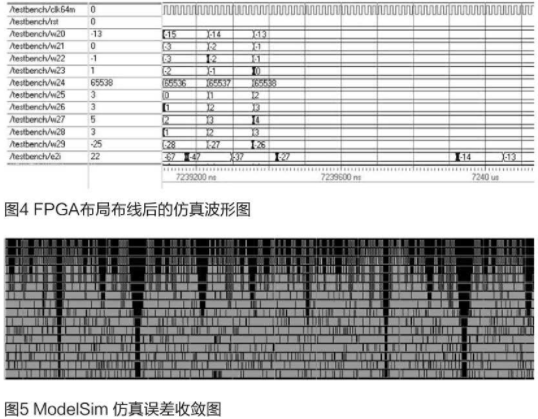

FPGA布局布線后的仿真波形如圖4、圖5所示。

從仿真結果(圖4,圖5)和ISE 8.2i的綜合報告可知,該校正模塊的最高時鐘頻率達到102.5MHz。

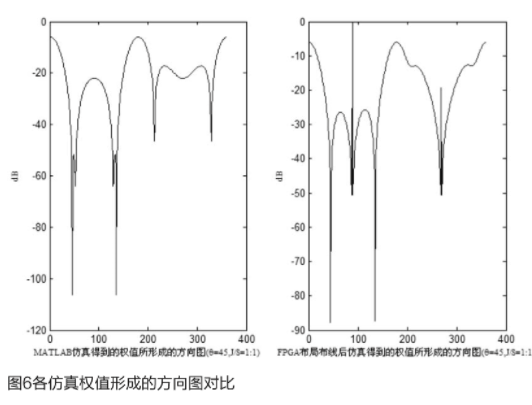

最后,由MATLAB仿真和FPGA布局布線后仿真得到的權值,經過MATLAB仿真形成新的方向圖,如圖6所示,可以看出,兩種方向圖基本一致。因此,基于FPGA的多通道校準同步算法的實現完全符合系統要求。

結語

由于數據時鐘的同步是FPGA 芯片設計實現的一個常見問題,也是一個重點和難點,很多設計不穩定都是源于數據時鐘的同步有問題。而本文提出了解決這一問題的時鐘同步方法,并在硬件上很好地實現了多通道校準算法,極大提高了系統穩定性。

責任編輯:gt

-

FPGA

+關注

關注

1643文章

21944瀏覽量

613450 -

芯片

+關注

關注

459文章

52089瀏覽量

435293 -

觸發器

+關注

關注

14文章

2031瀏覽量

61831

發布評論請先 登錄

基于FPGA的幀同步系統設計方案

FPGA時鐘設計方案

基于FPGA的時鐘恢復以及系統同步方案設計

基于FPGA 的OFDM 寬帶數據通信同步系統設計與實現

嵌入式同步時鐘系統的設計方案

采用FPGA實現同步、幀同步系統的設計

低成本的采用FPGA實現SDH設備時鐘芯片技術

基于FPGA芯片實現數據時鐘同步設計方案

基于FPGA芯片實現數據時鐘同步設計方案

評論