本文首先會對這個問題進行一般性地分析,在此基礎上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個新的解決方案,即采用雙時鐘模式提供 SERDES系統時鐘,并且探討

2013-09-26 14:34:31 3258

3258

不夠的情況下有可能會造成 FIFO 的溢出。本文首先會對這個問題進行一般性地分析,在此基礎上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個新的解決方案,即采用雙時鐘模式提供 SERDES系統時鐘。

2013-09-29 10:05:45 2100

2100

本文提出了一臺基于S12的簡易便攜式數字示波器的設計方案,該設計方案中的數字示波器能對任意小于1MHz的波形進行頻率和峰峰值的測量,且能夠對被測周期信號或單次非周期信號進行單次采集與儲存,連續顯示。該設計方案中的以S12為主控單片機,制作出的示波器不僅可以測量低頻的直流信號,也可以測量高頻的交流信號。

2013-11-05 09:10:46 2665

2665

/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道

2019-05-29 17:52:03

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中,有幾個因素限制了有效數據窗口寬度的繼續增加。a)、時鐘...

2021-07-28 08:35:42

的。特別是在數字控制電源中,DVS 很常見,也很容易實現。穩壓器一般用于生成恒定的輸出電壓。利用控制環路,可通過未經調節的輸入電壓生成穩定、精準的輸出電壓。動態電壓調節(DVS)有什么作用?動態電壓

2021-01-20 07:00:00

數字電子鐘設計方案數字鐘是一種用數字電路技術實現時、分、秒計時的裝置,與機械式時鐘相比具有更高的準確性和直觀性,且無機械裝置,具有更更長的使用壽命,因此得到了廣泛的使用。數字鐘從原理上講是一種典型

2009-12-17 11:31:30

本帖最后由 eehome 于 2013-1-5 10:02 編輯

數字語音解碼器的低功耗設計方案

2012-08-20 12:50:40

嗨,我有一個項目,我必須在發送器端序列化16位數字輸入數據,然后在接收器端反序列化數據。這種數字鏈路的預期速度是100MHz-500MHz。這種實現必須是系統同步的,即沒有任何時鐘轉發,我必須在Rx

2019-08-06 10:31:49

接(Dual Link)兩種方式,對于單連接,僅用圖1所示的1/2、9/10、17/18腳傳輸,它的傳輸速率可達4.9Gbps,雙連接可達9.9Gbps。DVI接口在數字電視中的應用● 基本方案論證分析

2018-12-12 10:18:10

隨著SerDes芯片集成度,復雜度,傳輸速率的不斷提高,傳統的自動化測試系統已經無法滿足SerDes測試速率需求。為解決該測試難題,通過Nautilus UDI方案的導入,成功得實現了32 Gbps

2021-05-10 06:58:55

介紹一種包含千兆采樣率ADC的系統設計方案

2021-05-14 06:07:02

介紹一種汽車LED照明系統的設計方案

2021-05-13 06:52:48

介紹一種視頻監控系統的設計方案

2021-05-31 07:07:58

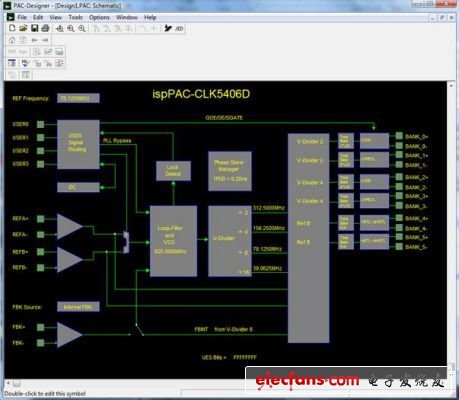

從ASIC到FPGA的轉換系統時鐘設計方案

2011-03-02 09:37:37

本帖最后由 eehome 于 2013-1-5 09:51 編輯

入侵報警系統設計方案

2012-08-18 15:36:22

分享一份智能視頻監控應用系統的設計方案

2021-06-08 06:49:09

分享一款不錯的AMBE-2000TM聲碼器在數字加密電話中的應用方案

2021-06-08 06:58:49

分享一款不錯的保安公司監控報警聯網綜合管理系統設計方案

2021-06-01 06:12:27

分享一款不錯的基于可編程邏輯器件PLD的數字電路設計方案

2021-04-30 06:34:54

分享一款不錯的多功能對講機通信系統設計方案

2021-05-20 06:45:08

一種基于PLC的智能鉗型吊電氣控制系統的設計方案

2021-05-07 07:07:42

本文提出了一種能夠很好地反映衛星通信中星地鏈路特性的模擬系統設計方案。在確定硬件設計方案之前,搭建了合理的信道仿真模型,并對仿真結果進行了分析。

2021-04-08 06:09:33

基于51單片機的時鐘-跑表設計方案(程序+仿真)

2018-11-29 12:07:49

摘要:隨著石油勘探的發展,在地震勘探儀器中越來越需要高精度的同步技術來支持高效采集。基于這種目的,采用FPGA技術設計了一種時鐘恢復以及系統同步方案,并完成了系統的固件和嵌入式軟件設計。通過室內測試

2019-06-18 08:15:35

數字系統的設計師們面臨著許多新的挑戰,例如使用采用了串行器/解串器(SERDES)技術的高速串行接口來取代傳統的并行總線架構。基于SERDES的設計增加了帶寬,減少了信號數量,同時帶來了諸如減少布線

2019-05-21 05:00:13

本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data

2019-10-21 07:09:44

小區智能化系統設計方案

2012-08-18 15:38:43

本帖最后由 eehome 于 2013-1-5 09:50 編輯

平安城市視頻監控系統設計方案-20091213

2012-08-20 09:56:45

SerDes是怎么工作的?SerDes有傳輸時鐘信號嗎?

2021-10-18 08:53:42

為 EMI 敏感和高速 SERDES 系統供電

2019-05-21 14:34:36

求一款RFID讀卡器測試系統的設計方案

2021-05-11 07:11:35

求大神分享一款天平系統的設計方案

2021-05-11 06:20:54

求一款看守所智能網絡門禁系統的設計方案

2021-06-01 07:07:25

本文提出的一種數字信道化IFM接收機方案結合了數字信道化接收機高效結構和相位差分瞬時測頻方法,從而降低了系統復雜度,提高了實時處理能力,仿真結果表明該方案具有較好的信號檢測能力。用現代技術來實現寬帶

2021-02-23 07:05:58

求一種數字式溫度測量電路的設計方案

2021-05-17 06:16:41

求一種以CPLD為核心處理電路的數字電壓表的設計方案

2021-04-28 07:14:04

漂移及漂移形成的原因是什么?光纖漂移引起的SERDES FIFO溢出問題分析BBU SERDES 雙系時鐘方案及具體實現

2021-04-19 08:35:11

本文介紹了一種基于ARM的視頻監控系統的設計方案,采用軟壓縮算法,討論了系統的硬件和軟件設計。

2021-06-08 06:27:10

求一種基于單片機的簡易洗衣機系統仿真設計方案

2022-01-17 08:09:52

一種基于FPGA技術的多按鍵狀態識別系統的設計方案

2021-05-06 08:44:59

求一種多路模擬數字采集與處理系統的設計方案

2021-04-28 07:04:52

求一種多通道同步數據采集及壓縮系統的設計方案。

2021-04-28 06:13:04

求一種天然氣發動機電控系統的設計方案

2021-05-13 06:12:56

求一種新型系統級可編程芯片的設計方案

2021-05-06 07:44:32

求一種智能物品清點系統的設計方案

2021-05-20 07:29:31

求一種智能電源模塊測試系統的設計方案

2021-05-10 06:35:30

一種基于CPLD控制的直流固態功控系統的設計方案。

2021-05-06 06:23:55

求一種視頻檢測和遠程控制的嵌入式系統設計方案

2021-05-27 06:38:21

TPMS主要有哪幾種實現方式?如何選用新型送器(遙控鑰匙)與接收器中幾種芯片?一種基于LIN總線分布式實時輪胎壓力監測系統的設計方案

2021-05-13 06:03:12

求一種陶瓷揚聲器系統的放大器設計方案

2021-06-04 07:10:45

求大佬分享一種多光譜可見光遙感圖像壓縮系統的設計方案

2021-06-02 06:39:48

求大佬分享一種小型通信系統的設計方案

2021-05-28 06:13:52

求大神分享一種PPSM嵌入式RTOS中的窗口系統設計方案

2021-04-27 06:20:09

測溫系統設計方案,原理方案都有,有圖有真相!

2014-09-05 16:29:53

用單片機實現電子時鐘設計方案時鐘電路在計算機系統中起著非常重要的作用,是保證系統正常工作的基礎。在一個單片機應用系統中,時鐘有兩方面的含義:一是指為保障系統正常工作的基準振蕩定時信號,主要由晶振

2009-12-17 11:20:48

電氣CAD文件中高效的工作流程性能卓越的 PCschemetic ELautomation軟件具有作電氣設計時所需要的所有功能。其獨一無二的工作流程可節省您大量的時間,它代替了所有的訂貨信息——從

2009-12-04 11:24:24

的serdes?2、如果serdes是各自的,是否共享輸入時鐘?(外部時鐘,對于我們來說是156.25MHz)3、在研究SRIO速率配置時發現文檔中描述:serdes的輸出時鐘不能超過3.125GHz,該描述是否準確?是否適用于所有的serdes模塊?謝謝!

2018-08-06 06:17:36

為了保證圖像采集的高速性和連續性,求一種適用嵌入式系統的數字圖像采集模塊設計方案?

2021-04-08 06:13:26

直播PPT:直播簡介:電源技術的發展日新月異,高可靠性,高頻率,高效率,高功率密度,節能環保是未來電源產品發展的趨勢和主流。其中LLC電源設計方案越來越受到電子工程師的青睞和追捧并成為中高功率等級

2019-01-04 11:41:20

什么是達芬奇技術?達芬奇技術在數字視頻系統的應用是什么?

2021-06-04 07:17:50

針對單片機的時鐘頻率電路有哪幾種設計方案?分別有何優缺點?

2022-02-22 06:20:34

問一下哪里能找到模擬路燈控制系統的設計方案嗎?

2015-07-20 11:06:39

100MHz的時候,有些接口功能是有限制的;使用外部的REF_CLK則可以靈活選擇配置時鐘。Serdes方案表輸入文字在LS1028A芯片中,SerDes可以配置下表的功能,不在表中的搭配是不允許

2020-10-28 17:15:14

的SerDes設計方案做個簡單解讀。PART.2 LS1028A飛凌9月份發布了NXP的LS系列家族新成員——FET1028A-C核心板。其包含豐富的高速接口:PCIE、SATA、USB、以太網。與我

2020-11-01 20:21:02

數字電視系統設計方案

一、客戶需求 1、通過改造,建設傳輸750M帶寬內的40個模擬頻道和50個數字電視頻道的雙平臺傳輸網絡系

2010-03-26 17:39:40 39

39 數字電路實驗的虛擬化設計方案

介紹了虛擬儀器的簡單使用方法及其在數字電路實驗教學中的應用, 列舉了幾個例子, 并通過虛擬儀器與傳統儀器的比較得出

2010-03-30 16:15:28 20

20 在數字通信系統中,由于有高斯噪聲和多徑的影響,接收信號產生損失,從而導致時鐘信號的提取更加困難,而時鐘信號的不準確性會降低整個系統的性能。本文我們給出一種改進

2010-08-03 17:04:27 33

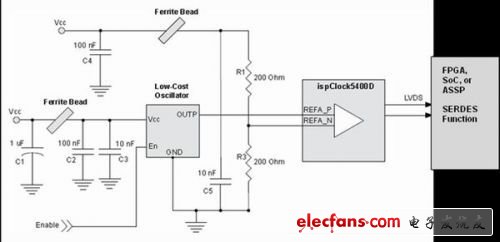

33 高速串行接口設計的高效時鐘解決方案

數字系統的設計師們面臨著許多新的挑戰,例如使用采用了串行器/解串器(SERDES)技術的高速串行接口來取代傳統的并行總線架

2010-04-09 13:24:59 968

968

病房呼叫系統設計方案

2011-01-28 09:39:13 19619

19619

本內容提供了全數字擴頻接收機的設計方案

2011-10-11 15:10:08 39

39 一種多功能數字時鐘的pcb設計方案,供大家學習使用。

2016-05-16 15:53:04 0

0 廠區監控系統設計方案_-_完本

2017-01-04 14:29:25 0

0 高效單級變換式LED驅動電源設計方案

2017-01-14 11:16:50 13

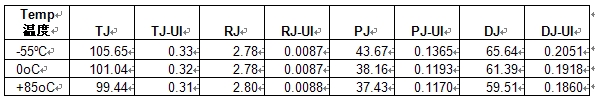

13 我們知道,SERDES對參考時鐘有嚴格的相位噪聲性能要求。通常,SERDES供應商會根據其SERDES采用的PLL以及CDR架構特點,以及性能數據,提出對參考時鐘的相位噪聲的具體要求。

2017-02-10 18:40:10 5965

5965

數字系統的設計師們面臨著許多新的挑戰,例如使用采用了串行器/解串器(SERDES)技術的高速串行接口來取代傳統的并行總線架構。基于SERDES的設計增加了帶寬,減少了信號數量,同時帶來了諸如減少布線

2017-10-26 15:37:45 4

4 時鐘的管理。本文詳細介紹了利用嵌入式微控制器MSP430單片機和數字鎖相環(DPLL)來實現嵌入式同步時鐘系統的方案和設計實例。 系統總體結構 同步設備的同步時鐘系統要求能達到3級時鐘標準,可使用從SDH網絡上提取的時鐘或外部時

2017-11-04 10:21:44 6

6 在很多無線或者有線的系統應用中,都需要器件的接收端能夠和鏈路的發送端的頻率做跟隨。通常的實現方案都是通過將SERDES的恢復時鐘引到芯片外部,然后通過一個cleanup PLL過濾抖動,然后同時再生出低相位抖動的跟隨時鐘,然后將此時鐘作為SERDES的參考時鐘。

2017-11-18 12:08:49 5865

5865

熟悉電磁兼容設計的工程師都知道,設計好時鐘電路是保證達到系統輻射指標的關鍵,時鐘電路EMC設計的好壞直接影響整個系統的性能。對于經驗豐富的工程師來說,在數字系統中有許多種方法可用于解決電磁干擾問題。

2018-04-23 08:14:00 1560

1560

隨著SerDes芯片集成度、復雜度、傳輸速率的不斷提高,傳統的自動化測試系統已經無法滿足SerDes測試速率需求。但通過Nautilus UDI方案的導入,成功實現了32 Gbps SerDes

2018-06-10 10:51:17 4434

4434

本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data

2019-05-24 15:33:25 4073

4073

為滿足目前的56GPAM-4 SerDes技術,以支持更高帶寬的100G+以太網和光網絡設計。硬件開發人員通常需要100fs(典型值)以下RMS相位抖動規范的時鐘。這些設計通常需要與CPU和系統時鐘等其他頻率時鐘混用。

2020-11-12 15:25:55 4154

4154 一種數字式可調直流穩壓電源系統設計方案

2021-06-25 10:32:54 34

34 基于STM32單片機的時鐘樹設計方案

2021-08-04 16:37:06 38

38 8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data Recovery,時鐘數

2023-07-27 16:10:01 1566

1566

的。在使用SerDes的過程中,設計者有太多的疑惑:為什么在傳輸的過程中沒有時鐘信號?什么是加重和均衡?抖動和誤碼是什么關系?各種抖動之間有什么關系?時鐘怎么恢復?等等這些問題,如果設計者能夠完全理解

2023-10-16 14:50:37 558

558

時鐘信號的同步 在數字電路里怎樣讓兩個不同步的時鐘信號同步? 在數字電路中,時鐘信號的同步是非常重要的問題。因為在信號處理過程中,如果不同步,就會出現信號的混淆和錯誤。因此,在數字電路中需要采取一些

2023-10-18 15:23:48 771

771 SerDes(Serialization/Deserialization)是一種在數字通信系統中提供重要優勢的串行/并行轉換電路。

2023-10-20 15:31:24 832

832

電子發燒友App

電子發燒友App

評論