高通執行副總裁史蒂芬·莫林科夫(Steven Mollenkopf)終于證實,公司旗下首款采用28納米制造工藝的產品將于今年年底到來!其實早前業內就已經有消息放出,暗示高通將于今年晚些時候才發

2011-07-23 09:14:13 3258

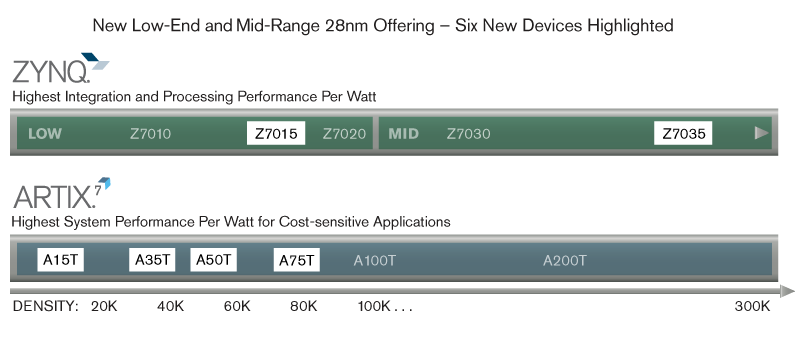

3258 賽靈思的20納米產品以備受市場肯定的28納米制程突破性技術為基礎,提供超越一個技術世代的系統效能、功耗和可編程系統整合度,繼續超越下一代!

2012-12-03 09:48:01 876

876 采用其28納米工藝制程的 Qualcomm?驍龍?410處理器已成功應用于主流智能手機,這是28納米核心芯片實現商業化應用的重要一步,開啟了先進手機芯片制造落地中國的新紀元。

2015-08-11 07:54:46 2718

2718 就是關閉XT2晶振了,在低功耗的之前開啟XT2作為時鐘源,進入低功耗的時候關閉XT2,為什么這時候功耗依然很大呢,如果在時鐘初始化的時候不操作BCSCTL1這個寄存器的話,進入低功耗后電流就非常小,我

2016-11-14 13:10:49

(Microcontroller Unit, MCU)市場,最新推出95納米單絕緣柵非易失性嵌入式存儲器(95納米5V SG eNVM)工藝平臺。在保證產品穩定性能的同時,95納米5V SG eNVM工藝平臺以其低功耗、低成本

2017-08-31 10:25:23

65納米和45納米。 65納米IC設計規模極為龐大,復雜度高,大多采用層次化物理設計和低功耗設計流程,這使65納米節點IC設計成本和設計團隊規模隨之增加。在典型情況下,設計成本是隨著設計類型的不同而改變

2019-05-20 05:00:10

低功耗MCU,晶振1.晶振有無源晶振和有源晶振,2pin和4pin,2P的晶振在設計、貼片工藝上更方便些。4腳有源晶振比2腳無源晶振好在哪里?2.供電2.5-5.5V這也算是低功耗?我看國外的低功耗

2021-10-11 17:18:28

數據透傳是選擇低功耗WiFi模塊還是低功耗藍牙模塊好?

2021-01-04 06:55:35

低功耗以太網PHY對于樓宇自動化的深遠影響

2020-11-26 06:29:47

Altera公司產品和企業市場副總裁DannyBiran低功耗是一種戰略優勢 在器件的新應用上,FPGA功耗和成本結構的改進起到了非常重要的作用。Altera針對低功耗,同時對體系結構和生產工藝進行

2019-07-16 08:28:35

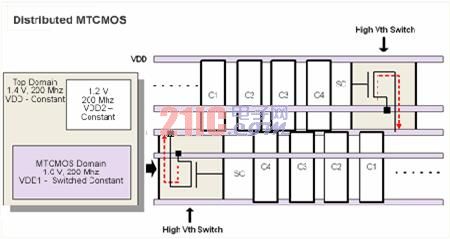

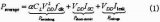

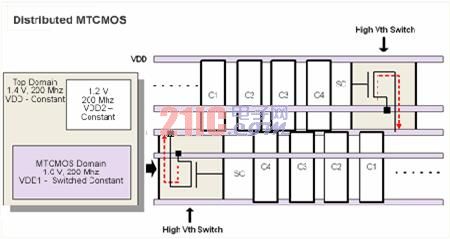

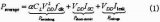

功耗存在。靜態功耗:也稱待機功耗,靜態功耗主要由晶體管的漏電流所導致的功耗。動態功耗:包括開關功耗或者成為翻轉功耗、短路功耗或者稱為內部功耗;動態功耗影響因素:門寄生電容、時鐘翻轉翻轉、時鐘頻率、供電電壓;降低功耗:應當在所有涉及層次上進行,即系統級、邏輯級和物理即,層次越高對功耗降低越有效;在系統

2021-11-11 06:24:53

。彩燈控制把低功耗藍牙模塊內置于LED內,即可通過APP控制燈泡的色彩、亮暗。在智能家居、連鎖酒店、辦公室、飯店等需要燈光控制調節的地方均可以內置低功耗藍牙模塊,改進設備的智能化和時尚化。計算機外設、I

2019-03-18 02:25:12

可選,并能夠以低電流進行備用電池供電。此外,產品還應盡可能地提高響應速度,并具備更多的內部資源。 近日,微芯(Microchip)公司推出的具有多種靈活低功耗休眠模式且工作電流超低的PIC24F

2019-07-10 08:10:06

工藝節點中設計,但是 FD-SOI 技術提供最低的功率,同時可以承受輻射效應。與體 CMOS 工藝相比,28 納米 FD-SOI 芯片的功耗將降低 70%。射頻數據轉換器需要同時具有高帶寬和低功耗,以

2023-02-07 14:11:25

程序使用定時喚醒采樣方式,每隔一段時間喚醒,進行AD采樣。問題在于,如果不使用內部2.5V基準電壓,進入低功耗時候,電流在20uA左右;使用內部2.5V基準電壓,進入低功耗前關閉(ADC12CTL0

2018-06-21 14:54:10

DL-RX809L 基于SOC 的超外差無線接收芯片設計,是一款低功耗、低成本、小體積、帶解碼(學習碼)超外差無線接收模塊。內部集成高性價比無線數據接收芯片及性能優異的低功耗單片機,模塊具有行業超高

2018-07-07 13:33:46

結合采用低功耗元件和低功耗設計技術在目前比以往任何時候都更有價值。隨著元件集成更多功能,并越來越小型化,對低功耗的要求持續增長。當把可編程邏輯器件用于低功耗應用時,限制設計的低功耗非常重要。如何減小動態和靜態功耗?如何使功耗最小化?

2019-08-27 07:28:24

消費電子領域,OEM希望采用FPGA的設計能夠實現與ASIC相匹敵的低功耗。盡管基于90nm工藝的FPGA的功耗已低于先前的130nm產品,但它仍然是整個系統功耗的主要載體。此外,如今的終端產品設計大多

2019-07-15 08:16:56

PCB制造工藝流程是怎樣的?

2021-11-04 06:44:39

你好微芯片的工作人員!我正在從以下鏈接閱讀關于降低功耗的一些技巧的文檔:http://ww1.micro..com/...01146B_.%202.pdfOn TIP#3 Configuring

2020-04-30 09:25:33

SimpleLink?超低功耗 無線微控制

2016-02-25 10:27:27

XLD3011系列是一套采用CMOS工藝實現的三端低功耗高壓電路。它們可以輸出100mA的電流,允許高達28V的輸入電壓。它們有3.0V到5.0V的幾種固定輸出電壓。CMOS技術確保低電壓降和低靜太

2022-01-18 10:09:07

XLD3011系列是一套采用CMOS工藝實現的三端低功耗高壓電路。它們可以輸出100mA的電流,允許高達28V的輸入電壓。它們有3.0V到5.0V的幾種固定輸出電壓。CMOS技術確保低電壓降和低靜態

2020-02-20 15:54:30

什么是納米?為什么制程更小更節能?為何制程工藝的飛躍幾乎都是每2年一次?

2021-02-01 07:54:00

現代化戰爭對吸波材料的吸波性能要求越來越高,一般傳統的吸波材料很難滿足需要。由于結構和組成的特殊性,使得納米吸波涂料成為隱身技術的新亮點。納米材料是指三維尺寸中至少有一維為納米尺寸的材料,如薄膜

2019-08-02 07:51:17

低成本低功耗的同步解調器設計怎么簡單化?

2021-05-20 06:36:50

HAL250低功耗霍爾開關是采?BCD工藝制作的全極低功耗霍爾ic,BCD?藝把雙極?藝和CMOS工藝,DMOS工藝同時制作在同一芯?上。HAL250低功耗霍爾開關綜合了雙極器件高耐壓、強負載的驅動

2021-10-14 11:45:24

關于黑孔化工藝流程和工藝說明,看完你就懂了

2021-04-23 06:42:18

在微功耗場景下,使用RCC是否比低功耗芯片的效率更高?設計例子:單火取電項目,從AC線取電取電,交流220V轉直流12V,再通過DC-DC方案,將12V轉為3.3V供Zigbee工作,該Zigbee

2016-06-17 13:50:42

的默認值,而且設計人員必須能夠在流程中的任何階段修改這些參數。為了解決這個問題,ReShape流程可以根據所用的工藝、特定的芯片類型及芯片內的特定模塊類型提供層次化的配置文件來控制這些設置工作。這樣就消除

2018-11-26 16:21:06

芯片設計解決方案供應公司微捷碼(Magma)設計自動化有限公司近日宣布,已和專為消費性應用提供超低功耗65納米FPGA(現場可編程門陣列)技術的先驅者SiliconBlue科技公司正式簽定技術合作

2019-07-26 07:29:40

結合采用低功耗元件和低功耗設計技術在目前比以往任何時候都更有價值。隨著元件集成更多功能,并越來越小型化,對低功耗的要求持續增長。當把可編程邏輯器件用于低功耗應用時,限制設計的低功耗非常重要。本文將討論減小動態和靜態功耗的各種方法,并且給出一些例子說明如何使功耗最小化。

2019-07-12 06:38:08

給予過高的期望。當然,所選擇的工藝不同,結果也會不同。雙極性器件具有最終決定帶寬 (BW=gm/2πCc) 的更高跨導 (gm)。要弄清楚多低才算低功耗,可以看一下流耗僅為 150nA 的最新 TLV3691。在 1V 以下的工作電壓下,135nW 就是低功耗。

2018-09-13 14:25:14

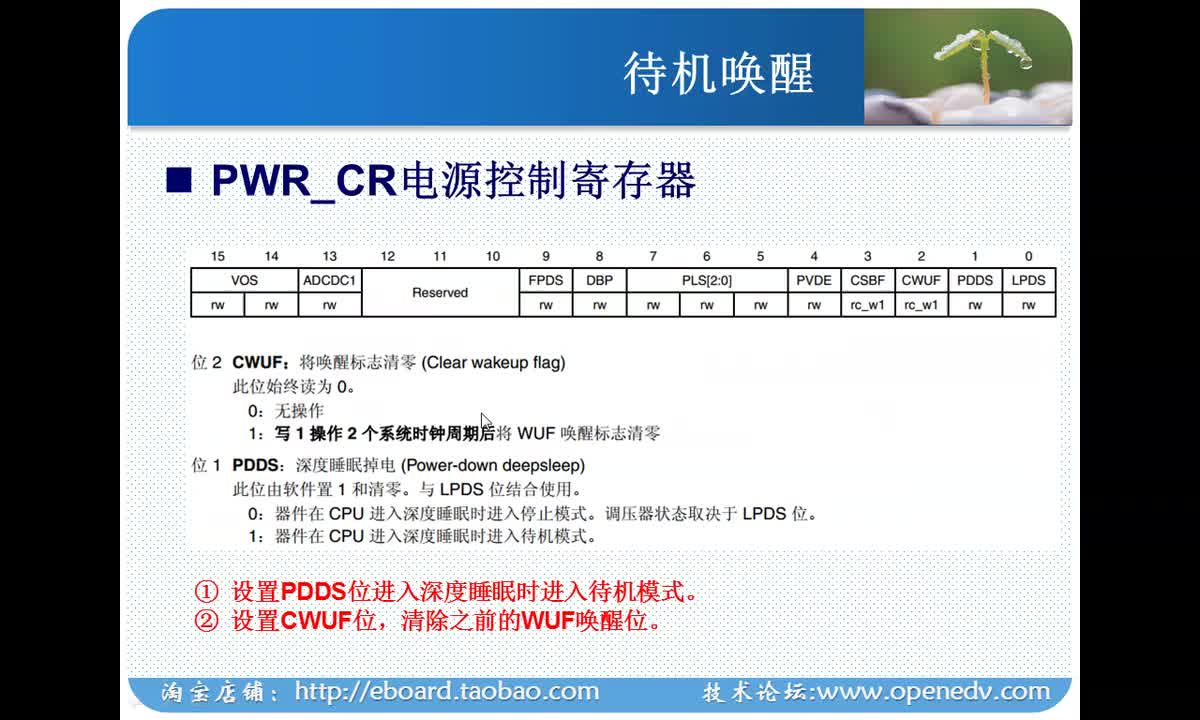

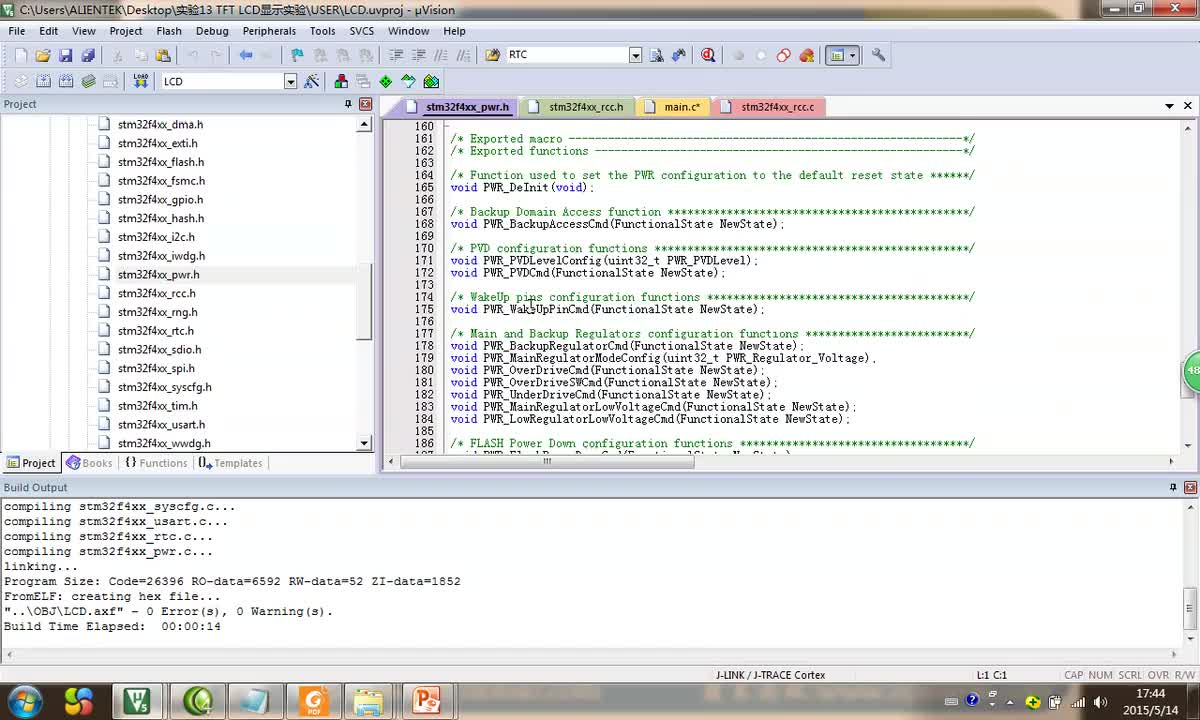

現在電子產品一般都有要求低功耗,不同的MCU,進入低功耗的處理流程可能不一樣,但是大致的流程還是一樣。現對MCU進入低功耗的處理流程大致如下:(1)關閉MCU之外的外設電源,例如:RS485、CAN

2021-11-01 08:10:03

從工藝選擇到設計直至投產,設計人員關注的重點是以盡可能低的功耗獲得最佳性能。Altera在功耗和性能上的不斷創新,那其28nm高端FPGA如何實現功耗和性能的平衡?具體有何優勢?

2019-09-17 08:18:19

量。通過采用基于40nm的半導體最新制造工藝以及創新方法來優化這些復雜的器件,設計人員能夠在單芯片中集成更多的功能。這不但降低了總功耗,而且還可以降低后續工藝節點每一相應功能的功耗。TPACK便是能夠

2019-07-31 07:13:26

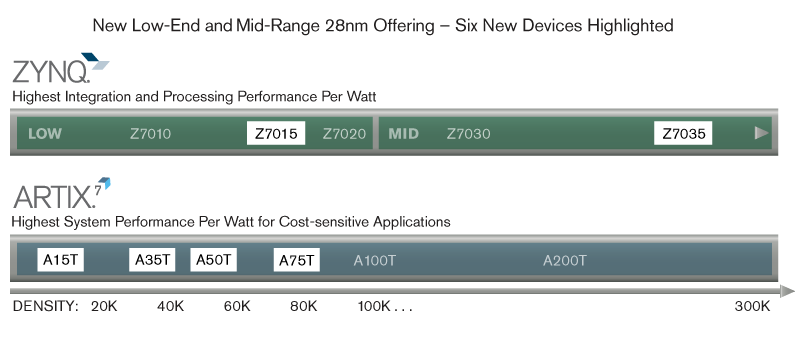

一半,而性能提高兩倍。通過選擇一個高性能低功耗的工藝技術,一個覆蓋所有產品系列的、統一的、可擴展的架構,以及創新的工具,賽靈思將最大限度地發揮 28 納米技術的價值, 為客戶提供具備 ASIC 級功能

2019-08-09 07:27:00

有這個功耗存在。靜態功耗:也稱待機功耗,靜態功耗主要由晶體管的漏電流所導致的功耗;動態功耗:包括開關功耗或者稱為翻轉功耗、短路功耗或者稱為內部功耗。動態功耗影響因素:門寄生電容、時鐘翻轉率、時鐘頻率、供電電壓;降低功耗:應當在所有設計層次上進行,即系統級、邏輯級和物理級,層次越高對功耗降低越

2021-11-11 06:27:30

的市場前景,眾商家摩拳擦掌、躍躍欲試,試圖在產品終端形態和穿戴方式,以及應用效能和實際用途方面推陳出新、搶灘市場,這也就對產品的內核模塊設計提出了更高的要求——小尺寸、低功耗、高工藝、性能穩定、可操作性強

2017-12-12 15:29:01

分享一款巨微MS1581低功耗藍牙無線收發器

2021-01-01 07:46:30

,Vdd為工作電壓。 2 常用的低功耗設計技術 低功耗設計足一個復雜的綜合性課題。就流程而言,包括功耗建模、評估以及優化等;就設計抽象層次而言,包括自系統級至版圖級的所有抽象層次。同時,功耗優化與系統

2016-06-29 11:28:15

復制性決定了指紋鎖是目前所有鎖具中最為安全的鎖種。指紋鎖除指紋識別外,根據國家公安部規定,應當加配應急機械鑰匙。 靈動微推出一款針對指紋鎖應用的低功耗MCU,型號:MM32F031MM32F031

2018-09-06 15:32:41

晶體管管芯的工藝流程?光刻的工藝流程?pcb制版工藝流程?薄膜制備工藝流程?求大佬解答

2019-05-26 21:16:27

`DL-RX809L 基于SOC 的超外差無線接收芯片設計,是一款低功耗、低成本、小體積、帶解碼(學習碼)超外差無線接收模塊。內部集成高性價比無線數據接收芯片及性能優異的低功耗單片機,模塊具有行業

2019-02-22 18:23:05

樣板貼片的工藝流程是什么

2021-04-26 06:43:58

終端節點關閉低功耗模式和開啟低功耗模式,功耗有何區別?功耗相差多少?

2018-05-22 08:42:02

芯片制造全工藝流程詳情

2020-12-28 06:20:25

芯片生產工藝流程是怎樣的?

2021-06-08 06:49:47

功耗及其組成部分,總結降低功耗的若干種常用方案;并重點介紹如何用UPF把低功耗意圖描述出來以及如何用Synopsys工具實現整個流程。 目前常用的低功耗設計的一些方法特別是用power-gating

2020-07-07 11:40:06

直到器件/I藝級的整個數字系統設計流程。每個級別可以達到的低功耗設計效果不同,抽象層次越高則優化的空間越大,效果也越明顯。對于電路的平均翻轉率,通過軟硬件分工有可能降低電路30%的翻轉次數,而通過邏輯

2013-05-16 20:00:33

請詳細敘述腐蝕工藝工段的工藝流程以及整個前道的工藝技術

2011-04-13 18:34:13

stm32進入低功耗模式,必須用中斷來喚醒,現在就是不用這種模式,如何通過程序來降低功耗啊

2019-05-06 18:43:22

貼片電阻的生產工藝流程如何

2021-03-11 07:27:02

要。Altera Cyclone V FPGA通過多種方法幫助設計人員降低系統總成本,設計人員受益的不僅是TSMC的28nm低功耗(28LP)制造工藝,還包括Cyclone V器件系列內置的體系結構,以及

2015-02-09 15:02:06

本資料是關于如何采用低功耗28nm降低系統總成本

2012-07-31 21:25:06

中芯國際(SMIC)和Cadence 共同推出用于65納米的低功耗解決方案Reference Flow 4.0

完全集成的能效型流程令快速、輕松地設計低功耗尖端器件成為可能

2009-10-31 07:48:01 1228

1228 高通攜手TSMC,繼續28納米工藝上合作

高通公司(Qualcomm Incorporated)與其專業集成電路制造服務伙伴-TSMC前不久日共同宣布,雙方正在28納米工藝技術進行密切合作。此

2010-01-13 08:59:23 910

910 臺積電與聯電大客戶賽靈思合作28納米產品

外電引用分析師資訊指出,聯電大客戶賽靈思(Xilinx)3月可能宣布與臺積電展開28納米制程合作;臺積電28納米已確定取得富

2010-01-19 15:59:55 1058

1058 賽靈思宣布采用 28 納米工藝加速平臺開發

全球可編程邏輯解決方案領導廠商賽靈思公司 (Xilinx Inc. ) 今天宣布,為推進可編程勢在必行之必然趨勢,正對系統工

2010-02-23 11:16:21 382

382 統一工藝和架構,賽靈思28納米FPGA成就高性能和低功耗的完美融合

賽靈思公司(Xilinx)近日宣布,為推進可編程勢在必行之必然趨勢,正對系統工程師在全球發布賽靈思

2010-03-02 08:48:51 576

576 根據貫穿整個IC實現流程的集成化低功耗設計技術策略

降低功耗是現代芯片設計最具挑戰性需求之一。采用單點工具流程時,往往只有到了設計流程后期階段才會去考慮降

2010-04-21 10:54:28 651

651

近期,高通公司宣布將推出首款基于28納米工藝的Snapdragon芯片組MSM8960并宣布此芯片組將于2011財年開始出樣。基于28納米工藝的該芯片組采用新的CPU內核為特征,主要針對高端

2010-11-24 09:19:57 1471

1471 本文基于IEEEl801標準Uni-fied Power Format(UPF),采用Synopsys和Mentor Graphics的EDA工具實現了包括可測性設計在內的“從RTL到GDSII”的完整低功耗流程設計。本論文第1部分描述了低功耗技術和術語

2011-03-11 11:33:55 1621

1621

微捷碼QCP提取器已被臺積電(TSMC)納入其季度28納米集成電路(IC)EDA質量檢驗報告中。這次質量檢驗讓設計師們對采用QCP解決臺積電28納米工藝IC日益提高的復雜性問題更有信心。

2011-07-15 08:39:06 877

877 本文采用自頂而目的設計原則,從體系結構到電路實現上分層次探討了時鐘芯片的功耗來源,并采取相應的控制手段實現芯片的低功耗設計。

2011-10-08 11:50:04 2128

2128

在高層次對系統進行功耗佑算和功耗優化是soc設計的關健技術本文首先給出soc設計的特點和流程,然后綜述目前高層次功耗估算和功耗優化的常用方法和技術,重點論述寄存器傳輸級和

2011-12-27 16:42:38 46

46 本白皮書介紹了有關賽靈思 28 nm 7 系列 FPGA 功耗的幾個方面,其中包括臺積電 28nm高介電層金屬閘 (HKMG) 高性能低功耗(28nm HPL 或 28 HPL)工藝的選擇。 本白皮書還介紹了 28 HPL 工藝提供

2012-03-07 14:43:44 41

41 臺積電TSMC已經準備量產28納米工藝的ARM處理器了。TSMC在2011年第四季度開始從28納米芯片獲得營收,目前28納米工藝芯片占有公司總營收的額5%。在今年晚些時候,TSMC將加速28納米芯片的生

2012-04-18 10:22:37 830

830

日前,聯華電子與SuVolta公司宣布聯合開發28納米工藝技術,該工藝將SuVolta的SuVolta的Deeply Depleted Channel晶體管技術集成到聯華電子的28納米High-K/Metal Gate高效能移動工藝。

2013-07-25 10:10:52 1049

1049 中芯國際新款40納米 Reference Flow5.1結合了最先進的Cadence CCOpt和GigaOpt工藝以及Tempus 時序簽收解決方案, 新款RTL-to-GDSII數字流程支持Cadence的分層低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839 2016年2月5日,北京訊——ARM 宣布,從即日起全球晶圓專工領導者聯華電子(UMC)的28納米28HPCU工藝可采用ARM? Artisan? 物理IP平臺和ARM POP? IP。

2016-02-15 11:17:49 896

896 “我們與 Cadence 密切合作開發參考流程,幫助我們的客戶加快其差異化的低功耗、高性能芯片的設計,”中芯國際設計服務中心資深副總裁湯天申博士表示,“Cadence創新的數字實現工具與中芯國際28納米工藝的緊密結合,能夠幫助設計團隊將28納米設計達到更低的功耗以及更快的量產化。”

2016-06-08 16:09:56 2242

2242 28納米以后邏輯工藝開始分岔:立體工藝FinFET由于獲得英特爾與臺積電的主推成為主流,14/16納米都已量產,10納米工藝也有可能在2017年量產;體硅工藝停止在28納米,想增加集成度而又對FinFET開發成本望而卻步的半導體公司另辟蹊徑。

2016-11-04 19:12:11 846

846

臺積電業務開發副總經理金平中指出,臺積電的超低功耗平臺包括55納米超低功耗技術、40納米超低功耗技術、22納米超低功耗/超低漏電技術等,都已經被各種穿戴式產品和物聯網應用采用,同時,臺積電也把超低功耗

2017-12-11 15:03:29 1409

1409 于聯電55納米超低功耗工藝(55ULP)的 PowerSlash 基礎IP方案。智原 PowerSlash 與聯電工藝技術相互結合設計,為超低功耗的無線應用需求技術進行優化,滿足無線物聯網產品的電池長期壽命需求。 智原科技營銷暨投資副總于德洵表示:物聯網應用建構過程中,效能往往受制于低功耗技術。

2018-03-05 15:08:00 5142

5142 位于廈門火炬高新區的聯芯集成電路制造(廈門)有限公司日前傳來喜訊,已于今年2月成功試產采用28納米High-K/Metal Gate 工藝制程的客戶產品,試產良率高達 98%。這是該公司28納米

2018-03-31 15:28:50 11192

11192 賽靈思7系列FPGA產品通過采用新的工藝和新的架構方式,成功將產品的功耗顯著降低。7系列FPGA產品的實測功耗與上一代產品相比,降低了約一半。采用臺積電全新28HPL工藝,賽靈思7系列28nm FPGA產品同時實現了高性能和低功耗。

2018-06-05 13:45:00 4085

4085 Credo 在2016年展示了其獨特的28納米工藝節點下的混合訊號112G PAM4 SerDes技術來實現低功耗100G光模塊,并且快速地躍進至16納米工藝結點來提供創新且互補的112G連接

2018-10-30 11:11:12 5204

5204 近日,華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2018-12-12 15:15:01 2029

2029 12月11日,華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2018-12-14 15:47:30 3159

3159 華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2019-01-01 15:13:00 3780

3780 華虹集團旗下上海華力與聯發科技股份有限公司共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一——基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2019-01-07 14:15:45 3224

3224 低功耗設計是一個整體的概念,意思是它在每個設計層次上都可以進行功耗的優化——算法層次的優化、RTL級代碼的優化、門級網表的優化、版圖布局的優化等等。

2019-02-02 17:20:00 5693

5693 持續創新 28HPL 高性能低功耗工藝,成就跨越全新中低端器件,和 Artix-7 FPGA、Kintex-7 FPGA 及 Zynq-7000 SoC 產品系列的全新低功耗工業速度等級的器件敬請

2019-08-01 09:07:32 3066

3066

28納米與40納米為目前半導體市場上的主流工藝,無論是IP、光罩與晶圓等技術均趨于穩定成熟,成本大幅低于FinFET工藝。

2019-09-19 14:43:29 1446

1446 的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低。目前許多終端市場對可編程邏輯器件設計的低功耗要求越來越苛刻。在消費電子領域,OEM希望采用FPGA的設計能夠實現與ASIC相匹敵的低功耗。 盡管基于90nm工藝的FPGA的功耗已低

2020-10-28 15:02:13 2498

2498 級四個層次按照自頂向下的電路設計方法,在不同設計層次上對功耗進行優化時,改善的程度是不同的,設計層次越高,優化所能達到的效果越好。本論文對各個層次的低功耗設計技術進行了研究和分析,并將系統級總線編碼技術作為

2021-04-13 16:49:37 19

19 現在電子產品一般都有要求低功耗,不同的MCU,進入低功耗的處理流程可能不一樣,但是大致的流程還是一樣。現對MCU進入低功耗的處理流程大致如下:(1)關閉MCU之外的外設電源,例如:RS485、CAN

2021-10-25 11:36:02 18

18 都導通時所引起的功耗。低功耗設計方法對于系統是在低功耗下提高性能,還是高性能下降低功耗,這對采樣什么樣的低功耗技術很關鍵。下圖是基于低功耗反饋的前向設計法,如圖,可以看出五個層次下對系統的功耗進行優化,自頂向下分別對應系統級、行為級、RTL級、邏輯級和物理級。下圖說明了各層次的具體優化方法和優化效果,可以看到層次

2021-11-06 15:51:01 18

18 功耗存在。靜態功耗:也稱待機功耗,靜態功耗主要由晶體管的漏電流所導致的功耗。動態功耗:包括開關功耗或者成為翻轉功耗、短路功耗或者稱為內部功耗;動態功耗影響因素:門寄生電容、時鐘翻轉翻轉、時鐘頻率、供電電壓;降低功耗:應當在所有涉及層次上進行,即系統級、邏輯級和物理即,層次越高對功耗降低越有效;在系統

2021-11-06 17:21:01 14

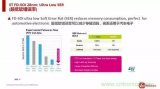

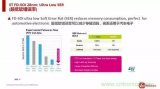

14 低功耗一直是便攜式電子設備的關鍵要求,但近年來,在人工智能、5G、大數據中心、汽車等應用快速發展的推動下,對低功耗的需求已經擴散到更多的終端產品中。

2023-02-14 09:10:59 778

778 無壓燒結銀工藝和有壓燒結銀工藝流程區別如何降低納米燒結銀的燒結溫度、減少燒結裂紋、降低燒結空洞率、提高燒結體的致密性和熱導率成為目前研究的重要內容。燒結銀的燒結工藝流程就顯得尤為重要

2022-04-08 10:11:34 778

778

電子發燒友App

電子發燒友App

評論