最大的優(yōu)點可能是當(dāng)首個 SoC 芯片進入實驗室時就可立即運行嵌入式軟件。

作為基于 FPGA 原型方法的擁護者,有人可能會認為我們只片面地看到了這種方法的優(yōu)點,而對其缺陷視而不見。但那絕非我們的本意。我們這本《基于 FPGA 的原型方法手冊》旨在全面揭示基于 FPGA的原型的利弊,因為最終我們并不想看到有人本來可以使用其他方法更好地達到目的(比如說用基于System C的虛擬原型),卻行進在這種方法的漫漫征途上。

讓我們來更深入地研究一下基于FPGA原型方法的目的和局限性,以及其對于系統(tǒng)級驗證和其他目的的適用性。把重點始終放在原型項目的目的上,讓我們在平臺、IP 使用、設(shè)計導(dǎo)出、調(diào)試及其他設(shè)計方面更容易地做出決策。這樣,我們就能夠通過分析世界上其他原型設(shè)計團隊的案例,從他們的項目中汲取經(jīng)驗。

基于FPGA的原型可滿足不同目的需求

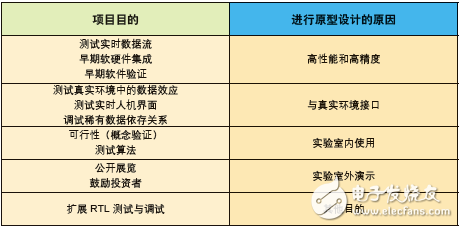

原型設(shè)計不是一個按幾個按鈕就能完成的過程,在它不同的階段需要仔細的關(guān)注和思考。除說明這個過程需要完成的工作和涉及到的專業(yè)知識外,我們還應(yīng)解釋在 SoC 項目中該進行(或者不該進行)原型設(shè)計的原因。在與原型設(shè)計人員多年交談中,我們最常問到的一個問題是“為什么您這么做?”。答案有多種多樣,我們把它們總結(jié)成了表 1 中幾條常見的理由。舉例來說,“真實環(huán)境中的數(shù)據(jù)效應(yīng)”,這可能指的是某個團隊的工作是通過原型設(shè)計得到某個系統(tǒng)全速運行時的模型,并將其與其他系統(tǒng)或外設(shè)相連,目的可能是為了測試對某個新接口標(biāo)準(zhǔn)的合規(guī)情況。他們進行原型設(shè)計的大致理由是“與真實環(huán)境接口”,而且原型設(shè)計也確實在真正的芯片器件面世之前,提供了實現(xiàn)這個目的的最快、最準(zhǔn)確的途徑。

?

表 1 采用基于 FPGA 原型的常見目的與原因

系統(tǒng)了解這些項目的目的和我們進行原型設(shè)計的原因,將有助于我們判斷基于 FPGA 的原型設(shè)計是否能為我們的下一個項目提供幫助。

因此,讓我們探究一下表 1 所述的目的以及基于 FPGA 的原型方法如何能幫助實現(xiàn)這些目的。在許多情況下,我們還會給出真實環(huán)境中的一些實例,筆者藉此提前感謝那些奉獻自己經(jīng)驗、指導(dǎo)他人走向成功的人士。

高性能與準(zhǔn)確度

只有基于 FPGA 的原型才能提供正確測試設(shè)計各個方面所需的速度和準(zhǔn)確度。我們把這個理由放在首位的原因是,雖然項目有許多需要實現(xiàn)的給定目的,但對需要進行原型設(shè)計的團隊來說,這可能是所有理由中最根本的原因。舉例來說,這個團隊的目的可能是驗證某些 SoC 的嵌入式軟件,觀察其在真實硬件上全速運行的情況,但使用原型的根本原因是為了確保高性能與準(zhǔn)確度。我們在虛擬系統(tǒng)中可以在更高的性能水平下驗證該軟件,但我們無法達到使用真實的 RTL 所能實現(xiàn)的準(zhǔn)確度。

實時數(shù)據(jù)流

難以驗證 SoC 的原因之一是因為其狀態(tài)取決于許多變量,包括其之前的狀態(tài)、輸入的次序以及更廣泛的 SoC 輸出系統(tǒng)效應(yīng)(以及可能的反饋)。將 SoC 設(shè)計與系統(tǒng)的其他部分相連并以實時速度運行,可以讓我們立即觀察到實時條件、輸入和系統(tǒng)反饋的變化帶來的效應(yīng)。

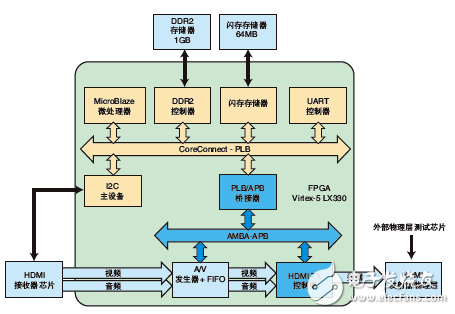

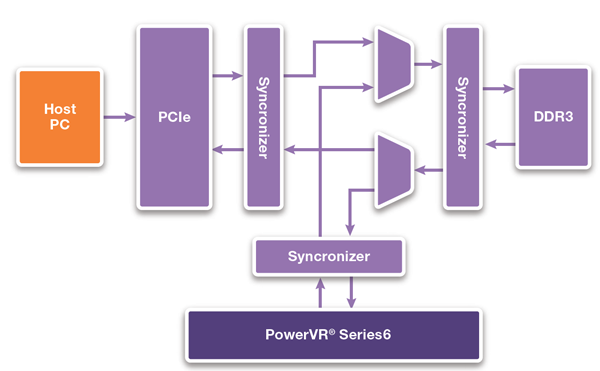

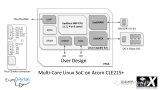

葡萄牙波爾圖市 Synopsys 公司 IP 團隊開發(fā)的 HDMI 原型中的實時數(shù)據(jù)流就是一個很好的例子。在本實例中,高清(HD)媒體數(shù)據(jù)流經(jīng)處理內(nèi)核的原型輸出到高清顯示器上,如圖 1 的方框圖所示。注意方框圖底部顯示的是實時音頻和高清視頻數(shù)據(jù)流,從接收器(從外部源)接收,流經(jīng)原型,輸出到與外部監(jiān)控器相連的實時HDMI PHY 的整個流程。

通過使用投片前的原型,我們可以立即看到和聽到不同的高清數(shù)據(jù)在我們的設(shè)計上的效果,反之亦然。只有采用基于 FPGA 的原型方法才支持這種實時數(shù)據(jù)流,不僅給此類多媒體應(yīng)用帶來極大好處,也能給許多其他要求對輸入數(shù)據(jù)流做出實時響應(yīng)的應(yīng)用帶來諸多裨益。

?

?

圖 1 HDMI 原型方框圖

軟硬件集成

在上述實例中,讀者可能已經(jīng)注意到原型使用了一塊小型 MicroBlazeTM CPU,并備有外設(shè)和存儲器,從而體現(xiàn)了一個 SoC 的所有常見模塊。在這個設(shè)計中,運行在 CPU 上的軟件主要用于加載和控制 A/V 處理。然而,在許多SoC 設(shè)計中,軟件最耗精力。

鑒于軟件已成為 SoC 開發(fā)工作的主體部分,軟件工作在項目日程中占據(jù)關(guān)鍵位置越來越常見。當(dāng) SoC 能夠有效達到量產(chǎn)標(biāo)準(zhǔn)的時候,決定項目實際完成日期的是軟件開發(fā)和驗證工作。在這種情況下,系統(tǒng)開發(fā)團隊如何才能提升軟件開發(fā)和驗證工作的效率呢?要回答這個問題,我們需要查看軟件開發(fā)團隊把時間都花在什么地方。

為軟件開發(fā)建立 SoC 的模型軟件由于自身的復(fù)雜性,很難做到完美。對我們在日常使用計算機的過程中遇到的軟件升級、服務(wù)包和漏洞修補的情況,我們都已經(jīng)司空見慣。但是,具體到嵌入 SoC 中的軟件,這種無休止的軟件改進方法就遇到了障礙。另一方面,相比于通用的計算機軟件而言,與嵌入式軟件互動的系統(tǒng),其設(shè)定的使用模式和環(huán)境條件都更容易確定。而且,為較簡單的系統(tǒng)開發(fā)的嵌入式軟件可以比較簡單,也就更易于全面驗證。

舉例來說,控制車輛子系統(tǒng)或電子玩具的 SoC 比在實時操作系統(tǒng) (RTOS) 上運行許多應(yīng)用和流程的智能手機更容易

進行全面測試。

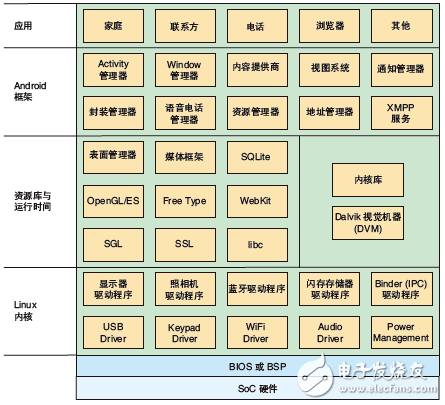

如果我們更加仔細地觀察運行在這類智能手機上的軟件,例如圖 2 所示的 Android 軟件,我們可以看到一種多層布置,這稱為軟件協(xié)議棧。(該圖基于軟件設(shè)計師 Frank Abelson 在其所著的《Unlocking Android》一書中的原始圖。

)

?

?

圖 2 Android 軟件協(xié)議棧

在觀察軟件協(xié)議棧時,我們會發(fā)現(xiàn),協(xié)議棧的最底層——也就是那些最接近硬件的部分,主要是為了滿足將軟件映射到 SoC 硬件上的需求。這就需要對硬件有絕對的了解,甚至包括地址和時鐘周期等。軟件協(xié)議棧最底層的設(shè)計人員往往稱自己為平臺工程師,他們的工作就是準(zhǔn)確描述硬件,以便協(xié)議棧的更高層次能夠識別和重復(fù)使用。這種描述被某些 RTOS 廠商稱為板支持包(BSP),與我們?nèi)粘J褂玫?PC 的基本輸入/輸出系統(tǒng) (BIOS) 類似。

協(xié)議棧從下往上第二層包含 RTOS的內(nèi)核以及將較高層次的軟件與被描述的硬件相連的必要驅(qū)動程序。在這些協(xié)議棧的最底層中,平臺工程師和驅(qū)動程序開發(fā)人員需要在真實的 SoC 或完全準(zhǔn)確的SoC 模型上驗證他們的代碼。這個層面的軟件開發(fā)人員需要全面了解各時鐘周期軟件的行為。

作為軟件開發(fā)人員的另一極,在協(xié)議棧的頂層,我們可以看到用戶空間,在這里可以同時運行多個應(yīng)用,比如像智能電話中的聯(lián)系人管理器、視頻顯示器、互聯(lián)網(wǎng)瀏覽器和實際呼叫的電話子系統(tǒng)。這些應(yīng)用中的每一個都不能直接訪問 SoC 硬件,而且實際上在某種程度上違背了所有硬件考慮事項。這些應(yīng)用依賴運行在協(xié)議棧較低層的軟件代表自己與 SoC 硬件及系統(tǒng)其他部分通信。

我們可以歸納為:在協(xié)議棧的每一層,軟件開發(fā)人員只需要一個足夠準(zhǔn)確的模型來讓自己的代碼認為自己運行在目標(biāo) SoC 上即可。超過必要的準(zhǔn)確度只會讓模型在模擬器上的運行速度下降。實際上,任何層面的 SoC 建模,都要求我們把硬件和協(xié)議棧描述為比當(dāng)前層面更低的一層,以便進行驗證。而且在理想的情況下,我們應(yīng)該只要求夠用的準(zhǔn)確度,以實現(xiàn)最高性能。

舉例來說,協(xié)議棧頂層的應(yīng)用開發(fā)人員可以在真實的SoC或 SoC 模型上測試代碼。在這種情況下,模型的準(zhǔn)確度只要能夠讓應(yīng)用認為自己運行在真正的 SoC 上就足夠,它不需要精確到時鐘周期,也不需要了解硬件的細致結(jié)構(gòu)。但這里速度非常重要,因為在許多情況下有多個應(yīng)用會同時運行,并與真實環(huán)境中的數(shù)據(jù)接口。

這種只為軟件層提供“夠用的準(zhǔn)確度”的建模方法為不同的軟件開發(fā)人員提供了多種不同的建模環(huán)境,供他們在SoC 項目的不同階段使用。可以采用SystemC 這樣的語言進行事務(wù)處理層面的建模,創(chuàng)建出一個準(zhǔn)確度低但速度足夠快的仿真器模型,用來同時運行許多應(yīng)用。如果實時的真實數(shù)據(jù)的處理不是很重要,那么考慮采用虛擬原型方法比較好。

不過,必須完整運行整個軟件協(xié)議棧或必須處理真實環(huán)境中的數(shù)據(jù)時,最適合采用基于 FPGA 的原型方法。

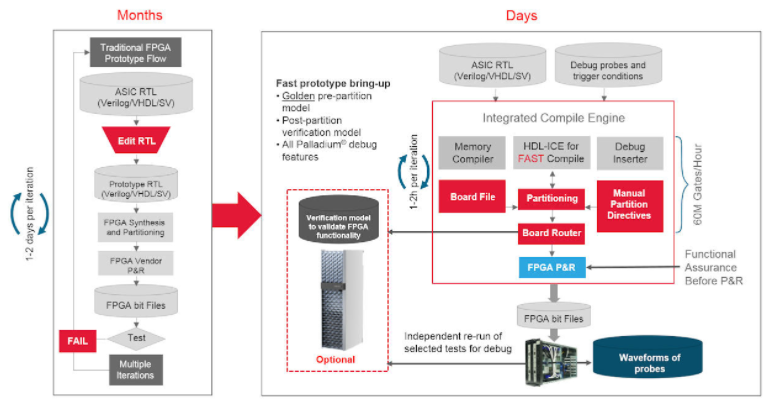

使用原型驗證軟件的實例只有采用基于 FPGA 的原型方法才能夠打破建模方法中準(zhǔn)確度與性能之間內(nèi)在的相互牽制關(guān)系。采用 FPGA,我們既能實現(xiàn)實時的速度,又能以完全的 RTL 周期精度建模。這樣,單個原型不僅能供低層軟件驗證要求的準(zhǔn)確模型使用,又能供高層應(yīng)用開發(fā)人員需要的高速模型使用。實際上,整個 SoC軟件協(xié)議棧都可以在單個基于 FPGA的原型上建模。德克薩斯州奧斯汀市Freescale Semiconductor公司移動產(chǎn)品部的 Scott Constable 及其團隊開展的項目就是采用 FPGA 驗證軟件的一個很好的例子。

Freescale非常想加快 SoC 開發(fā)進程,因為手機市場上產(chǎn)品生命周期短,需要產(chǎn)品盡快打入市場。這不僅是為了贏得競爭,也是為了避免迅速過時。通過分析流程中耗時最多的環(huán)節(jié),F(xiàn)reescale發(fā)現(xiàn)通過加快手機3G協(xié)議測試工作可以帶來最明顯的效果。如果測試工作能夠在流片前完成,F(xiàn)reescale就可以將項目時間縮短數(shù)月。與通常只有一到兩年的產(chǎn)品生命周期而言,這非常重要。

協(xié)議測試是一個復(fù)雜的過程,就算以較高的實時速度進行,也需要一天才能完成。使用 RTL 級仿真需要花上數(shù)年,而在較快的仿真器上運行也要數(shù)周時間,這都不切合實際。采用 FPGA 是因為這是實現(xiàn)必要的時鐘速度,及時完成測試的唯一途徑。

協(xié)議測試需要開發(fā)產(chǎn)品的各種軟件特性,包括硬件驅(qū)動程序、操作系統(tǒng)和協(xié)議棧代碼。雖然如前所述主要的目的是協(xié)議測試,通過使用 FPGA,所有這些軟件開發(fā)工作都能夠在流片前完成,從而大大加快各種最終產(chǎn)品的開發(fā)進度。

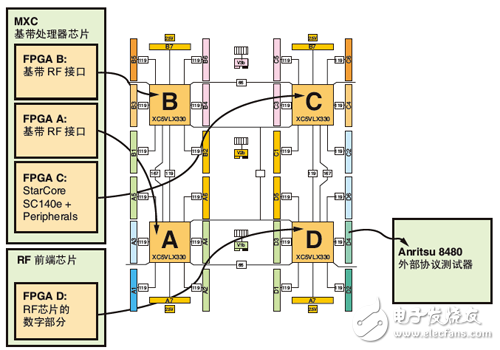

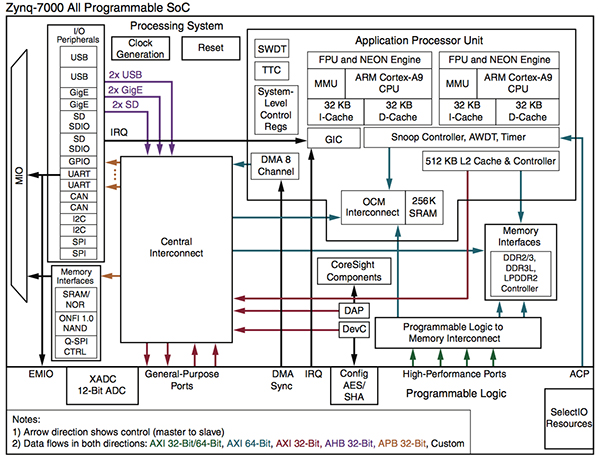

Freescale 構(gòu)建了一個多芯片系統(tǒng)的原型,其中包括一個雙核 MXC2 基帶處理器和一個 RF收發(fā)器芯片的數(shù)字部分。基帶處理器內(nèi)置一個用于調(diào)制解調(diào)器處理的 Freescale StarCore DSP內(nèi)核、一個用于用戶應(yīng)用處理的ARM?926 內(nèi)核,以及 60 多個外設(shè)。

Synopsys HAPS-54 原型板用來實現(xiàn)原型(如圖 3 所示)。該基帶處理器有 500 多萬個 ASIC門,Scott 的團隊使用 Synopsys Certify 工具將其在原型板上劃分給三個賽靈思 Virtex-5FPGA,同時把數(shù)字 RF 設(shè)計布置在第四個 FPGA 中。Freescale 決定不構(gòu)建模擬部分的原型,而是直接從 Antritsu協(xié)議測試盒中以數(shù)字形式提供移動網(wǎng)絡(luò)數(shù)據(jù)。

?

?

圖3 Freescale 的 SoC 設(shè)計在 HAPS-54 原型板上的分區(qū)

較早的內(nèi)核使用的某些設(shè)計技術(shù)對ASIC 來說非常有效果,但對 FPGA 來說卻不太好用。另外,RTL 的一部分是從系統(tǒng)級設(shè)計代碼中自動生成的,由于其過于復(fù)雜的時鐘網(wǎng)絡(luò),對 FPGA 來說也是相當(dāng)不利。因此,必須對 RTL 進行一些調(diào)整,使其更加兼容 FPGA,這樣做的成效非常顯著。

除了能夠加快協(xié)議測試, 到Freescale 的工程師完成首個芯片時,他們還能夠:

?發(fā)布調(diào)試器軟件,且在芯片實現(xiàn)后無需進行大的修改;

?完成驅(qū)動程序軟件;

?在操作系統(tǒng)提示符下引導(dǎo)SoC;

?實現(xiàn)調(diào)制解調(diào)器陣營(modem camp)和注冊。

僅在完成首個芯片后一個月,F(xiàn)reescale 團隊就成功地從這個系統(tǒng)中撥出了第一個移動電話呼叫,把產(chǎn)品開發(fā)進度縮短了6個多月,這非常具有里程碑意義。

如 Scott Constable 所說,“除了加速我們所述的協(xié)議測試目標(biāo)外,我們的 FPGA 系統(tǒng)原型還加快了眾多其他領(lǐng)域的項目進度,再次證明了它的價值。

也許最重要是給開發(fā)人員帶來的不可估量的好處:它能夠讓工程人員盡早參與項目,讓從設(shè)計到軟件到驗證再到應(yīng)用

的所有開發(fā)團隊在芯片完成前半年時間內(nèi)就對產(chǎn)品了如指掌。這種對產(chǎn)品專業(yè)知識認知的進程的加快是難以用甘特圖

(Gantt chart) 來衡量的,卻可能是最有益處的。”

“ 鑒于如此多的優(yōu)勢, 用基于FPGA 的原型解決方案來加快 ASIC 的開發(fā)進程是一件非常自然的事情。我們隨后將這種方法介紹給了 Freescale 網(wǎng)絡(luò)和微控制器部,還將其用于最新 IP驗證、驅(qū)動程序開發(fā)、調(diào)試器開發(fā)和客戶演示。”

這個例子說明基于 FPGA的原型方法能夠給軟件開發(fā)團隊提供什么樣的增值工具,能夠在產(chǎn)品質(zhì)量和項目進程方面帶來怎樣顯著的回報。

接口優(yōu)勢:測試真實條件下的數(shù)據(jù)效應(yīng)很難想象有這樣一種 SoC 設(shè)計可以不遵守輸入數(shù)據(jù)、處理數(shù)據(jù)、生成輸出數(shù)據(jù)的基本結(jié)構(gòu)。實際上,如果我們深入 SoC 設(shè)計,就會發(fā)現(xiàn)無數(shù)的子模塊遵循著同樣的結(jié)構(gòu),直到單個門級。要在這些層級中的每一個層級驗證正確的處理,要求我們提供完整的輸入數(shù)據(jù)集,并觀察處理結(jié)果的輸出數(shù)據(jù)是否正確。對單個門來說,這個工作很簡單,對小型 RTL 模塊來說,也是可能的。但隨著系統(tǒng)日趨復(fù)雜,從統(tǒng)計上來說基本沒有可能確保輸入數(shù)據(jù)和初始條件的完整性,尤其是在有軟件運行在一個以上的處理器的時候。

為了提升傳統(tǒng)驗證方法的效率和覆蓋面,以及應(yīng)對這種復(fù)雜性所帶來的挑戰(zhàn),我們已經(jīng)投入了大量的研究工作和資金。在完整的 SoC 層面,我們需要使用多種不同的驗證方法來覆蓋所有輸入組合并和剔除極端情況下的組合。

最后一點非常重要,因為不可預(yù)測的輸入數(shù)據(jù)能擾亂所有的 SoC 系統(tǒng),即便是精心設(shè)計的關(guān)鍵SoC設(shè)計也難以幸免。與新輸入的數(shù)據(jù)或者輸入數(shù)據(jù)不尋常的組合或序列相結(jié)合的,是非常多的 SoC 可能的前置狀態(tài),可能會使SoC 處于某種無法驗證的狀態(tài)。當(dāng)然,這種情況不一定是什么問題,SoC 可以在無需系統(tǒng)的其他部分干預(yù)的情況下恢復(fù),或者用戶根本就沒有察覺。

但是,不能驗證的狀態(tài)必須在最終芯片中避免,因此我們需要盡可能全面地測試設(shè)計的方法。在設(shè)計的功能仿真過程中,驗證工程師會采用有力的方法,比如受約束隨機激勵和高級測試工具來完成多種測試,旨在達到可接受的測試覆蓋面。但是,完整性仍受驗證工程師選擇的方向和給定的約束條件的限制,并受限于可用于運行仿真的時間。

結(jié)果雖然受約束隨機驗證永遠不可能窮盡,但能夠大大增強我們已經(jīng)測試了所有輸入的組合(包括可能的輸入和極端

情況輸入)的信心。

為了屏蔽極端情況下的組合,我們可以通過觀察真實條件下運行在基于FPGA 原型上的設(shè)計來完善我們的驗證工作。通過將 SoC設(shè)計植入原型,我們能夠以與最終芯片媲美的速度和準(zhǔn)確度來運行設(shè)計,從而在最終的環(huán)境數(shù)據(jù)中進行“浸入式”測試,就如在最終芯片上進行的一樣。

西班牙瓦倫西亞的 DS2 采用基于FPGA 的原型將 SoC 設(shè)計浸入到真實環(huán)境中就是一個很好的例子。

實例:浸入到真實環(huán)境數(shù)據(jù)中

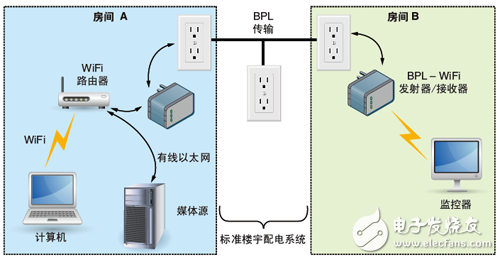

電力線寬帶 (BPL) 技術(shù)一般采用無法檢測的信號來通過輸電線發(fā)送和接收信息。BPL 的一種典型應(yīng)用是將高清視頻從接收器通過輸電線傳輸?shù)绞覂?nèi)的任意一臺顯示器,如圖 4 所示。DS2 的 BPL 設(shè)計核心是復(fù)雜的硬件和嵌入式軟件算法,其可對電力線輸入輸出的高速傳輸信號進行編碼和檢索。這些電力線可能工作在噪聲極高的電氣環(huán)境中,因此開發(fā)工作的關(guān)鍵部分是在各種真實情況下驗證這些算法。

?

?

圖4 WiFi 范圍擴展器采用的電力線寬帶 (BPL) 技術(shù)

DS2 的 BPL 設(shè)計核心是復(fù)雜的硬件和嵌入式軟件算法,其可對電力線輸入輸出的高速傳輸信號進行編碼和檢索。這些電力線可能工作在噪聲極高的電氣環(huán)境中,因此開發(fā)工作的關(guān)鍵部分是在各種真實情況下驗證這些算法。

DS2 的 ASIC 設(shè)計經(jīng)理 Javier Jimenez 說明了基于 FPGA 的原型設(shè)計對他們的用處:“采用穩(wěn)健的驗證技術(shù)開發(fā)可靠的高速通信非常重要。它需要采用不同的通道和噪聲模型進行大量的嘗試,只有基于 FPGA 的原型可幫助我們?nèi)鏈y試算法,在原型上運行設(shè)計的嵌入式軟件。另外,我們還可將原型拿出實驗室,進行廣泛的現(xiàn)場測試。我們可將多個原型放在真正的家居和辦公環(huán)境中,其中部分電氣環(huán)境非常惡劣。我們不能考慮將仿真器系統(tǒng)用于該目的,因為其價格非常昂貴,也不便攜帶。”這種在實驗室外使用基于 FPGA的原型設(shè)計非常有指導(dǎo)意義,因為我們明白打造可靠、便攜的平臺對取得成功非常重要。

對實驗室可行性實驗的優(yōu)勢在項目的初始階段,需要對芯片拓撲、性能、功耗以及片上通信結(jié)構(gòu)做出基本決策。部分決策采用算法或系統(tǒng)級建模工具便可良好執(zhí)行,但也可以采用FPGA 進行某些額外的實驗。這是否是真正基于 FPGA 的原型設(shè)計呢?我們正使用 FPGA 進行某個概念的原型設(shè)計,但這與使用算法或數(shù)學(xué)工具不同,因為我們需要某些可能是由這些高級工具生成的 RTL。一旦進入 FPGA,就可采集早期信息幫助推進算法和最終 SoC 架構(gòu)的優(yōu)化。基于 FPGA 的原型為項目該階段帶來的優(yōu)勢是,可使用更準(zhǔn)確的模型,而且這些模型的運行速度非常快,能夠與實時輸入互動。

這種類型的實驗性原型值得一提,因為它們是在全面的 SoC 項目中使用基于 FPGA 的原型設(shè)計硬件和工具的又一途徑,可為我們的投資帶來更高的回報。

在實驗室外使用原型

基于 FPGA 的原型設(shè)計可用于驗證 SoC 設(shè)計的一個真正獨到之處,是其獨立工作的能力。這是因為 FPGA 可通過閃存 EEPROM 卡或其它獨立介質(zhì)進行配置,無需主機 PC 管理。因此該原型不但可獨立運行,而且還可用于各種環(huán)境下的 SoC 設(shè)計測試,這與其它建模技術(shù)(如需要依賴主機干預(yù)的仿真)提供的環(huán)境儼然不同。

在極端情況下,原型可以完全從實驗室中取出,用于現(xiàn)場真實環(huán)境中。比如將原型安裝在開動的車輛上,研究設(shè)計對外部噪聲、移動、天線場強等條件變化的依賴性。比如,本文作者就曾將移動電話的基帶原型安裝在車輛上,通過公共 GSM 網(wǎng)絡(luò)在移動中撥打電話。

芯片架構(gòu)師與其他產(chǎn)品專家需要與早期客戶互動,展示其算法的重要特性。基于 FPGA 的原型設(shè)計在項目極早期的這個階段可能是非常關(guān)鍵的優(yōu)勢,但這種方法與主流 SoC 原型設(shè)計略有不同。

將基于 FPGA的原型用于實驗室外的另一種極為常見的用途是在商業(yè)展示會上進行新產(chǎn)品功能的預(yù)制造展示。下面讓我們來研究一下英國 BBC 下屬的研發(fā)部門將基于 FPGA 的原型用于實驗室外和商業(yè)展示會的案例。

實例:現(xiàn)實世界中的原型

FPGA 獨立運行的強大功能在英國用來推廣 DVB-T2 的 BBC 研發(fā)項目中得到了充分展現(xiàn)。DVB-T2 是業(yè)界領(lǐng)先的最新開放式標(biāo)準(zhǔn),其可實現(xiàn)通過地面發(fā)射器傳播高清電視。

使用基于 FPGA 的原型的原因和大多數(shù)國際標(biāo)準(zhǔn)一樣,DVB-T2 技術(shù)規(guī)范的完善花費了數(shù)年時間,來自世界各地的研究人員和技術(shù)專家用了 3 萬個工程小時。只有 FPGA 才能高度靈活地滿足開發(fā)過程中不斷變更的需求。該規(guī)范于 2008 年 3 月終稿,并于三個月后在 6 月 26 日以《DVB 藍皮書》的方式發(fā)行。

由于 BBC 在規(guī)范制定的同時就已經(jīng)在使用基于 FPGA 的原型,由 BBC研發(fā)部 Justin Mitchell 帶領(lǐng)的 BBC 實施團隊就能夠為 DVB-T2 開發(fā)一種基于硬件的調(diào)制器和解調(diào)器。該調(diào)制器建立在具有賽靈思Virtex-5 FPGA 的 Synopsys HAPS-51卡基礎(chǔ)之上。該卡連接至 BBC 研發(fā)部設(shè)計的子卡上。該子卡提供一個 ASI 接口,可接收輸入的傳送流。輸入的傳送流隨后傳輸給 FPGA,按 DVB-T2 標(biāo)準(zhǔn)編碼,然后傳回子卡,直接上變頻為UHF。

該調(diào)制器用于業(yè)界首次從現(xiàn)場 TV發(fā)射器傳輸 DVB-T2 標(biāo)準(zhǔn)信號,時間是該規(guī)范發(fā)行的同一天。解調(diào)器也采用 HAPS 作為另一種FPGA 原型的基礎(chǔ),完善了端對端的工作鏈,并在 2008 年阿姆斯特丹的 IBC展會上進行了演示,時間是規(guī)范最終確定后三個月。這是一項不平常的成就,幫助建立了該系統(tǒng)于 2009 年投入使用的信心。

此外, B B C 研發(fā)部還參與了DVB-T2 項目的其它重要部分,包括2009 年 3 月在 Turin 舉辦的非常成功的插拔測試大會。在這次大會上,共有五種不同的調(diào)制器和六種不同的解調(diào)器亮相,在各種模式下協(xié)同工作。BBC原型穩(wěn)健的便攜式構(gòu)造使其成為本次插拔測試大會上的亮點。

Justin Mitchell 對基于 FPGA 的原型評論道:“FPGA 最大優(yōu)勢之一是能夠在從預(yù)備階段到宣布傳輸?shù)倪@段時間里跟蹤規(guī)范的最新變化。根據(jù)規(guī)范的變動迅速對調(diào)制器做出調(diào)整的能力非常重要。很難想出有另一種可如此快速開發(fā)調(diào)制器與解調(diào)器并支持便攜性的技術(shù),其可使調(diào)制器與解調(diào)器獨立應(yīng)用于現(xiàn)場發(fā)射器和公共展會。”

基于 FPGA 原型有何不足?

我們撰寫本文的目的是公正地看待基于 FPGA 原型的優(yōu)勢與局限性,因此在前面談及各種優(yōu)勢之后,我們將在下面介紹部分局限性。

首先最重要的是,F(xiàn)PGA 原型不是 RTL 模擬器。如果我們的目的是編寫一些 RTL,然后盡快在 FPGA 中實施,以查看它是否能工作,那么我們應(yīng)該重新思考所忽略的東西。模擬器有兩個基本組件,可以把它們考慮成引擎和儀表盤。引擎的作用是激勵模型,記錄結(jié)果,而儀表盤的作用則是幫助我們檢驗這些結(jié)果。我們可以以小幅增量運行模擬器,然后通過我們的儀表盤進行調(diào)整;我們可能采用某些非常復(fù)雜的激勵方式,這基本上都是仿真器的工作。基于 FPGA 的原型能夠完成相同的工作嗎?當(dāng)然不能。

FPGA 對運行 RTL“模型”來說確實是一種速度更快的引擎,但當(dāng)我們開始設(shè)置該模型的時候,速度優(yōu)勢就會大打折扣。此外,模擬器的儀表盤部分能夠完整地控制激勵和掌握結(jié)果。我們應(yīng)該思考儀表化 FPGA 的方法,深入了解設(shè)計的功能性,但即便是在這方面最完善的設(shè)計,也只能提供一部分真正能用于 RTL 模擬器儀表盤的信息。因此,該模擬器是用于重復(fù)編寫和評估 RTL代碼更加理想的環(huán)境,因此我們應(yīng)該等到模擬基本完成后,RTL 相當(dāng)成熟后才能將其交付給 FPGA 原型設(shè)計團隊。

基于 FPGA 原型不是 ESL

S y n o p s y s 的 I n n o v a t o r 或Synphony 等電子系統(tǒng)級 (ESL) 工具或算法工具可在 SystemC 中完成設(shè)計,或通過預(yù)定義模型庫進行構(gòu)建。然后,我們不但可在相同的工具中模擬這些設(shè)計,而且還可深入了解其系統(tǒng)級性能,包括運行軟件,在項目初期階段進行軟硬件權(quán)衡。

使用基于 FPGA 原型方法,我們需要 RTL,因此它不太適合研究算法或架構(gòu),因為這兩者通常不采用 RTL 方式表達。對軟件來說,F(xiàn)PGA 原型設(shè)計的優(yōu)勢是在當(dāng) RTL 成熟得可以構(gòu)建硬件平臺的時候,軟件可在更加準(zhǔn)確以及更加真實的環(huán)境中運行。對那些具有天馬行空想法的人來說,可以編寫少量 RTL 在 FPGA 上運行,進行可行性研究。這是一種極少而又非常重要的FPGA 原型設(shè)計的使用方法,但別把它和整個 SoC 的系統(tǒng)級或算法研究混淆在一起。

持續(xù)性是關(guān)鍵

優(yōu)秀的工程師往往會為其工作選擇適當(dāng)?shù)墓ぞ撸珣?yīng)該隨時有一種方法可以將半成品交給他人繼續(xù)完成。我們應(yīng)該能夠在盡量不增加工作量的情況下,將來自 ESL 模擬的設(shè)計移交給基于 FPGA 的原型。此外,部分 ESL 工具還可通過高層次綜合實現(xiàn)設(shè)計,生成 RTL 供 SoC 項目整體使用。基于FPGA 的原型能夠接收該 RTL,并以高周期精度在電路板上運行。但我們需要再次等到 RTL 相對穩(wěn)定下來,這需要等到項目軟硬件分區(qū)和架構(gòu)研究階段完成后。

采用 FPGA 進行原型設(shè)計的原因是什么呢?

當(dāng)前 SoC 是從算法研究人員到硬件設(shè)計人員,乃至軟件工程師和芯片布局團隊等眾多專家的工作結(jié)晶,在項目不斷發(fā)展的同時,各類專家也都有自己的需求。SoC 項目的成功很大程度上取決于上述各類專家所使用的硬件驗證、軟硬件聯(lián)合驗證以及軟件驗證的方法,基于 FPGA 原型設(shè)計可為每一類專家?guī)砀鞣N不同的優(yōu)勢。

對于硬件團隊而言,驗證工具的速度可對驗證吞吐量產(chǎn)生巨大的影響。在大多數(shù) SoC 開發(fā)中,有必要隨項目的成熟運行多次仿真,重復(fù)回歸測試。仿真器和模擬器是用于這類 RTL 驗證的最常用平臺。然而即便使用基于 TLM的模擬與建模,由于長時間的運行,RTL 內(nèi)部或 RTL 與外部激勵物之間的部分互動仍然不能在仿真或模擬中重新創(chuàng)建。因此一些團隊采用基于 FPGA 原型為這種硬件測試提供具有更高性能的平臺。例如,我們可以在近乎實時的條件下運行整個操作系統(tǒng)的引導(dǎo)程序,節(jié)省需要花上數(shù)天才能達到相同目的的模擬時間。

對于軟件開發(fā)團隊而言, 基于FPGA原型可為目標(biāo)芯片提供獨特的流片前模型,能夠在開發(fā)接近尾聲時高速、高度準(zhǔn)確地進行軟件調(diào)試。

對于整個團隊而言,SoC 項目的關(guān)鍵階段是在軟硬件初次結(jié)合的時候。硬件將由最終軟件執(zhí)行,而執(zhí)行方式可能是單純硬件驗證方案難以預(yù)見或預(yù)測的,從而最終將出現(xiàn)新的硬件問題。這在多核系統(tǒng)中或者在那些運行同步實時應(yīng)用的系統(tǒng)中特別普遍。如果這種軟硬件的采用要等到第一個器件制造完畢后,那么毫不夸張地說,到那時再發(fā)現(xiàn)新的缺陷就不太好了。

基于 FPGA原型有助于盡早地將軟件引入具有高周期精度的高速硬件模型。SoC 團隊經(jīng)常告訴我們,F(xiàn)PGA 原型設(shè)計的最大優(yōu)勢就是在第一個器件上市時,系統(tǒng)和軟件都已準(zhǔn)備就緒,當(dāng)天便可運行。

電子發(fā)燒友App

電子發(fā)燒友App

評論