對SoC芯片要進行FPGA原型驗證,假如設計較大,要將SoC中不同功能模塊或者邏輯模塊分別分配到特定的FPGA,那么對SoC的分割策略尤為重要。這一點和大規模的多片FPGA設計有所不同,在設計一個大規模的FPGA產品之前,你可能在一開始就會考慮到如何將不同的功能模塊以及連接方式分別合理的放到不同的FPGA中,各個FPGA之間的連接在設計之初就有考慮。

但是,對于大規模SoC設計要分割到多片的FPGA中,對于出database的邏輯原型工程師而言,顯得有點“措手不及”,因為整體的RTL架構代碼并未考慮在多片FPGA上的實現架構,前端SoC架構以及前端的RTL設計工程師更多考慮的是SoC的實現流程。所以,這一點給原型驗證工程師帶來挑戰,但是我們可以順著以下思路運用相關軟件進行手動分割。

分配高度連接的模塊

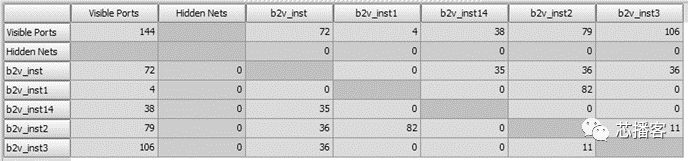

我們期望分割工具可以顯示模塊級互連信息,比如我們在工具中可以選擇設計的層次結構的模塊列表(層次結構之所以非常重要,就是因為在SoC的設計過程中,本身就會遵循以功能為大方向去寫RTL級別的代碼,然后“高內聚,低耦”的思路劃分模塊與層次關系的),然后列表會展示相應的模塊與模塊之間的連接關系。例如以下工具展示的模塊之間的互連: ? ? ?

? ? ?

這里,我們可以立即看到塊b2v_inst1和b2v_inst2共享82個相互連接,但b2v_ints3與塊的頂級IO的連接最多(106)。當用大量相互連接的信號劃分多個塊時,重要的任務是確保這些塊放置在同一FPGA中。如果高度連接的塊被放置在不同的FPGA中,那么我們將需要大量的FPGAIO引腳來重新連接它們。

例如,當使用64位和更大的總線時,分配到不同FPGA中的兩個塊很可能需要數百個額外的FPGA IO。因此,在上面的示例中,我們可能會嘗試先將b2v_inst3分配到一個FPGA中,而b2v_inst1和b2v_ins2可以一起分配到不同的FPGA中,因為它們是相互連接的,但與b2v_ins3幾乎沒有連接。

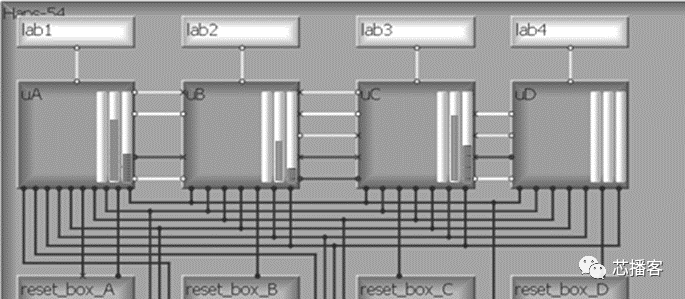

其次,我們期望工具能夠展示大致的FPGA分區信息,當我們手動選擇相關模塊到各FPGA塊的時候,分割軟件可以及時的反饋相關分區FPGA的資源使用情況,以便我們做出最優的手動分割選擇。 ? ? ? ?

? ? ? ?

如果不可能將高度互連的塊放在一起,因為它們溢出了一個FPGA的資源,那么我們將需要降低層次結構級別,并在下一級查找連接較少的塊,并提取要分配到不同FPGA中的塊。通過這種方式,我們仍然可以增加所需的FPGA的IO的數量,但比將更高級別的塊分配到其他地方的情況要少。

如果在此較低級別上沒有這樣的分區,則我們可能會走得更低,但在越來越細的邏輯粒度上指定分區會使分區更可能受到設計迭代的影響,因為這些更細的粒度被不同地優化或重命名。如果我們發現自己必須深入層次結構以找到解決方案,那么最好返回并使用不同的粗略分區在頂層重新啟動。

分配各種設計功能模塊

使用我們對每個塊的面積的估計,我們可以將剩余的設計塊分配給FPGA資源,從最大的塊開始。我們從較大的塊開始,因為這自然會將較小的塊留給稍后的分區過程。然后,隨著FPGA資源可能變得過滿(請記住,50%到70%的利用率是一個很好的目標),我們可以更自由地放置粒度更細、輸入和輸出數量更少的較小塊。

當我們進行分區時,我們希望平衡FPGA的資源使用,同時將利用率保持在可容忍的范圍內,即低于70%的建議值。這將有助于避免長時間的運行時間,并使其更容易達到所需的時間。

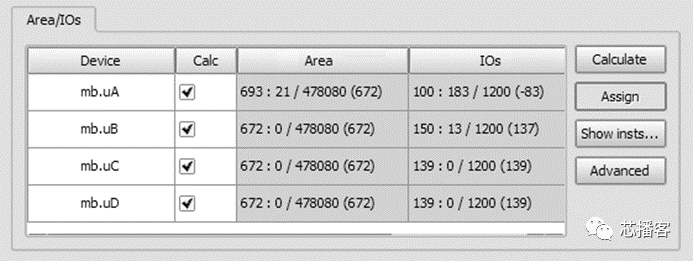

選擇了分區的候選塊后,我們可能會進行嘗試分配,直到找到最佳解決方案,然而,在具有許多FPGA的原型中,這是低效的。我們已經看到,對我們的任務決定進行即時反饋是多么有用。事實上,在分配任務之前獲得反饋更為有用。這使我們能夠提前了解如果將選定塊放置在這樣或那樣的FPGA中,對IO和資源的影響。這種預警稱為影響分析。

這里我們可以看到,我們選擇的塊具有672個邏輯元素的區域,從先前的資源估計中提取。如果我們選擇將塊分配給mb.uB,我們將使FPGA的面積增加672個邏輯元件(總共478080個),并將IO計數增加137個,使其總數達到150個。

我們還可以看到,如果我們將塊分配給mb.uA,那么面積仍將增加相同的數量,但IO需求將減少83個引腳,這可能是因為我們的塊連接到已經分配給mb.uA的一些邏輯。我們可以根據此快速分析選擇mb.uA然后單擊分配。與所有由交互式用戶界面驅動的工具一樣,一旦我們熟悉該方法,就可以使用腳本和命令行。

在放置了主要的分層塊之后,我們可以使用相同的方法用較小的塊來填補空白。對于較小的塊,順序并不那么重要,我們可以通過連接和資源使用等信息來指導。一些工具還提供屏幕上的指導,如基于所需連接的各種權重的“老鼠窩”線,這些線似乎將所選塊拉向最佳FPGA選擇。

在手動完成關鍵任務后,一些團隊將在這個階段改用自動分區。如果這可以在與手動分區器相同的環境中運行,則效率更高。我們只是到達了一個讓我們感到滿意的地步,我們已經控制了我們的關鍵任務,并按下按鈕完成剩下的任務。

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21952瀏覽量

613818 -

SoC芯片

+關注

關注

1文章

635瀏覽量

35633 -

RTL

+關注

關注

1文章

388瀏覽量

60628

原文標題:對SoC進行手動FPGA分區

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

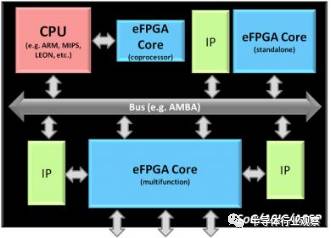

SoC FPGA有哪些作用?

基于FPGA的SOC系統中的串口設計

Altera公司SoC FPGA 簡介

SoC設計中嵌入FPGA(eFPGA)內核實用評估方法

新硬盤進行重新分區的簡單技巧

什么是SoC、SOPC、SoC FPGA?用在什么場景?

基于FPGA的SoC創建方案

如何對SoC進行手動FPGA分區

如何對SoC進行手動FPGA分區

評論