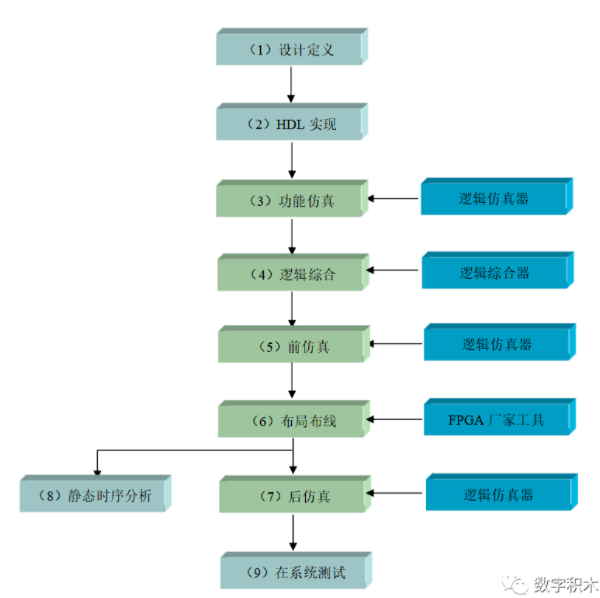

FPGA原型驗(yàn)證流程是確保FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)設(shè)計(jì)正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計(jì)實(shí)現(xiàn)到功能驗(yàn)證的整個(gè)過(guò)程,是FPGA開(kāi)發(fā)流程中不可或缺的一環(huán)。以下是FPGA原型驗(yàn)證流程的詳細(xì)步驟:

首先,進(jìn)行FPGA設(shè)計(jì)。這包括使用專(zhuān)業(yè)的硬件描述語(yǔ)言(如Verilog或VHDL)將硬件原型的功能轉(zhuǎn)化為FPGA代碼。設(shè)計(jì)過(guò)程需要充分考慮硬件資源的利用、性能優(yōu)化以及可維護(hù)性等因素。

接著,將設(shè)計(jì)好的FPGA代碼加載到FPGA開(kāi)發(fā)板或模擬器中。這通常涉及到使用特定的編程工具將代碼編譯并下載到FPGA芯片中。

隨后,進(jìn)行功能驗(yàn)證。驗(yàn)證過(guò)程主要包括測(cè)試FPGA的各個(gè)功能模塊是否按照預(yù)期工作。這可以通過(guò)編寫(xiě)測(cè)試程序、使用調(diào)試工具或構(gòu)建測(cè)試平臺(tái)來(lái)完成。驗(yàn)證人員需要設(shè)計(jì)一系列的測(cè)試用例,覆蓋FPGA設(shè)計(jì)的所有功能和邊界條件,以確保設(shè)計(jì)的完整性和正確性。

在驗(yàn)證過(guò)程中,還需要關(guān)注FPGA與外部接口的通信和數(shù)據(jù)傳輸。這包括驗(yàn)證FPGA與其他硬件組件(如傳感器、執(zhí)行器等)的接口連接是否正確,數(shù)據(jù)傳輸是否穩(wěn)定可靠。

此外,性能驗(yàn)證也是FPGA原型驗(yàn)證流程中的重要環(huán)節(jié)。驗(yàn)證人員需要評(píng)估FPGA設(shè)計(jì)的性能表現(xiàn),包括處理速度、資源利用率、功耗等指標(biāo)。這有助于發(fā)現(xiàn)設(shè)計(jì)中可能存在的性能瓶頸或優(yōu)化空間。

最后,進(jìn)行問(wèn)題定位和修復(fù)。如果在驗(yàn)證過(guò)程中發(fā)現(xiàn)任何功能或性能問(wèn)題,驗(yàn)證人員需要定位問(wèn)題的原因并進(jìn)行修復(fù)。這可能涉及到修改FPGA代碼、調(diào)整硬件資源分配或優(yōu)化接口設(shè)計(jì)等。

總的來(lái)說(shuō),F(xiàn)PGA原型驗(yàn)證流程是一個(gè)復(fù)雜而嚴(yán)謹(jǐn)?shù)倪^(guò)程,它確保了FPGA設(shè)計(jì)的正確性和功能性,為后續(xù)的硬件實(shí)現(xiàn)和應(yīng)用部署提供了堅(jiān)實(shí)的基礎(chǔ)。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21957瀏覽量

614046 -

原型驗(yàn)證

+關(guān)注

關(guān)注

0文章

24瀏覽量

10825 -

開(kāi)發(fā)板

+關(guān)注

關(guān)注

25文章

5507瀏覽量

102252

發(fā)布評(píng)論請(qǐng)先 登錄

驗(yàn)證中的FPGA原型驗(yàn)證 FPGA原型設(shè)計(jì)面臨的挑戰(zhàn)是什么?

高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)設(shè)計(jì)及驗(yàn)證

FPGA原型驗(yàn)證的技術(shù)進(jìn)階之路

華為FPGA設(shè)計(jì)流程指南

FPGA設(shè)計(jì)流程和技術(shù)規(guī)范

關(guān)于FPGA開(kāi)發(fā)板和原型驗(yàn)證系統(tǒng)對(duì)比介紹

為什么SoC驗(yàn)證一定需要FPGA原型驗(yàn)證呢??

如何建立適合團(tuán)隊(duì)的FPGA原型驗(yàn)證系統(tǒng)平臺(tái)與技術(shù)?

什么是FPGA原型驗(yàn)證?如何用FPGA對(duì)ASIC進(jìn)行原型驗(yàn)證

SoC設(shè)計(jì)的IO PAD怎么移植到FPGA原型驗(yàn)證

SoC設(shè)計(jì)的IO PAD怎么移植到FPGA原型驗(yàn)證

從SoC仿真驗(yàn)證到FPGA原型驗(yàn)證的時(shí)機(jī)

為什么SoC驗(yàn)證一定需要FPGA原型驗(yàn)證呢?

fpga原型驗(yàn)證流程

fpga原型驗(yàn)證流程

評(píng)論