高速收發器(SERDES)的運用范圍十分廣泛, 包括通訊、計算機、工業和儲存,以及必須在芯片與芯片/模塊之間、或在背板/電纜上傳輸大量數據的系統。但普通高速收發器的并行總線設計已無法滿足現在的要求。將收發器整合在FPGA中,成為解決這一問題的選擇辦法。

高速設計用FPGA

具備嵌入式數Gb收發器的低功耗FPGA架構,它能讓設計人員利用高生產率的EDA工具提供實體層和邏輯層建構模塊,研發出低成本的小型系統,使得設計師能夠快速解決協議和速率的變化問題,以及為了提高性能和增加新功能時,必須進行設計修改所面臨的重新編程問題,這些迫切需求的靈活性無法在ASIC和ASSP方案中獲得。FPGA提供了一種單芯片解決方案,克服了多芯片方案中的互通作業、布線和功率問題。FPGA中的收發器在克服訊號完整性問題的同時,也能工作在一系列不同的系統或協議環境中。

收發器選擇考慮

收發器的選擇對于要獲得所需的功能設計而言相當關鍵。設計師必須在設計初期階段就分析收發器的功能和性能,并融合頻寬需求、協議、多媒體類型、EMC和互通作業性所決定的設計準則指導選擇。收發器的選擇應該包括規格的符合性驗證;針對抖動、噪音、衰減和不連續性等不利條件下的免疫能力或補償能力;以及應用中的傳輸媒介的類型。根據目前多數組件存在的收發器錯誤紀錄,不難發現將混合訊號收發器整合在數字電路FPGA中僅取得了有限的成功。因此,系統設計師在驗證市場需求時要特別小心,要緊盯著制程、電壓、溫度、核心以及I/O端口,還有硅芯片生產能力等各方面的驗證工作。

評估收發器發射性能的重要工具是眼圖。這是建構在一系列分層PRBS周期上的發射機波形圖量度。透過利用眼狀模板,眼圖可用來顯示特定指針的符合性。如果波形沒有侵占眼圖模板的張開區,通常意味著它符合抖動、噪音和幅度指針。另外,為確保采用隨機性較高的PRBS序列,并將在示波器上擷取的波形采樣數量減到最少,以便它們不會被錯誤地表征較差的PRBS性能,需要一個非常謹慎的方案。

在決定生產制程時,收發器眼圖性能更顯重要。在選擇正確組件時還有下述許多其它因素要考慮。

訊號完整性

對芯片內或芯片與模塊間的通訊來說,無論通訊是透過背板、電纜還是同一電路板上的直接連接,具有嵌入式收發器的FPGA都是理想的選擇。用串行收發器取代平行高速總線可簡化系統設計。在速度高時,并行總線容易遭受干擾和串擾,使得布線相當復雜,有時甚至無法實現。而極具強韌性的串行收發器能簡化布局設計,減少零組件和連接器數量,還能減少PCB層數。在具有相同的總線頻寬時,串行接口的功耗也比并行端口小。

但收發器的更高數據率意味著非理想的傳輸線效應會使布線更加困難。人們普遍采用FR4板進行PCB設計,因為FR4的制造通常采用玻璃纖維和環氧材料,因此具有容易制造、阻燃、易鉆孔、低成本等特點。遺憾的是,當數據率較高時,各層中的銅線會產生‘趨膚效應’,高頻訊號掠過導體的表面,減少了傳導區域,增加了訊號衰減。FPGA設計師通常對數Gb訊息信道中傳送的訊號頻率點了解較少,由于FR4介電材料本身對衰減的影響就極大,在只有幾Gb的數據率上,衰減有可能超過20dB。為了克服這些問題,具有收發器的Stratix II GX FPGA包含了發射機和接收機內部的一些功能,可繼續使用便宜的FR4 PCB材料。

預加重

在數Gb速率時,設計師無法簡單地透過放大訊號解決訊號損失問題,因為這將增大功耗并引起眼圖的閉合。眼圖閉合可能是由發射緩沖的阻抗變壞所引起。在布局上或連接器中,反射能量的強度呈現出近端的不連續性。預加重透過加重任何訊號變化后的第一個數據符號來對發射訊號進行預失真處理,消除訊息信道中脈沖響應的前端過沖和后沿拖尾。

Stratix II GX收發器提供可程序的預加重功能,允許用戶根據傳輸媒介和驅動能力,在3個抽頭中選取每個抽頭13級中的任意一級。最大的預加重為500%,這對張開1.25m Molex GbX背板上速率為6.25Gbps的眼圖來說已經足夠。

接收機均衡

預加重是克服傳輸線損耗的有效方法,不過較高的驅動強度將產生電磁干擾(EMI),并且會使系統容易遭受近場的串擾。張開接收機眼圖的一種替代方案或互補方案是利用接收機均衡技術。在許多應用中利用均衡技術來克服損耗并實現誤碼性能改善是可能的。FPGA中的接收均衡透過在接收機端放大訊號中的高頻分量來補償傳輸損耗,而低頻分量保持不變,這將有效地使訊息信道的s-21插入損耗曲線反轉,使得總訊息信道的頻率響應變得最平坦。均衡技術還可以與預加重技術一起使用,來補償具有特殊挑戰性的鏈路。

Stratix GX II收發器是完全可編程的,無論在設計或應用階段,都能在系統工作過程中進行編程,并能與遠距設備及在工作條件很差的環境下實現互通作業性。這使用戶得以配置均衡器,使其在各種訊息信道長度上工作。最大的均衡水平是17dB,采用4級峰值放大器來實現。這確保了所配置的系統能實現組件速率高達6.375Gbps條件下的最佳訊號完整性,而且還省去了極易傳遞誤碼、功耗大并基于DFE的外來接收機架構。

在設計背板時需考慮的重要因素是收發器的輸出驅動能力,因為最佳訊號完整性設置會由于背板布局、背板插槽數量以及發射卡和接收卡的整體位置不同而變化。由于這種收發器優越的訊號完整性性能,使FPGA能以6.375Gbps的速率在具有連接器的52英寸FR4背板上工作。這種可編程能力和極具強韌性的設計加上低功耗特性,使FPGA可工作在最具挑戰性的背板、電纜、芯片或模塊以及數Gb互連設備中。

可編程驅動能力

某些傳輸線損耗可透過增強差分輸出驅動器的驅動能力,以及在接收機里放大訊號電平來克服。Stratix II GX架構允許設計師在4mA~16mA范圍內選擇驅動能力。實際的Vod輸出驅動電壓電平取決于終端電阻值,對50Ω的傳輸線來說,標準阻值范圍是100Ω。

功率

在所有的高密度背板應用中,功率耗散都是一個主要問題。這些應用的空間有限,功耗和發熱問題必須減到最小,以確保組件溫度在沒有風力冷卻和電源供給情況下仍能保持在所要求的工作范圍內。

為了降低收發器功耗,Stratix II GX采用了專利的PCNL輸出緩沖器技術,該技術使90奈米的PMA(實體媒體連接)層的最大功耗較具備收發器的65奈米FPGA低20%。在40寸FR4串行鏈路上,工作速率達3.1875Gbps時,每四分之一收發器(四個收發器中的一個)所需的功耗為每通道125mW,而工作速率達6.375Gbps時的功耗則為每通道225mW。每四分之一收發器可由1~2個獨立的頻率源來驅動,并具有各自獨立的頻率分配器。頻率和分頻器的結合,能在每四分之一收發器中支持四個不同的數據率,這將大幅降低功耗。利用信道的基本配置能分別判斷信道上的發射機或接收機,進一步節省Stratix II GX收發器的功率。

協議支持

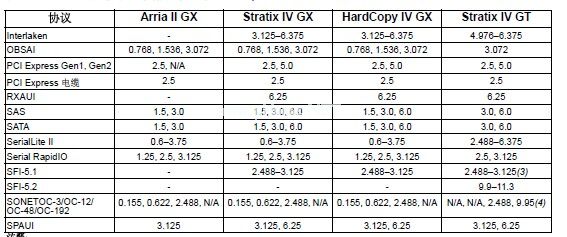

先進的FPGA設計方法能大幅甚至徹底省去設計和驗證FPGA與收發組件間數據信道所需的工作和時間。為了使收發器在滿足特定協議標準時還能具有一定的余量,并能在614Mbps到6.375Gbps的數據速率范圍內正常工作,Stratix II GX收發器經過了精心設計,可提供經驗證的良好性能。支持的協議標準包括PCI Express、串行數字接口(SDI)、XAUI、Gigabit以太網絡、HiGig+、Interlaken、SerialLite II、Serial RapidIO(SRIO)、光纖信道,以及常用的6Gbps長距和短距電界面(CEI-6G-LR/SR)。FPGA基本協議模式能讓架構師在全速率范圍內建構任何符合當地需求或具有知識產權的協議。Stratix II GX系列能滿足嚴格的SONET/SDH OC48/STM16光抖動標準,能整合FPGA的數字和協議功能,以及具備線路接口功能、背板功能、低功耗、低抖動、協議兼容的收發器。

來源同步和平行I/O支持

多數應用要求高速來源同步和并行接口提供數據平衡和管線作業。來源同步I/O(SSIO)是一種允許頻率和數據被分別(即使用LVDS訊號)發送的FPGA界面。作為一種鏈路層接口,SSIO用于將數據從收發器傳送到系統進行處理。來源同步I/O必須支持一個足夠高的數據頻寬,以確保能向收發器連續不斷地提供數據。來源同步I/O部份包含動態相位對齊(DPA)電路,該電路將接收機頻率訊號復制到變化的相位訊號中,并將最近的頻率訊號與進來的數據對齊。DPA能夠使來源同步接口支持更高的數據率,支持增強型數據信道開銷,進一步提高數據率,并實現糾錯、加密和線路編碼。

SSTL和HSTL中具有大量可提供標準I/O連接的平行I/O,適合高性能內存接口、PCI接口等應用。具有收發器的FPGA面臨的挑戰是如何在具有平行I/O、SSIO和FPGA數字邏輯、且收發器所有埠在工作和被評估時可同時切換的驗證標準一致性,以及抗噪音能力和強韌的抖動性能。

FPGA高速收發器設計原則

- FPGA(591969)

相關推薦

賽靈思演示28nm工藝FPGA:80個最大13.1Gbit/秒高速串行收發器

美國賽靈思(Xilinx)2012年4月5日使用28nm工藝制造的FPGA “Virtex-7 X690T”演示了有線通信系統(背板)。該FPGA配備有80個以最大13.1Gbit/秒的速度工作的高速串行收發器“GTH”,已于2012年

2012-04-09 11:13:59 2848

2848

2848

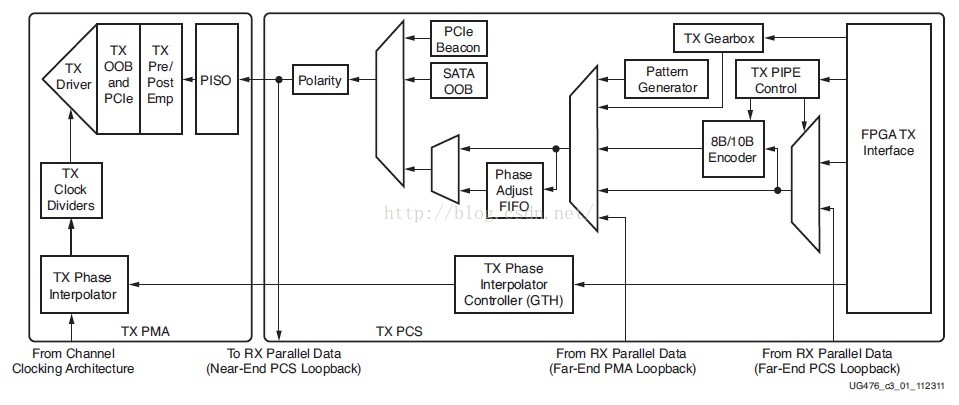

2848FPGA高速收發器的GTX發送端解析

每一個收發器擁有一個獨立的發送端,發送端有PMA(Physical Media Attachment,物理媒介適配層)和PCS(PhysicalCoding Sublayer,物理編碼子層)組成

2020-11-20 11:27:39 5566

5566

5566

5566

FPGA設計之GTP、GTX、GTH以及GTZ四種串行高速收發器

xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH以及GTZ四種串行高速收發器,四種收發器主要區別是支持的線速率不同,圖一可以說明在7系列里面器件類型和支持的收發器類型以及

2020-11-20 12:08:15 17712

17712

17712

17712

7系列收發器與時鐘的關系是什么?

嗨,我想了解7系列收發器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

FPGA GTP收發器設計指導

本帖最后由 QQ3511836582 于 2017-3-29 15:42 編輯

疑問描述測試表明,Spartan-6 FPGA的GTP收發器有可能受到臨近bank中用戶管腳的干擾。因此,賽靈思

2017-03-21 14:34:27

FPGA GTP收發器設計指導

FPGA GTP收發器設計指導疑問描述測試表明,Spartan-6 FPGA的GTP收發器有可能受到臨近bank中用戶管腳的干擾。因此,賽靈思針對bank0和bank2中管腳的使用提出了一些新的建議

2016-08-25 09:46:38

FPGA高速收發器設計要遵循哪些原則?

高速收發器(SERDES)的運用范圍十分廣泛,包括通訊、計算機、工業和儲存,以及必須在芯片與芯片/模塊之間、或在背板/電纜上傳輸大量數據的系統。但普通高速收發器的并行總線設計已無法滿足現在的要求。將收發器整合在FPGA中,成為解決這一問題的選擇辦法。FPGA高速收發器設計時,我們需要注意哪些事項呢?

2019-08-07 06:26:42

FPGA固件開發-設備收發器模塊的數據訪問狀態實現

數據訪問狀態的功能簡單地說就是中斷監測和數據收發。每次系統復位后 FPGA 會自動配置 PDIUSBD12 器件,配置完成之后設備收發器模塊會處于空閑狀態(TS_IDLE)。PDIUSBD12 器件

2018-11-27 09:20:08

收發器

、體積小、無中繼、傳輸距離長等優點得到了廣泛的應用,光纖收發器正是利用了光纖這一高速傳播介質很好的解決了以太網在傳輸方面的問題。那么,我們對這個名詞也來做個解釋吧。光纖收發器,是一種將短距離的雙絞線

2014-04-30 17:28:08

收發器的每項參數與其在實際應用中的意義

CAN收發器是連接CAN控制系統與CAN總線網絡的橋梁,當選型CAN收發器時應該注意哪些參數?本文將帶大家深入的了解收發器的每項參數與其在實際應用中的意義。

2020-12-18 07:16:27

高速CAN收發器MCP2551電子資料

概述:MCP2551是MACROSHIP生產的一款高速CAN收發器。可作為CAN協議控制器和物理總線接口。MCP2551可為CAN協議控制器提供差分收發能力,它完全符合ISO-11898標準,包括能滿足24V電壓要求...

2021-04-20 06:50:57

CAN收發器有什么特點?

在CAN通信中,收發器起到了十分相當特別的作用。目前市面的收發器型號也是不計其數,本文則是根據收發器的發展,簡單介紹幾款收發器的特點。很多年前,NXP的CAN收發器幾乎在每一個CAN節點上都看的到,當時最常見的型號就是PCA82C250。

2019-09-03 06:04:44

Cyclone IV 收發器體系結構

在低成本的 FPGA 中,Cyclone? IV GX 器件內嵌多達八個全雙工收發器,運行在 600Mbps 到 3.125 Gbps 的串行數據速率上。 表 1-1 列出了 Cyclone IV GX 收發器通道所支持的串行協議信息。

2017-11-14 10:54:41

DA PHS射頻收發器芯片怎么設計?

微電子(RDA)公司開發出基于全新RF收發結構的單芯片收發器及集成天線開關的高效率功放模塊。本文介紹RDA PHS射頻收發器芯片的設計方法。

2019-09-20 07:46:19

GTX收發器,讀取速度低于500Mbps怎么辦?

嗨,我們計劃在不同線路速率的高速收發器線路上接收數據,最低為400Mbps。接收器規范提供的最小線速率為500 Mbps。有沒有辦法使用400Mbps流使用收發器(例如通過過采樣,減少時鐘分頻器)?目前我們在收發器外使用過采樣,但這阻止我們使用內部8b10b解碼器和逗號對齊邏輯。謝謝,馬蒂亞斯

2020-08-12 06:39:36

RS-485自動收發型收發器工作原理揭秘

RS-485總線是半雙工的通信總線,因此通常需要MCU控制RS-485收發器的收發狀態。為節省MCU的I/O資源,RS-485自動收發型收發器應運而生,但該類收發器或多或少會遇到一些應用問題,這一類問題該如何解決?本文將從工作原理為你揭曉。

2019-07-12 07:37:06

SFP收發器向導怎么設置?

我需要能夠使用SFP收發器。我想使用收發器向導,但我不知道選擇哪些選項。我不確定我的轉賬率是多少。我知道我需要使用的時鐘大約是600MHz。我還需要能夠從此收發器恢復時鐘。收發器是否有輸出時鐘?謝謝你的幫助。

2020-04-07 14:39:32

WiFi收發器的電源和接地設計

。考慮到實際設計中PLL雜散信號對于電源耦合、接地和濾波器元件的位置非常敏感,本文著重討論了有關PLL雜散信號抑制的方法。為便于說明問題,本文以MAX2827 802.11a/g收發器的PCB布局作為參考設計。WiFi收發器的電源和接地設計:[hide] [/hide]

2011-12-06 16:28:08

XILINX收發器問題的解決

我正在研究使用高速收發器接收部分的定制電路板。所有四個接收器的參考時鐘相同,為125 MHz。我從焦平面陣列(FPA)接收數據并使用8 / 10b編碼。我可以讓FPA重復顯示空白行(字符1FFD

2020-05-05 11:39:41

什么是用于RF收發器的簡單基帶處理器?

挑戰。這些收發器可為模擬RF信號鏈提供數字接口,允許輕松集成到ASIC或FPGA,進行基帶處理。基帶處理器(BBP)允許在終端應用和收發器設備之間的數字域中處理用戶數據。

2019-09-19 06:20:59

介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述GTX/GTH收發器時鐘

2021-11-11 07:42:37

使用一個收發器的Txoutclk為兩個收發器配備Txusrclock嗎?

嗨,我有2個靜態配置的GTX收發器用于HD-SDI操作。我可以使用一個收發器的Txoutclk為兩個收發器配備Txusrclock嗎?通過這種方式,我可以只用1個Txusrclock為FPGA邏輯

2020-08-19 07:43:50

關于FPGA如何連接CAN收發器?

我之前在CSDN上查到的資料都顯示FPGA需要連接一個獨立CAN控制器,如SJA1000再去連CAN收發器。請問我能直接把FPGA的引腳直接連在CAN收發器的TX、RX上嗎?如果不能原因又是什么?

2018-10-10 09:25:39

具有高速CAN收發器的MC33907電源系統基礎芯片的應用

具有高速CAN收發器的MC33907電源系統基礎芯片的典型應用。 33907_8器件是多輸出,電源,集成電路,包括HSCAN收發器,專用于汽車市場

2020-05-22 15:58:32

利用IBERT核對GTX收發器板級測試

和GTX收發器的動態重新配置端口屬性,還包括通信邏輯,以允許設計在運行時通過JTAG進行訪問。

IBERT工具用于對Xilinx FPGA芯片的高速串行收發器進行板級硬件測試。通過IBERT可以獲取誤碼率

2023-06-21 11:23:12

如何在FPGA和ASIC設計中結合高速USB功能

ASIC系統。 使用USB協議棧知識產權(IP)及外部收發器 在第一種方法中,我們可以在FPGA或ASIC中實現SIE(見圖3)。圖3 FPGA + USB協議棧IP + USB收發器 SIE IP

2012-11-22 16:11:20

如何選擇合適的FPGA千兆位收發器?

選擇合適的千兆位收發器(GT)是通信和實時處理領域尤其需要重點考慮的設計事項,但特定的市場領域可能會存在太多的標準、協議或使用模型。有時針對某一種應用就會涉及到好幾種標準,為了選擇最適合的千兆位收發器,必須對各種協議的最新發展情況了如指掌。

2019-10-31 06:57:54

展望未來英特爾FPGA設計,介紹新型224G PAM4收發器

`FPGA 的全稱是“現場可編程門陣列”,而能夠以較低的功耗、將信號高速引入或推出的收發器,將是該領域在未來很長一段時間內的一個主戰場。據悉,FPGA 有望迎來一個可充編輯邏輯的終極功能世界,通過

2020-09-02 18:55:07

常見CAN收發器分為哪幾種

是S32K116的FlexCAN外設,收發器是TJA1043T,兩端的電阻由主機廠提供,我們的OBU中不加電阻。常見CAN收發器分為三種:?高速CAN,最高速率1M/bps?低速/容錯CAN,最高速率125K/bps?單線CAN,最高速率33.3K/bps接法和物理信號如下圖所示:Quipass

2022-01-10 07:54:45

求助FPGA高速串行收發器,輸出12.5Gbps的信號要用什么電平 ...

求助FPGA高速串行收發器,輸出12.5Gbps的信號要用什么電平輸出28.5Gbps的信號要用什么電平?

2014-11-10 09:12:51

請問7系列FPGA收發器向導v2.3 GTX名稱不正確的原因?

你好我試圖在KC705板上使用收發器來生成比特流。我正在使用Vivado 2012.3和7系列FPGA收發器向導v2.3。我之前使用過具有不同傳輸者名稱的IBERT核心。IBERT收發器名稱類似于

2020-07-28 10:29:31

請問能用FPGA直接連接CAN收發器嗎?

我之前在CSDN上查到的資料都顯示FPGA需要連接一個獨立CAN控制器,如SJA1000再去連CAN收發器。請問我能直接把FPGA的引腳直接連在CAN收發器的TX、RX上嗎?如果不能原因又是什么?

2018-10-10 09:05:37

采用AD9361高性能高度集成的RF收發器

AD-FMCOMMS2-EBZ,評估板是一款高速模擬模塊,旨在展示AD9361,這是一款高性能,高度集成的RF收發器,適用于RF應用,如3G和4G基站和測試設備應用,以及軟件定義的無線電。其可編程性

2019-07-04 14:15:44

TJA1042高速CAN 收發器

關鍵詞 TJA1042、高速、低功耗、CAN 收發器摘 要TJA1042 是一款高速CAN 收發器,是CAN 控制器和物理總線之間的接口,為CAN 控制器提供差動發送和接收功能

2009-11-10 13:50:18 364

364

364

364基于MICRF005的高速無線UHF收發器原理及應用

MICRF005芯片是Micrel公司生產的一種高速無線UHF收發器?熏是一款單芯片OOK收發器,可用于遠距離低功率無線設備中單向和雙向無線連接。MICRF0

2010-11-30 17:15:51 26

26

26

26基于FPGA的高速時鐘數據恢復電路的實現

基于FPGA的高速時鐘數據恢復電路的實現

時鐘數據恢復電路是高速收發器的核心模塊,而高速收發器是通信系統中的關鍵部分。隨著光纖在通信中的應用,信道可以承載

2009-10-25 10:29:45 3626

3626

3626

3626

選擇合適的FPGA千兆位收發器至關重要

選擇合適的FPGA千兆位收發器至關重要

選擇合適的千兆位收發器(GT)是通信和實時處理領域尤其需要重點考慮的設計事項,但特定的市場領域可能會存在太多的標準、

2009-11-04 10:05:02 467

467

467

467

采用帶有收發器的全系列40-nm FPGA和ASIC實現創新

采用帶有收發器的全系列40-nm FPGA和ASIC實現創新設計

人們對寬帶服務的帶寬要求越來越高,促使芯片供應商使用更多的高速串行收發器。因此,下一代應用采

2010-02-04 11:06:19 879

879

879

879

TJA1043新一代高速CAN總線收發器

TJA1043新一代高速CAN總線收發器

恩智浦半導體推出了新一代的高速CAN總線收發器-TJA1043,它在電磁兼容(EMC)和靜電放電(ESD)性能上有顯著提高。

2010-05-10 11:01:21 7709

7709

7709

7709PDN設計和FPGA收發器性能

面向收發器(SERDES) FPGA 的PDN 設計對電源有嚴格的要求,需要干凈的電壓源。雖然低功耗應用中通常采用低泄漏(LDO) 線性穩壓器,但這一方法必須仔細的隔離電壓源。電路板設計人員在這

2011-05-11 18:29:41 57

57

57

57Xilinx推出UltraScale FPGA收發器設計

了解如何在您的 ?UltraScale? FPGA? 設計中部署串行收發器。了解并利用串行收發器模塊的特性,如 ?8B/10B? 和 ?64B/66B? 編碼、通道綁定、時鐘校正和逗點檢測。其它專題

2017-02-09 08:04:41 327

327

327

327FPGA中RocketIO GTP收發器的高速串行傳輸實現方案

提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收發器設計的一個高速串行傳輸實現方案,詳細闡述了硬件設計要點和軟件實現概要,系統實測表明,該方案能在某信號處理系統兩個板卡之間穩定地進行1.6 Gb/s的數據傳輸,誤碼率優于10e-12,傳輸距離大于1米。

2017-11-21 10:16:00 7689

7689

7689

7689比較 Xilinx? Virtex?-7FPGA GTH收發器和Altera Stratix V GX收發器的均衡能力

設計人員呼吁提升10G+ 芯片到芯片和背板性能, 依賴接收機均衡來補償信號失真。觀看視頻, 并排比較 Xilinx? Virtex?-7 FPGA GTH 收發器 和 Altera Stratix V GX 收發器的均衡能力。

2018-05-23 15:47:00 3974

3974

3974

3974

基于MCP2561/2下的高速 CAN 收發器

MCP2561/2 是 Microchip 的第二代高速 CAN 收發器。

它可用作 CAN 協議控制器與兩線制 CAN 物理總線之間

的接口。

2018-06-28 09:23:00 23

23

23

2340-nm收發器FPGA和ASIC系列的特點

您意識到對高速收發器、更高的數據速率和帶寬的需求越來越強烈了嗎? 您是否希望“以少勝多”呢? 請觀看這一新視頻,了解全系列收發器FPGA和ASIC怎樣滿足這些需求,為業界提供最全面的收發器定制邏輯

2018-06-22 01:18:00 2817

2817

2817

2817高速ADC與高速串行收發器

經理。我從事FPGA工作已經有12年了。他們中后5人的主要工作是高速串行收發器應用。

我們今天在這里演示新的Linear Technology LTC2274模數轉換器怎樣與具有嵌入式串行收發器

2018-06-20 05:28:00 4215

4215

4215

4215

Virtex UltraScale+ FPGA收發器的演示

該視頻演示了具有32.75G背板功能的Virtex?UltraScale+?FPGA,功率優化的收發器。

該收發器具有同類最佳的發送抖動和第三代客戶驗證的自適應接收器均衡功能......

2018-11-28 06:39:00 2161

2161

2161

2161如何在spartan-6 FPGA中使用GTP收發器的詳細資料說明

本文檔介紹如何在Spartan?6 FPGA中使用GTP收發器。?spartan-6 FPGA GTP收發器簡稱為GTP收發器。

?gtpa1_dual是實例化原語的名稱,它實例化一組

2019-02-15 14:42:47 27

27

27

27virtex-6 FPGA GTH收發器的用戶指南資料免費下載

本章介紹virtex-6 FPGA GTH收發器向導,并提供相關信息,包括其他資源、技術支持和向xilinx提交反饋。向導自動執行創建HDL包裝器的任務,以配置virtex-6設備中的高速串行GTH收發器。

2019-02-20 09:35:45 4

4

4

4如何使用電源管理系統使FPGA收發器的容差保持很小

ADI Guneet Chadha演示如何使用電源系統管理使FPGA內核或I/O(例如:高速收發器)的電源輸出電壓(1V)保持在很小的容差范圍內(0.25%)還顯示了“如何確定電源裕量”

2019-07-24 06:15:00 2098

2098

2098

2098基于XilinxVirtex?-6FPGA 11.18 Gbps收發器的高速互操作性

和AFCT-701SDZ 10 Gbs以太網SFP +收發器產品與具有自適應DFE的XilinxVirtex?-6FPGA 11.18 Gbps收發器的高速互操作性。 Xilinx產品:Virtex-6 HXT

2021-04-14 11:53:31 4122

4122

4122

4122

工業級光纖收發器的選購原則及使用注意事項

此外還有單纖工業級光纖收發器和雙纖工業級光纖收發器,內置電源工業級光纖收發器和外置電源工業級光纖收發器以及網管型工業級光纖收發器和非網管型工業級光纖收發器。

2020-11-17 14:21:23 4508

4508

4508

4508Xilinx 7系列FPGA收發器架構之硬件設計指導(一)

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述 GTX/GTH收發器時鐘

2021-11-06 19:51:00 35

35

35

35如何區分單纖收發器與雙纖收發器

單纖收發器是指采用的是單模光纜,單纖收發器是只用一根芯,兩端都接這根芯,兩端的收發器采用不同的光波長,所以能在一根芯里傳輸光信號。

2023-03-16 14:24:33 1050

1050

1050

1050

如何計算高速RS485收發器的功耗?

如何計算高速RS485收發器的功耗? 高速RS485收發器是一種常見的通信設備,用于對串口數據進行收發。對于高速RS485收發器,我們需要了解它的功耗計算方法,以便在使用過程中合理計劃電源供應

2023-10-31 14:37:15 554

554

554

554 電子發燒友App

電子發燒友App

評論