小編最近在做邏輯綜合時(shí),總在Verilog HDL以及SDC內(nèi)見到SERDES時(shí)鐘以及相關(guān)約束,為了揭開電串行器/解串器Serdes的神秘面紗,小編查閱了相關(guān)資料和論文,并在此文中對(duì)SERDES進(jìn)行介紹討論,同時(shí)介紹一種采用光電集成技術(shù)的,即采用光SerDes而非電SerDes的高速收發(fā)器。

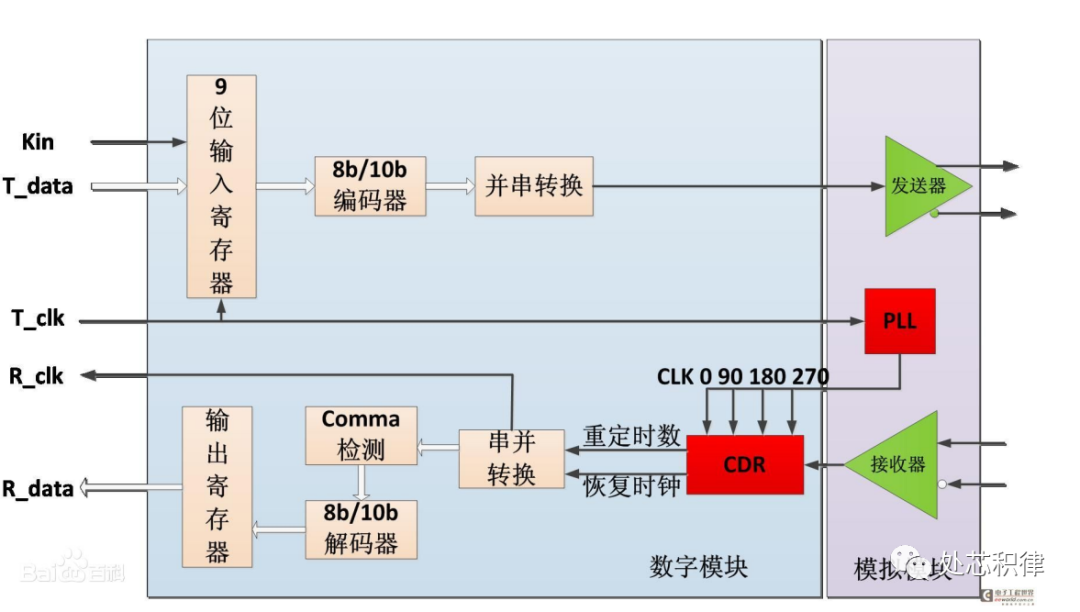

圖1 簡單的串行器/解串器Serdes的架構(gòu)圖(來源百度百科)

SerDes簡介

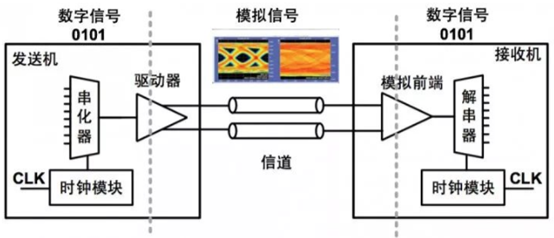

首先我們要了解什么是SerDes,SerDes的應(yīng)用場景又是什么呢?SerDes又有哪些常見的種類?做過FPGA的小伙伴想必都知道串口,與并行傳輸技術(shù)相比,串行傳輸技術(shù)的引腳數(shù)量少、擴(kuò)展能力強(qiáng)、采用點(diǎn)對(duì)點(diǎn)的連接方式,而且能提供比并行傳輸更高帶寬,而SerDes的主要作用就是把并行數(shù)據(jù)轉(zhuǎn)化成為串行數(shù)據(jù),或者將串行數(shù)據(jù)轉(zhuǎn)化為并行數(shù)據(jù)的“器件”。

SerDes的全稱是SERializer(串行器)/DESerializer(解串器),這種主流的高速的時(shí)分多路復(fù)用(TDM),點(diǎn)對(duì)點(diǎn)的串行通信技術(shù)可以充分利用通信的信道容量,提升通信速度,進(jìn)而大量的降低通信成本。目前,商用基于SerDes架構(gòu)的通信協(xié)議最高可實(shí)現(xiàn)單通道56Gbps(好像已經(jīng)可達(dá)112Gbps)的速率,在未來高帶寬、低成本的應(yīng)用領(lǐng)域會(huì)越來越廣泛。

實(shí)際上PCIE,JESD204B等復(fù)雜協(xié)議都是基于SerDes協(xié)議,常見的電SerDes就PCIE等協(xié)議來說,更接近物理層,所以SerDes通常又被稱之為物理層(PHY)器件。正是因?yàn)镾erDes的強(qiáng)電氣屬性,使得Serdes具有以下優(yōu)點(diǎn):

1. 減少布線沖突(非獨(dú)立時(shí)鐘嵌入在數(shù)據(jù)流中,解決了限制數(shù)據(jù)傳輸速率的Signal時(shí)鐘的Jilter問題); 帶寬高 ; 2. 引腳數(shù)目少; 3. 抗噪聲、抗干擾能力強(qiáng)(差分傳輸); 4. 降低開關(guān)噪聲; 5. 擴(kuò)展能力強(qiáng); 6. 更低的功耗和封裝成本;

根據(jù)SerDes的結(jié)構(gòu)的不同可以將其分為四類:

并行時(shí)鐘SerDes:將并行寬總線串行化為多個(gè)差分信號(hào)對(duì),傳送與數(shù)據(jù)并聯(lián)的時(shí)鐘。這些SerDes比較便宜,在需要同時(shí)使用多個(gè)SerDes 的應(yīng)用中,可以通過電纜或背板有效地?cái)U(kuò)展寬總線;

8B/10B編碼SerDes(最常見的結(jié)構(gòu)):將每個(gè)數(shù)據(jù)字節(jié)映射到10bit代碼,然后將其串行化為單一信號(hào)對(duì)。10位代碼是這樣定義的:為接收器鐘恢復(fù)提供足夠的轉(zhuǎn)換,并且保證直流平衡(即發(fā)送相等數(shù)量的‘1’和‘0’)。這些屬性使8B/10B編碼SerDes 能夠在有損耗的互連和光纖傳輸中以較少的信號(hào)失真高速運(yùn)行;

嵌入式時(shí)鐘SerDes:將數(shù)據(jù)總線和時(shí)鐘串化為一個(gè)串行信號(hào)對(duì)。兩個(gè)時(shí)鐘位,一高一低,在每個(gè)時(shí)鐘循環(huán)中內(nèi)嵌串行數(shù)據(jù)流,對(duì)每個(gè)串行化字的開始和結(jié)束成幀,并且在串行流中建立定期的上升邊沿。由于有效負(fù)載夾在嵌入式時(shí)鐘位之間,因此數(shù)據(jù)有效負(fù)載字寬度并不限定于字節(jié)的倍數(shù);

位交錯(cuò)SerDes:將多個(gè)輸入串行流中的位匯聚為更快的串行信號(hào)對(duì)。

SerDes支持非常多的的主流工業(yè)標(biāo)準(zhǔn),比如Serial RapidIO ,F(xiàn)iberChannel(FC),PCI-Express(PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-GbEthernet(XAUI),Infiniband 1X,4X,12X等。

SerDes結(jié)構(gòu)

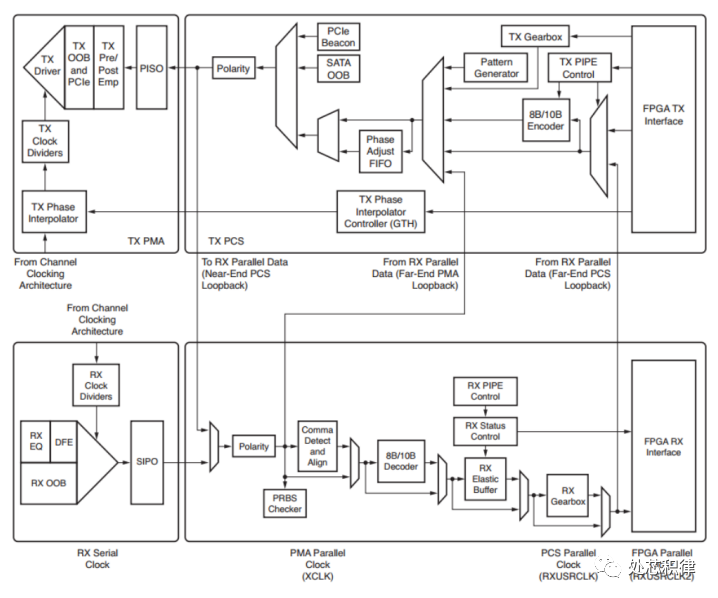

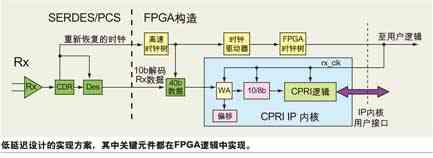

事實(shí)上在SerDes收發(fā)器內(nèi)部包括高速串并轉(zhuǎn)換電路、時(shí)鐘數(shù)據(jù)恢復(fù)電路、數(shù)據(jù)編解碼電路、時(shí)鐘糾正和通道綁定電路,為各種高速串行數(shù)據(jù)傳輸協(xié)議提供了物理層(PHY)基礎(chǔ)。而主流的8B/10B編碼SerDes則主要由物理介質(zhì)相關(guān)子層( PMD)、物理媒介適配層(Physical MediaAttachment,PMA)和物理編碼子層( Physical Coding Sublayer,PCS )所組成,且收發(fā)器的TX發(fā)送端和RX接收端功能獨(dú)立。

圖2 SerDes收發(fā)器內(nèi)部的電路物理層結(jié)構(gòu)圖

各物理層的作用:

1. PCS層,負(fù)責(zé)數(shù)據(jù)流的編碼/解碼,是標(biāo)準(zhǔn)的可綜合CMOS數(shù)字邏輯,可以通過邏輯綜合實(shí)現(xiàn)軟硬綜合實(shí)現(xiàn)。

2. PMA層,是數(shù)模混合CML/CMOS電路,負(fù)責(zé)負(fù)責(zé)串化/解串化,是理解SerDes區(qū)別于并行接口的關(guān)鍵。

3. PMD層,負(fù)責(zé)串行信號(hào)通信。

涉及模塊:

1. TXPLL:這個(gè)模塊主要使用具有1ps以下的抖動(dòng)的時(shí)鐘為參考,輸出數(shù)GHZ級(jí)的時(shí)鐘。

2. RXCDR(時(shí)鐘恢復(fù)):這個(gè)模塊是一個(gè)復(fù)雜的控制回路,作用是來追蹤傳入數(shù)據(jù)的平均相位,并不管Path上的任何SI或失真,通常是通過復(fù)雜的相位旋轉(zhuǎn)器或CDR驅(qū)動(dòng)的鎖相環(huán)來完成的。

3. TXdriver:這個(gè)模塊把序列化模塊轉(zhuǎn)化為差分信號(hào)。

4. RX均衡器:此模塊用連續(xù)的時(shí)間均衡器以及DFE(裁決反饋均衡器)來均衡高速效應(yīng),通常需要一個(gè)自動(dòng)增益的電路來促進(jìn)均衡效果,RX均衡器通常以狀態(tài)機(jī)邏輯和軟件的形式來實(shí)現(xiàn)自動(dòng)校準(zhǔn)。

轉(zhuǎn)化過程:

1. 發(fā)送(TX)即并轉(zhuǎn)串 簡單的來說就是并行信號(hào)通過FiFO,傳遞給內(nèi)部的8b/10b編碼器、擾碼器,防止數(shù)據(jù)連0/1,之后傳遞給串行器進(jìn)行轉(zhuǎn)化,經(jīng)過均衡器均衡后,由驅(qū)動(dòng)發(fā)出。

2. 接收(RX)即串轉(zhuǎn)并 簡單的來說就是輸入的串行信號(hào)經(jīng)過線性均衡器均衡后,去除了高速時(shí)鐘的jilter后,CDR從數(shù)據(jù)中恢復(fù)Caputure時(shí)鐘,并通過解串器轉(zhuǎn)為對(duì)齊的并行信號(hào),由驅(qū)動(dòng)發(fā)出。

光SerDes解串器

目前光互連中電串行/反串行器(SerDes)的高功耗和速度提升障礙是光互連發(fā)展的阻礙,人們逐漸把目光投向光SerDes的高速收發(fā)器。光SerDes解串器采用時(shí)間交錯(cuò)的多路復(fù)用技術(shù)來進(jìn)行并行串行光信號(hào)的直接轉(zhuǎn)換,同時(shí)電SerDes的缺失極大地降低了數(shù)據(jù)傳輸通道中的功耗,以一個(gè)工作在20個(gè)數(shù)據(jù)速率為2GHz的并行數(shù)字路徑和1個(gè)40GHz串行光通道之間的光SerDes收發(fā)器為例,其功耗僅為13.5pJ/b左右,要遠(yuǎn)遠(yuǎn)低于同類型電SerDes的靜態(tài)功耗。同時(shí)結(jié)合波分復(fù)用(WDM)、脈沖幅度調(diào)制(PAM)、正交相移鍵控(QPSM)等多種光復(fù)用技術(shù),可進(jìn)一步提高帶寬。

在數(shù)據(jù)中心、超級(jí)計(jì)算機(jī)和光纖接入網(wǎng)的數(shù)據(jù)通信中,對(duì)未來帶寬的需求不斷增長,這促使傳統(tǒng)的電子鏈路被光鏈路取代,用于片內(nèi)和片外通信。雖然光學(xué)技術(shù)在帶寬、損耗、串?dāng)_、電磁兼容等方面具有優(yōu)勢,但由于光信號(hào)不能直接由處理器處理,需要將光信號(hào)轉(zhuǎn)換為電信號(hào)。傳統(tǒng)的光互連通信解決方案是將并行電信號(hào)通過芯片內(nèi)部的串行器/反串行器(SerDes)轉(zhuǎn)換為高速串行電信號(hào),再通過芯片外部的光收發(fā)器轉(zhuǎn)換為光信號(hào)。由于SerDes電路的高功耗和鏈路比特率,光互連的發(fā)展逐漸面臨瓶頸。收發(fā)器的大部分功率消耗在模擬電路,特別是SerDes上,而不是光學(xué)器件上。

以當(dāng)前28Gb/s系統(tǒng)為例,收發(fā)器的光電轉(zhuǎn)換(EO)和光電轉(zhuǎn)換(OE)功耗僅為7.2pJ/b。但是整個(gè)鏈路的功率預(yù)算增長到29.5pJ/b,其中22.3pJ/b(75.6%)是由SerDes電路貢獻(xiàn)的,這與OE-EO轉(zhuǎn)換沒有直接關(guān)系。進(jìn)一步的帶寬擴(kuò)展受到嚴(yán)重限制,因?yàn)樾枰鈦砘謴?fù)信號(hào)完整性,并在高速串行鏈路的末端重新計(jì)時(shí),即使是非常短的幾英寸距離。同時(shí)提高比特率和保持低功耗是不可持續(xù)的。因此,最好是提高并行度來提高鏈路比特率。但是并行化程度的提高是由芯片的引腳數(shù)決定的,而引腳數(shù)是由制造工藝、芯片尺寸、芯片頂層設(shè)計(jì)等決定的。

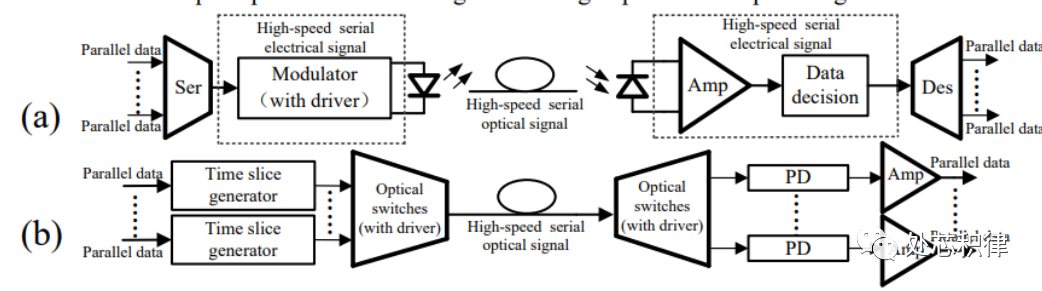

簡單地說,光SerDes就是利用時(shí)分復(fù)用技術(shù)將并行電信號(hào)加載到光載波上,獲得單波長單通道電平可能高于40Gb/s的串行光傳輸,同時(shí)完成光電和串并聯(lián)轉(zhuǎn)換。如圖3所示,傳統(tǒng)的電子SerDes收發(fā)器需要兩級(jí)轉(zhuǎn)換,以高速串行電信號(hào)為介質(zhì),將低速并行電信號(hào)轉(zhuǎn)換為高速串行光信號(hào),而光SerDes收發(fā)器實(shí)現(xiàn)了低速并行電信號(hào)與高速串行光信號(hào)的直接轉(zhuǎn)換,即比傳統(tǒng)的電SerDes多了一級(jí)光電信號(hào)轉(zhuǎn)化。

圖3 兩種收發(fā)器的比較。(a)在傳統(tǒng)收發(fā)器中,以高速串行電信號(hào)為介質(zhì),利用電子SerDes將并行電信號(hào)轉(zhuǎn)換為高速串行光信號(hào)。(b)在所提出的收發(fā)器中,利用光SerDes將并行電信號(hào)直接轉(zhuǎn)換為高速串行光信號(hào)。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613910 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3624瀏覽量

107343 -

解串器

+關(guān)注

關(guān)注

1文章

133瀏覽量

13963 -

SERDES接口

+關(guān)注

關(guān)注

0文章

28瀏覽量

3172

原文標(biāo)題:PCIE,USB,SATA ,Ethernet 都在用的?SerDes到底是個(gè)啥?

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

SerDes的技術(shù)原理 SerDes的重要概念和技術(shù)概述

視頻: Artix-7 FPGA:如何在大批量應(yīng)用中使用高速SerDes

SERDES接口電路設(shè)計(jì)

FPGA高速收發(fā)器設(shè)計(jì)要遵循哪些原則?

請問7系列中的SERDES是否有最小延遲規(guī)范?

高速SERDES接口在網(wǎng)絡(luò)方面有哪些應(yīng)用?

Nautilus UDI方案是如何實(shí)現(xiàn)高速SerDes測試的?

高速SerDes PCB設(shè)計(jì)的相關(guān)資料分享

FPGA高速收發(fā)器設(shè)計(jì)原則

基于SERDES收發(fā)器和CPRI的電信系統(tǒng)低延遲變化設(shè)計(jì)

高速SerDes PCB 設(shè)計(jì)

SERDES關(guān)鍵技術(shù)

如何在網(wǎng)絡(luò)中使用光纖收發(fā)器?使用光纖收發(fā)器的注意事項(xiàng)

汽車以太網(wǎng)發(fā)明人押寶SerDes!一文詳解車載SerDes技術(shù)

什么是SerDes?SerDes有哪些應(yīng)用?

介紹一種采用光SerDes而非電SerDes的高速收發(fā)器

介紹一種采用光SerDes而非電SerDes的高速收發(fā)器

評(píng)論