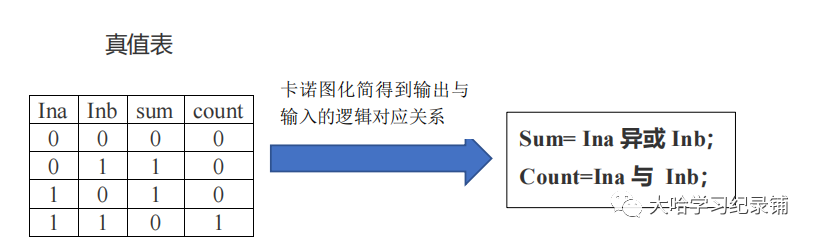

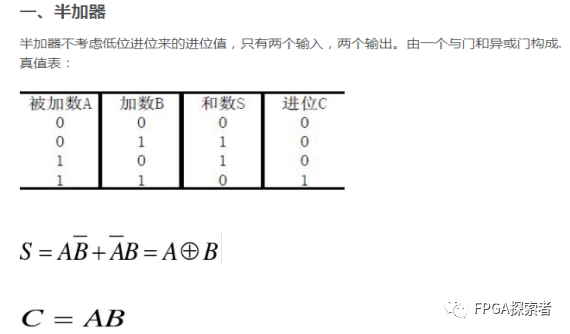

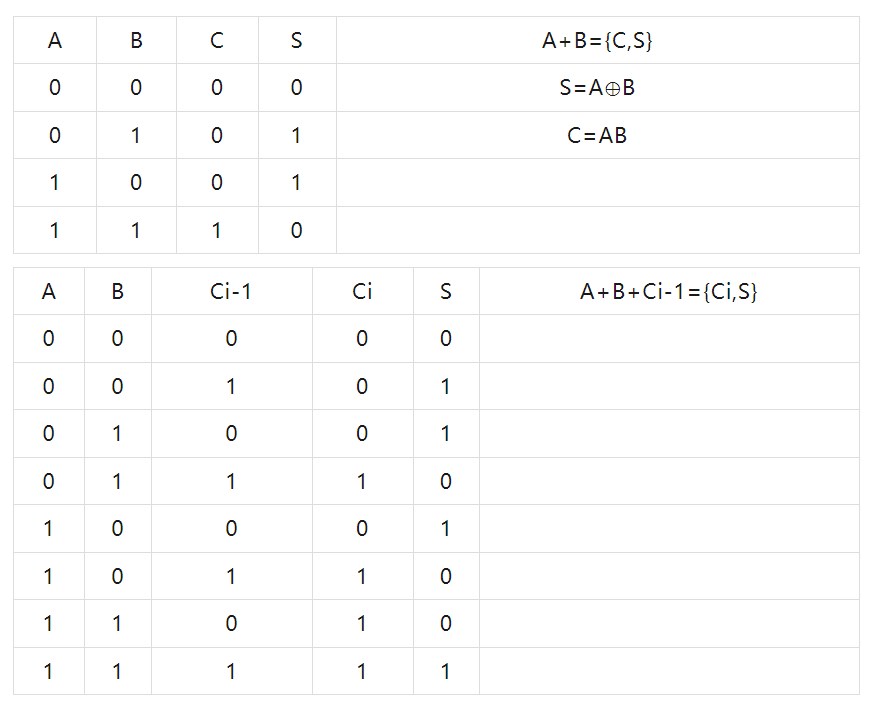

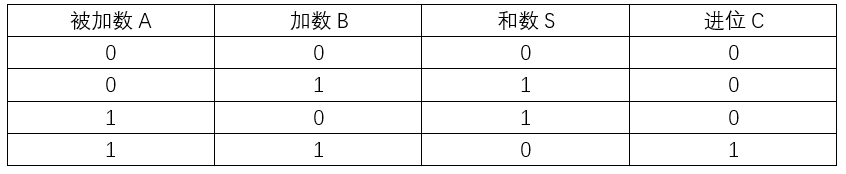

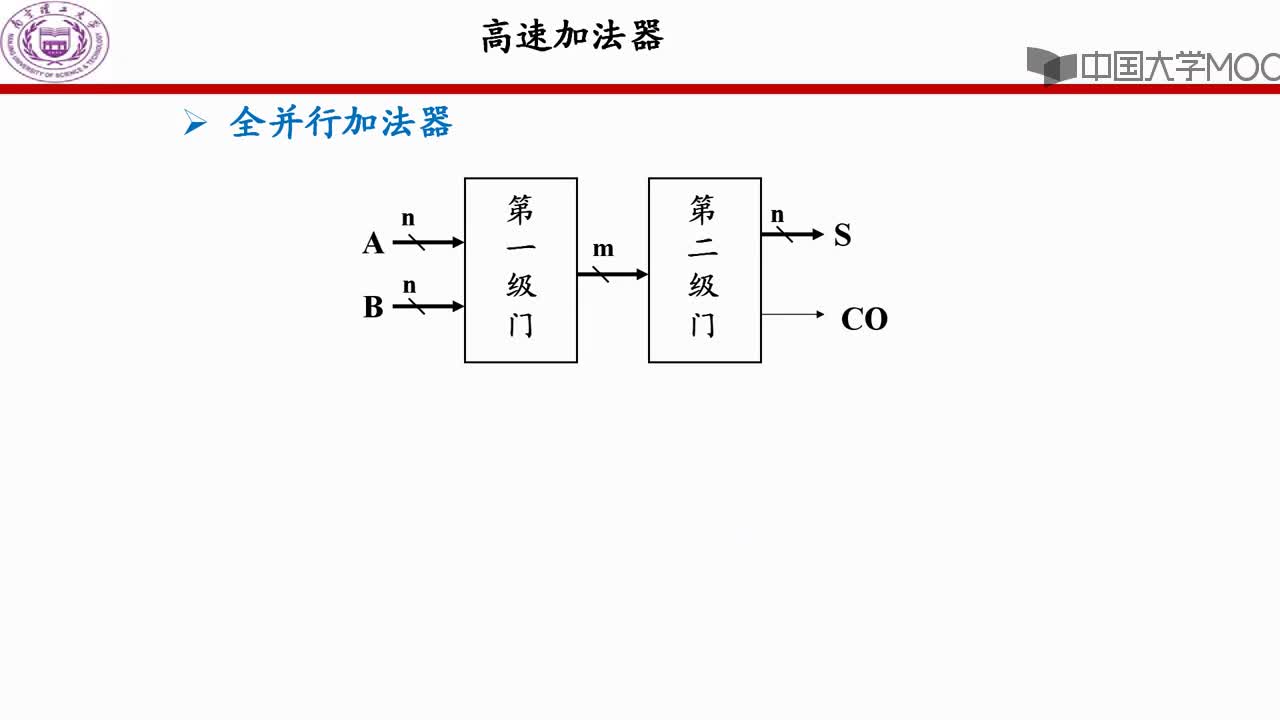

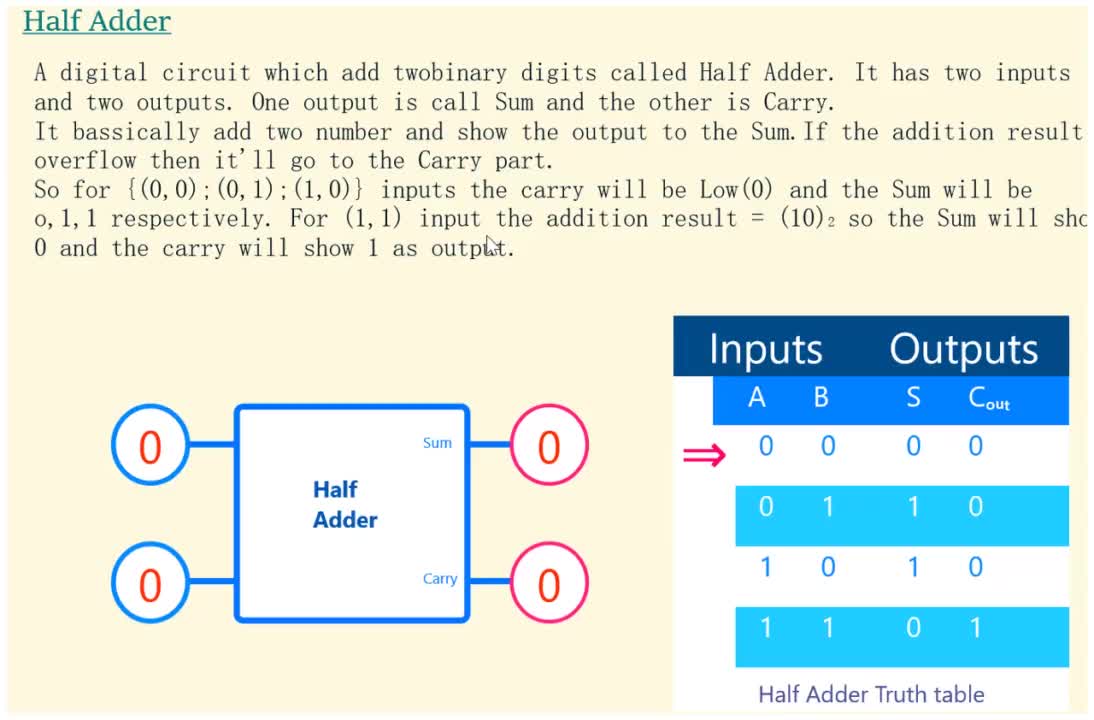

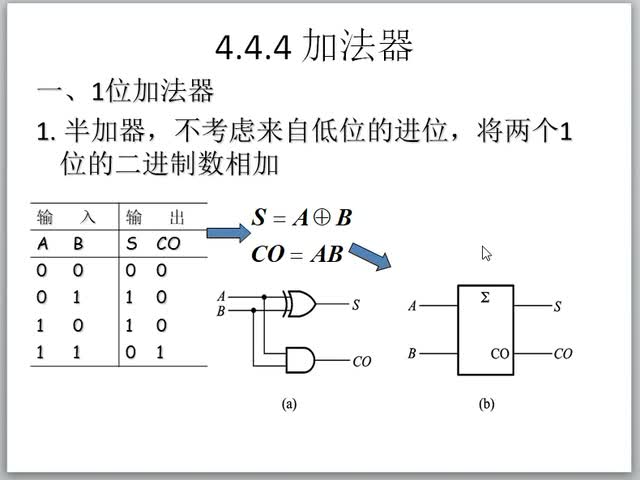

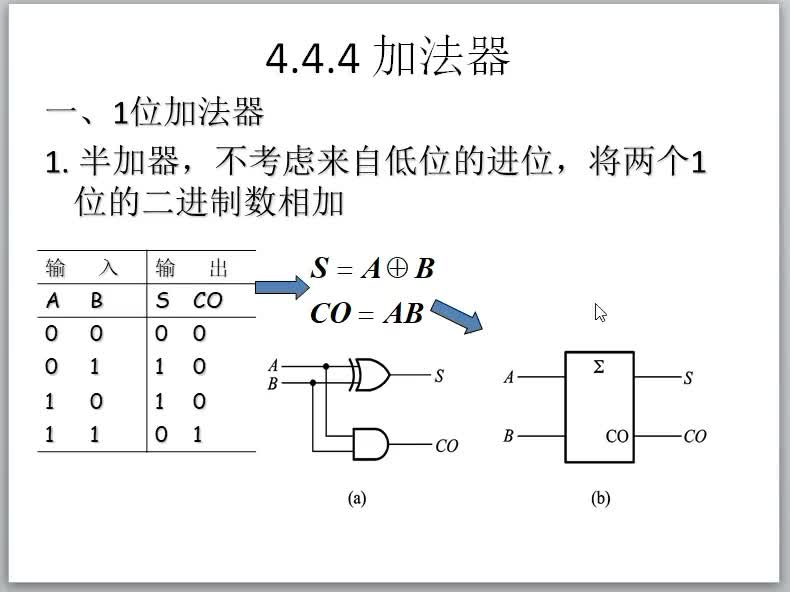

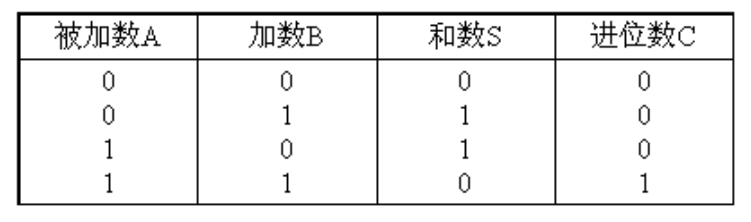

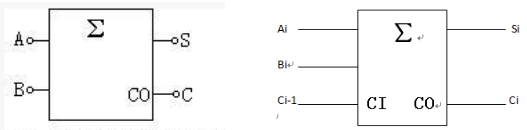

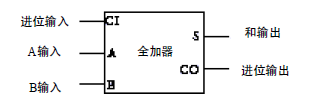

半加器和全加器是算術(shù)運(yùn)算電路中的基本單元,它們是完成1位二進(jìn)制數(shù)相加的一種組合邏輯電路。兩個(gè)1二進(jìn)制的加法運(yùn)算如下表所示,其中S表示和數(shù)C表示進(jìn)位數(shù)。由表中邏輯關(guān)系可見,這種加法運(yùn)算只考慮了兩個(gè)加數(shù)本身,而沒有考慮由低位來的進(jìn)位,所以稱為半加。半加器就是實(shí)現(xiàn)下面這個(gè)真值表關(guān)系的電路。

由真值表可得邏輯表達(dá)式

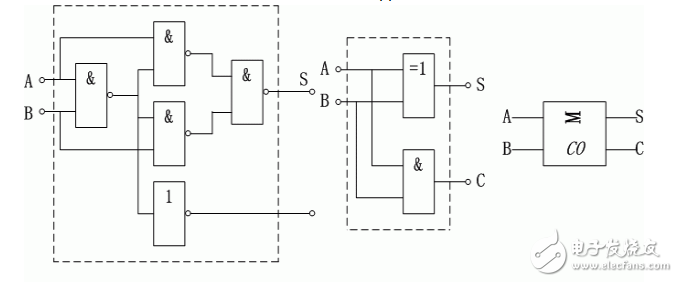

運(yùn)用邏輯代數(shù),可將上式變換成與非形式

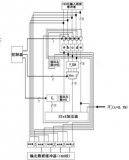

根據(jù)這兩個(gè)表達(dá)式可得由與非門組成的半加器:

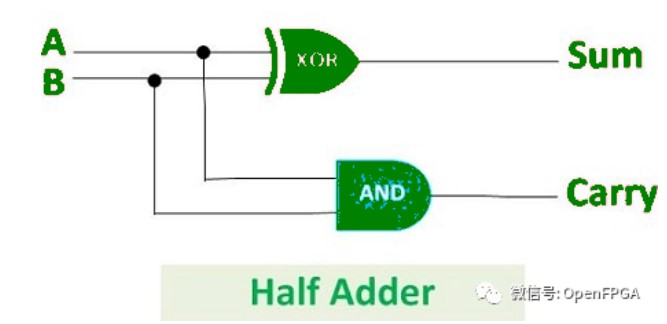

因?yàn)榘爰雍?img src="/article/UploadPic/2009-4/200947103417834.gif" align=absMiddle>是異或關(guān)系,所以半加器也可利用一個(gè)集成異或門和與門來實(shí)現(xiàn):

圖中右邊是半加器的代表符號(hào)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論