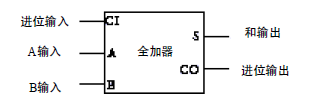

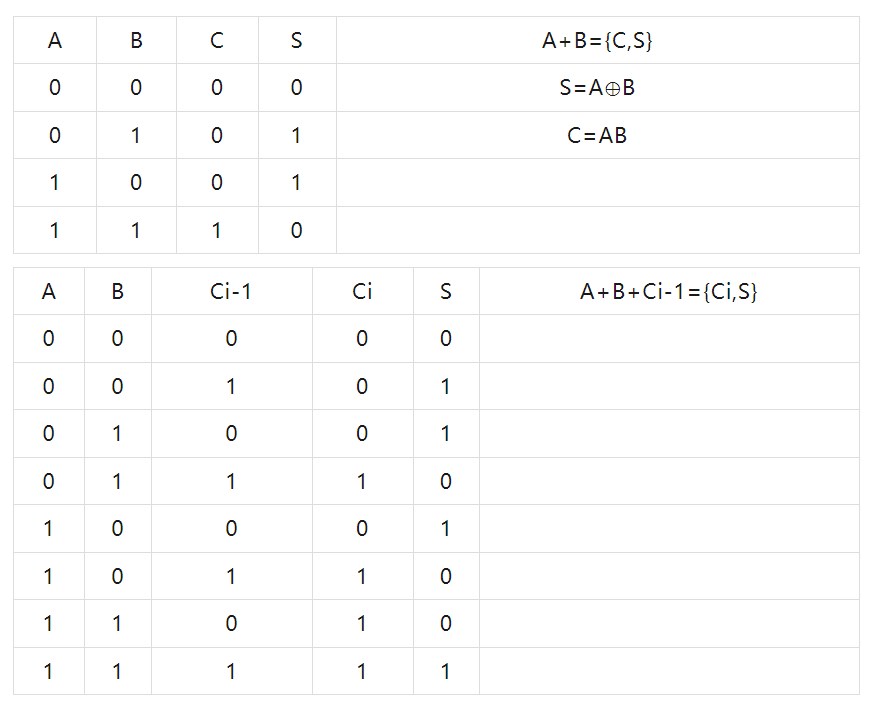

實際上,一個完整的加法器的輸入端有3個:A、B和低位的進位結(jié)果CI。

全加器(Full Adder)

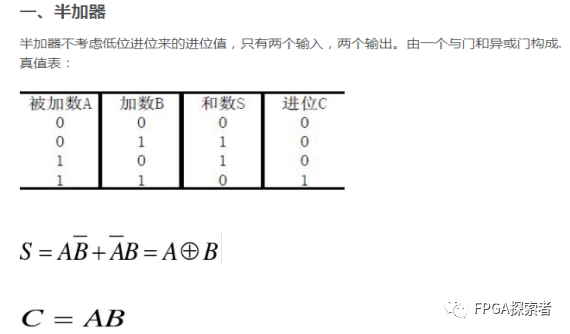

這個全加器相當(dāng)于是計算3個位(A、B、CI)的和。因此,其最終的“和輸出”為三個數(shù)的異或。進位輸出的規(guī)律為:3個數(shù)中如果有2個或者以上的數(shù)為1時,“進位”位就為1.

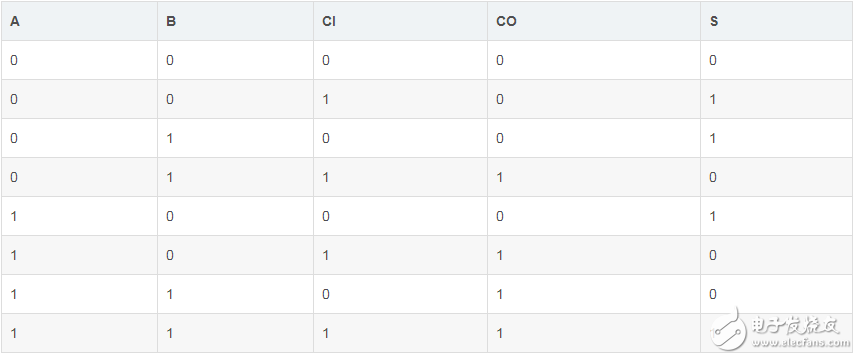

全加器真值表

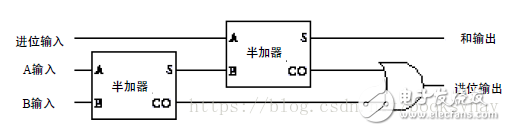

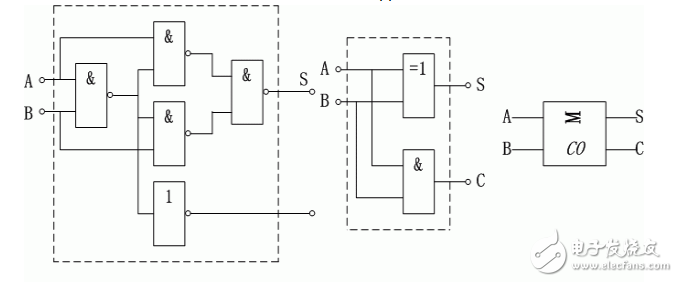

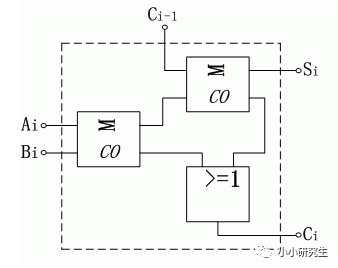

為了實現(xiàn)這個功能,可以使用兩個半加器:

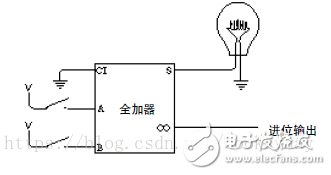

這個一位的全加器應(yīng)用于個位時,需要將進位輸出接到地,即置為0:

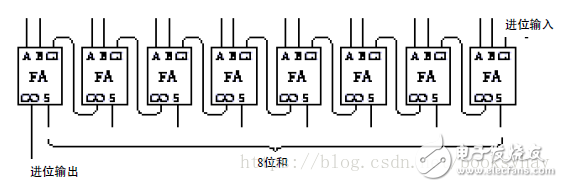

將多個“一位全加器”級聯(lián)起來,可以變成“多位全加器”,上一個全加器的“進位輸出”連到下一個全加器的“進位輸入”。比如8位全加器如下:

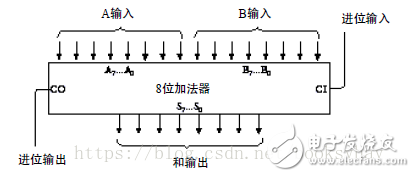

可以簡化為:

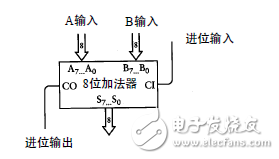

或者:

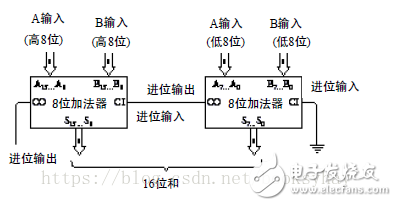

同樣的,可以將兩個8位全加器級聯(lián)起來,變成一個16位的全加器:

最后:你可能會問:“計算機真的是以這種方式把數(shù)字加起來的嗎?”

基本上是這樣的,但不完全是。

首先,加法器應(yīng)該做得更快。如果你明白這個電路是如何工作的,你會看到最低位相加產(chǎn)生的進位作為下一列數(shù)相加的一個輸入,而第3列的加法又等著第2列加法的進位,依此類推。加法器總體的速度等于加數(shù)的位數(shù)乘以單個全加器的速度。這種進位方式稱為行波進位。

更快的加法器使用稱為先行進位的加法電路,從而加快了加法進程。

第二(但是十分重要),計算機再也不用繼電器了!盡管它們曾經(jīng)用過。建于2 0世紀3 0年代初的第一批數(shù)字計算機使用繼電器,后來又用了真空管。現(xiàn)代計算機用晶體管。當(dāng)用在計算機中時,晶體管和繼電器的功能差不多,但是晶體管速度更快,體積更小,更安靜,更省電,而且還便宜不少。構(gòu)造一個8位加法器仍然需要1 4 4個晶體管(如果采用先行進位,則需要更多),但整體電路的體積卻小多了。

-

全加器

+關(guān)注

關(guān)注

10文章

62瀏覽量

28835 -

半加器

+關(guān)注

關(guān)注

1文章

29瀏覽量

8967

發(fā)布評論請先 登錄

FPGA入門——1位全加器設(shè)計 精選資料分享

全加器,全加器是什么意思

全加器是什么?全加器和半加器的區(qū)別?

請用Verilog分別實現(xiàn)1位半加器和1位全加器

如何用半加器實現(xiàn)全加器?

如何用半加器實現(xiàn)全加器?

評論