Vivado Synthesis的各種流程

Vivado IPI (IP Integrator)提供了直觀的模塊化的設計方法。用戶可以將Viva....

關于datasheet的含義

設計分析時,我們除了查看資源利用率、時序指標、功耗等基本信息之外,有時也需要查看跟輸入/輸出管腳相關....

Routing Complexity是什么含義呢?

那么Routing Complexity是什么含義呢?Routing Complexity實際反映的....

UltraScale/UltraScale+的時鐘資源

UltraScale和UltraScale+進一步增強了Clock root的概念,從芯片架構和Vi....

Pblock的一個屬性CONTAIN_ROUTING

使用CONTAIN_ROUTING之后,布線時在Pblock的拐角處會遇到較大困難,可能出現布線擁塞....

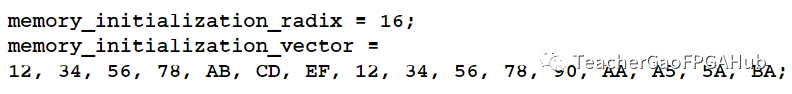

如何使用API定義一個向量呢

數據類型是我們使用C++編程時必須明確的一項內容。針對AI Engine,這一點尤為重要。因為不同的....

如何評估graph的性能

評估graph的性能對于kernel接口設計有著非常重要的意義。我們仍以前一篇文章中提到的工程為例。....

使用Trace View對對Kernel進行性能仿真分析

對Kernel進行性能分析需要對其進行仿真,同時還要用到Vitis Analyzer。為便于說明,我....

AI Engine架構的構成及應用優勢

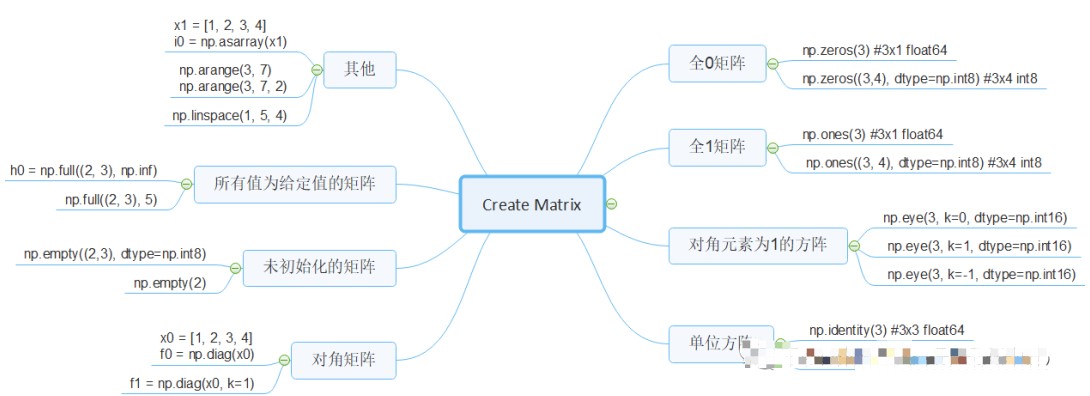

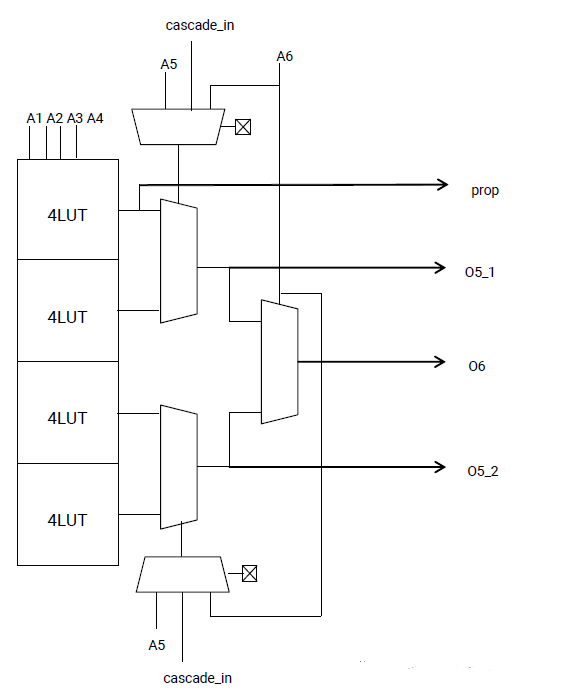

至此,我們可以看到AI Engine有三種數據源:存儲單元、AXI4-Stream和級聯接口。因此,....

在Vivado中怎么定制Strategy

Vivado提供了多種Synthesis策略和Implementation策略,用戶可以直接使用這些....

在Vivado中怎么定制Strategy

Vivado提供了多種Synthesis策略和Implementation策略,用戶可以直接使用這些....

Vivado BDC (Block Design Container)怎么用

談到BDC(Block DesignContainer)就不得不提IPI(IP Integrator....

使用Vivado License Manager時Vivado的錯誤信息

Vivado License Manager在使用Vivado License Manager時,如....

使用帶HBM芯片有哪些要注意的地方

Virtex UltraScale+部分芯片中集成了HBM(High Bandwidth Memor....

基于Vivado下怎么找到關鍵路徑?

什么是關鍵路徑? 關鍵路徑分為兩類:一類是時序違例的路徑,主要是建立時間違例; 另一類是時序沒有違例....

UltraScale和Versal之間有哪些不同?

作為Xilinx 7nm芯片,Versal在架構上與前一代芯片UltraScale相比有諸多不同,這....

如果是多通道輸入數據,是否依然存在矩陣乘法呢?

進一步擴展,如果每個通道有多個與之對應的Kernel,會是什么情形呢?如下圖所示。圖中,每個通道有4....

卷積神經網絡中的矩陣乘法

先看一個二維濾波器,如下圖所示。濾波器是一個3x3的矩陣,輸入數據是一個5x5的矩陣。輸入矩陣中的紅....