在FPGA設(shè)計中,我們遵循的原則之一是同步電路,即所有電路是在同一時鐘下同步地處理數(shù)據(jù)。這個概念可進一步展開,即不局限于同一時鐘,只要時鐘之間是同步關(guān)系(兩者之間有明確的相位延遲,例如同一個MMCM生成的時鐘),這是因為目前的芯片規(guī)模越來越大,設(shè)計越來越復(fù)雜,往往需要多個時鐘同時運算。

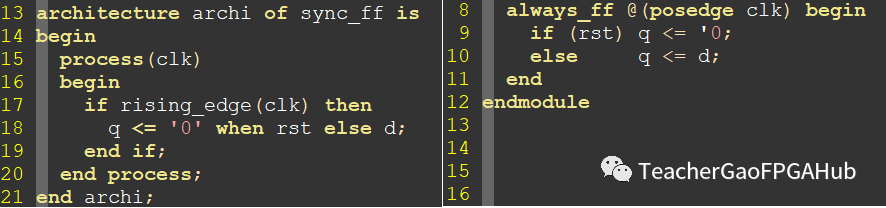

通常,我們說某個信號與指定時鐘同步,意味著這個信號是由該時鐘驅(qū)動的邏輯生成的,或者這個信號只有在時鐘有效沿(一般是上升沿有效)下才會被觸發(fā)。以復(fù)位信號為例,就有同步復(fù)位和異步復(fù)位之分。我們從HDL代碼角度看一下二者的區(qū)別。如下圖所示代碼,描述的是同步復(fù)位觸發(fā)器,左側(cè)為VHDL-2008版本的描述方式,右側(cè)為System Verilog版本的描述方式。可以看到敏感變量列表(左側(cè)第15行,右側(cè)第8行)中只有時鐘clk,因此,進程中的狀態(tài)變化就依賴于時鐘的變化即時鐘有效沿。

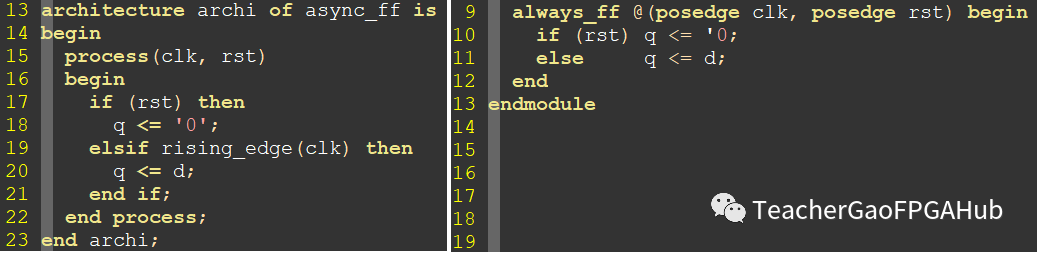

我們再看看異步復(fù)位是如何描述的,如下圖所示。左側(cè)是VHDL-2008版本,右側(cè)是System Verilog版本。可以看到,此時敏感變量列表中除了時鐘clk之外還有復(fù)位信號rst。在VHDL版本中,可以明確地看到復(fù)位信號位于if條件分支,而時鐘有效沿位于elsif分支,優(yōu)先級低于復(fù)位信號。因此,這里只要復(fù)位有效,無論時鐘沿是否有效都會觸發(fā)操作。

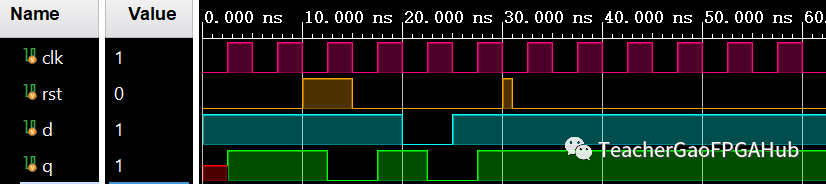

進一步,我們從仿真角度看看這兩者的區(qū)別。同步復(fù)位觸發(fā)器的仿真結(jié)果如下圖所示。可以看到復(fù)位信號只有在時鐘有效沿下才起作用。圖中第二個復(fù)位脈沖并沒有被時鐘有效沿采到,故不會導(dǎo)致觸發(fā)器復(fù)位。

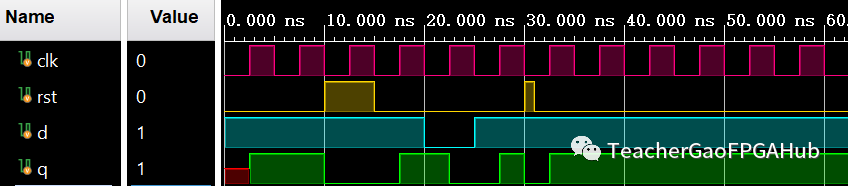

異步復(fù)位觸發(fā)器仿真結(jié)果如下圖所示。可以看到第二個復(fù)位脈沖盡管沒有在時鐘有效沿下,但仍促使觸發(fā)器復(fù)位。這正是異步的原理。

對比兩個仿真結(jié)果,我們可以看到同步復(fù)位的一個明顯的好處就是利用了時鐘的過濾功能,去除了復(fù)位信號上的毛刺,而異步復(fù)位下,如果復(fù)位信號有毛刺就會導(dǎo)致觸發(fā)器誤操作,這在狀態(tài)機電路中尤為嚴重,很有可能導(dǎo)致狀態(tài)機進入無效狀態(tài)。

編輯:lyn

-

仿真

+關(guān)注

關(guān)注

52文章

4269瀏覽量

135732 -

同步復(fù)位

+關(guān)注

關(guān)注

0文章

27瀏覽量

10872 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13504

原文標題:同步復(fù)位與異步復(fù)位

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

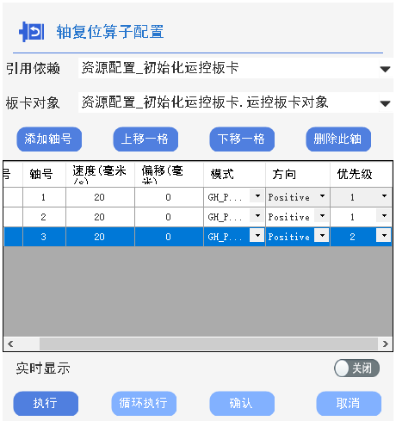

GraniStudio零代碼平臺軸復(fù)位算子支持多少個軸同時復(fù)位,有哪些回零模式?

復(fù)位電路的核心功能和主要類型

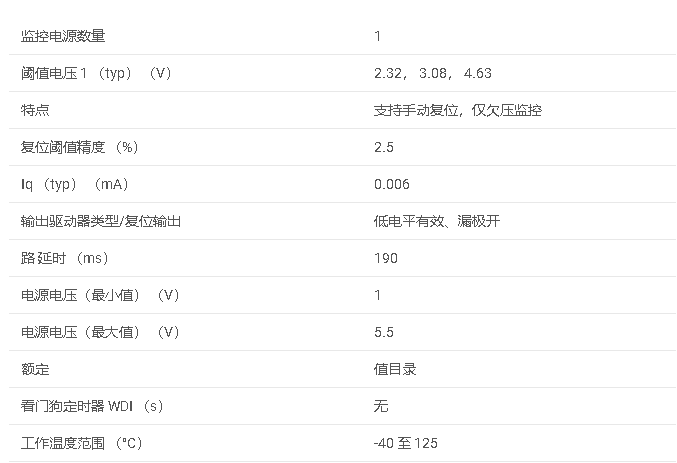

LM3724系列 低功率電壓監(jiān)控和復(fù)位IC,帶手動復(fù)位功能數(shù)據(jù)手冊

復(fù)位電路的作用、控制方式和類型

FPGA復(fù)位的8種技巧

復(fù)位電路的設(shè)計問題

復(fù)位電路的三種方式 復(fù)位電路的原理和作用

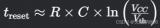

復(fù)位電路的電容多大的 復(fù)位電路設(shè)計類型有哪幾種

復(fù)位電路靜電整改案例分享(一)——交換機復(fù)位電路

關(guān)于同步復(fù)位與異步復(fù)位的仿真詳解

關(guān)于同步復(fù)位與異步復(fù)位的仿真詳解

評論