All Programmable技術和器件的全球領先企業賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))今日宣布其Zynq UltraScale+ RFSoC 系列開始發貨,該系列是通過一個突破性的架構將 RF 信號鏈集成在一個單芯片 SoC 中,致力于加速 5G 無線、有線 Remote-PHY 及其它應用的實現。基于 16nm UltraScale+ MPSoC 架構的 All Programmable RFSoC 在單芯片上集成 RF 數據轉換器,可將系統功耗和封裝尺寸減少最高達 50%~70%,而且其軟判決前向糾錯 (SD-FEC) 內核可滿足 5G 和 DOCSIS 3.1 標準要求。隨著芯片樣片向多家客戶發貨, Zynq UltraScale+ RFSoC 系列早期試用計劃現已啟動。

用于 RF 信號鏈的片上系統

Zynq RFSoC 將 RF 數據轉換器、SD-FEC 內核以及高性能 16nm UltraScale+ 可編程邏輯和 ARM 多處理系統完美集成在一起打造出了一個全面的模數信號鏈。射頻-數字信號調節與處理通常分派給不同的獨立子系統中,但 Zynq UltraScale+ RFSoC 將模擬、數字和嵌入式軟件設計集成到單個單芯片器件上,實現了高度的系統穩健性。該系列器件具有如下特性:

● 8 個 4GSPS 或 16 個 2GSPS 12 位 ADC

●8-16 個 6.4GSPS 14 位 DAC

●SD-FEC 內核、LDPC 和 Turbo 編解碼器完美集成在一起,可滿足 5G 和 DOCSIS3.1 標準要求

●ARM 處理子系統,采用四核 Cortex-A53 和雙核 Cortex-R5

●16nm UltraScale+ 可編程邏輯配有集成 Nx100G 內核

●多達 930,000 個邏輯單元和超過 4,200 個 DSP Slice

賽靈思通信業務主管總監 Gilles Garcia 介紹 Zynq RFSoC

Zynq RFSoC 系列支持的應用包括 massive-MIMO 的遠端射頻單元、毫米波移動回程、5G 基帶、固定無線訪問、有線 Remote-PHY 節點、測試測量、衛星通信等高性能 RF 應用。

5G 無線

Zynq UltraScale+ RFSoC 器件能為下一代無線基礎架構提供帶寬密集型系統。如果沒有系統級的突破,5 倍帶寬、100 倍用戶數據速率、1000 倍網絡容量等在內的 5G 要求均無法實現。Zynq UltraScale+ RFSoC 集成了分立式 RF 數據轉換器和信號鏈優化技術,這樣 Massive-MIMO 的遠端射頻單元、無線回程和固定無線訪問不僅可實現高信道密度,而且還能將功耗和封裝尺寸減小 50%-75%。在 5G 基帶應用中,多個集成 SD-FEC 內核相對于軟核實現方案而言,可將系統吞吐量提升 10-20 倍,并可滿足嚴格的功耗和散熱要求。

有線 Remote-PHY

同樣,在下一代有線寬帶服務領域,Zynq RFSoC 也實現了封裝尺寸、能效和硬件靈活性的完美組合,可支持 Remote-PHY 系統。分布式訪問架構推動 DOCSIS 3.x PHY 功能從集中頭端設備轉移到靠近消費者的 Remote-PHY 節點。通過用無所不在的以太網傳輸取代低效的模擬光傳輸,網絡的容量、規模和性能得到了大幅提升。通過 RF 集成和支持 LDPC FEC 的信號鏈,RFSoC 能確保靈活的 R-PHY 部署,從而可滿足 DOCSIS3.1 更高的頻譜效率要求。

-

賽靈思

+關注

關注

33文章

1797瀏覽量

132354 -

單芯片

+關注

關注

3文章

462瀏覽量

35196 -

5G

+關注

關注

1360文章

48813瀏覽量

573781

發布評論請先 登錄

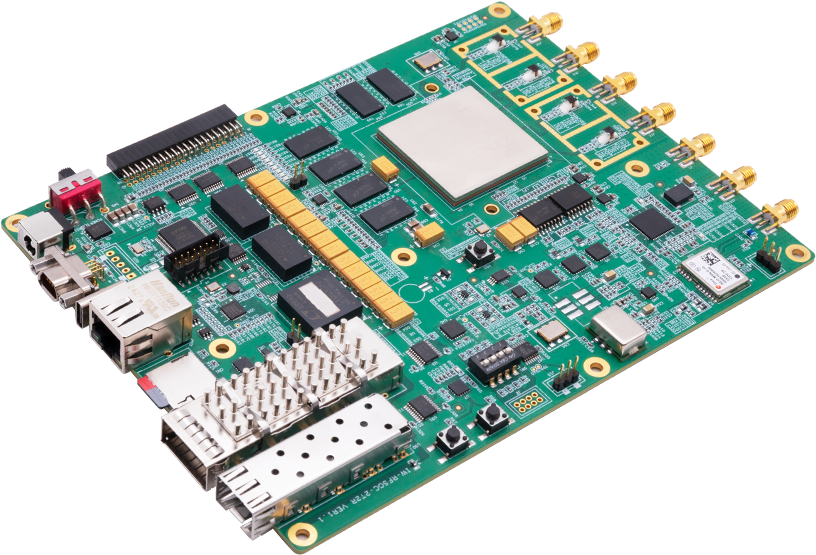

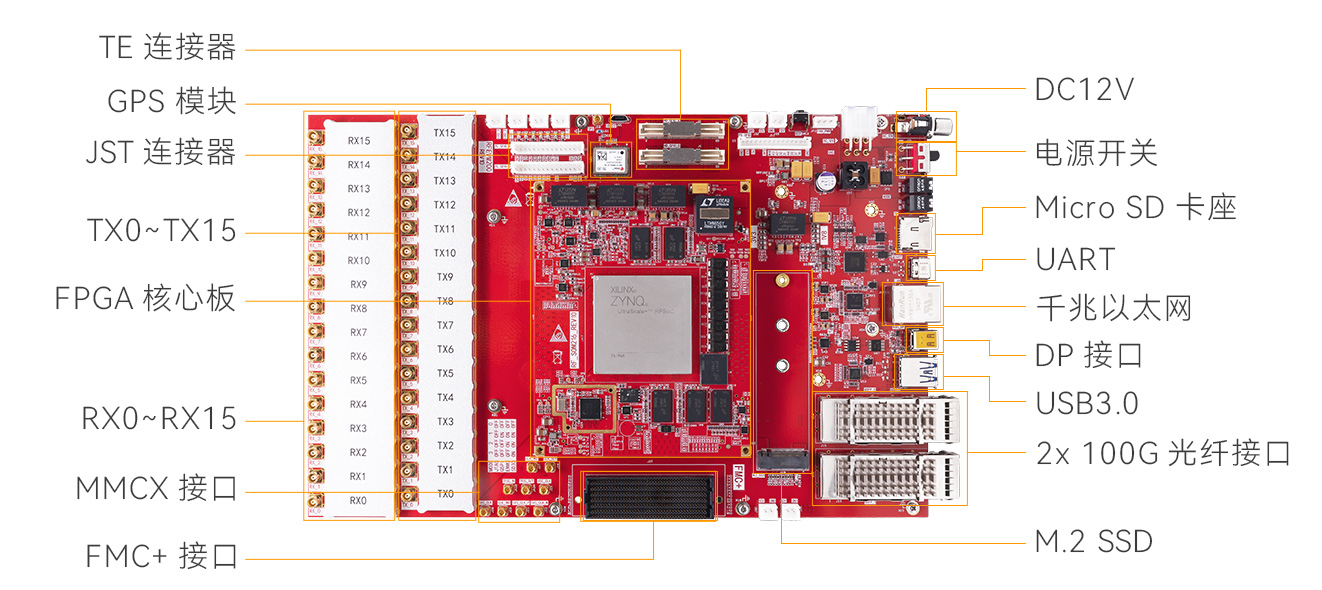

高性能緊湊型 RFSoC FPGA 開發平臺 AXW22,重塑射頻開發體驗

AMD Spartan UltraScale+ FPGA 開始量產出貨

一板多能,AXRF49 定義新一代 RFSoC FPGA 開發平臺

直采+異構,看 RFSoC FPGA 開發板 AXW49 如何應對射頻信號處理高要求

AMD Zynq RFSoC賦能富士通ORAN無線電產品

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

針對ZYNQ+ULTRASCALE的FPGA供電的一些疑問求解答

時序約束一主時鐘與生成時鐘

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

賽靈思公司宣布其Zynq UltraScale+ RFSoC系列開始發貨

賽靈思公司宣布其Zynq UltraScale+ RFSoC系列開始發貨

評論