時鐘接口閾值區間附近的抖動會破壞ADC的時序。例如,抖動會導致ADC在錯誤的時間采樣,造成對模擬輸入的誤采樣,并且降低器件的信噪比(SNR)。降低抖動有很多不同的方法,但是,在get降低抖動的方法前我們必須找到抖動的根本原因!

時鐘抖動,why?

時鐘抖動的根本原因就是時鐘和ADC之間的電路噪聲。隨機抖動由隨機噪聲引起,主要隨機噪聲源包括:

熱噪聲(約翰遜或奈奎斯特噪聲),由載流子的布朗運動引起。

散粒噪聲,與流經勢壘的直流電流有關,該勢壘不連續平滑,由載流子的單獨流動引起的電流脈沖所造成。

閃爍噪聲,出現在直流電流流動時。該噪聲由攜帶載流子的半導體中的陷阱引起,這些載流子在釋放前通常會形成持續時間較短的直流電流。

爆裂噪聲,也稱爆米花噪聲,由硅表面的污染或晶格錯位造成,會隨機采集或釋放載流子。

查看時鐘信號噪聲,how?

確定性抖動由干擾引起,會通過某些方式使閾值發生偏移,通常受器件本身特性限制。查看時鐘信號噪聲通常有三種途徑:時域、頻域、相位域。

咳咳,敲黑板劃重點,以上三種途徑的具體方法如下↓↓↓

時域圖

圖1. 抖動的時域圖

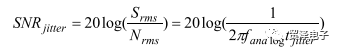

時鐘抖動是編碼時鐘的樣本(不同周期)間的變化,包括外部和內部抖動。抖動引起的滿量程信噪比由以下公式得出

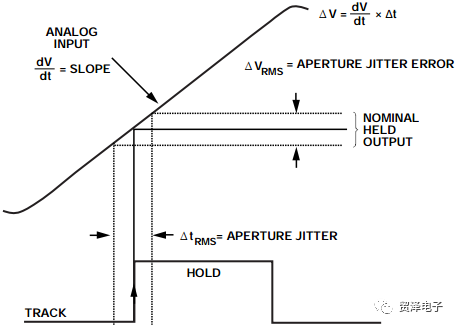

舉個栗子,頻率為1 Ghz,抖動為100 FS均方根值時,信噪比為64 dB。在時域中查看時,x軸方向的編碼邊沿變化會導致y軸誤差,幅度取決于邊沿的上升時間。孔徑抖動會在ADC輸出產生誤差,如圖2所示。抖動可能產生于內部的ADC、外部的采樣時鐘或接口電路。

圖2. 孔徑抖動和采樣時鐘抖動的影響

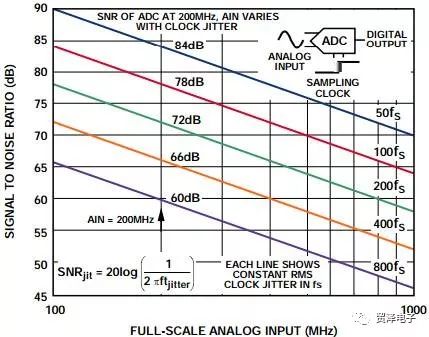

圖3顯示抖動對信噪比的影響。圖中顯示了5條線,分別代表不同的抖動值。x軸是滿量程模擬輸入頻率,y軸是由抖動引起的信噪比,有別于ADC總信噪比。

圖3. 時鐘抖動隨模擬信號增大而提升信噪比

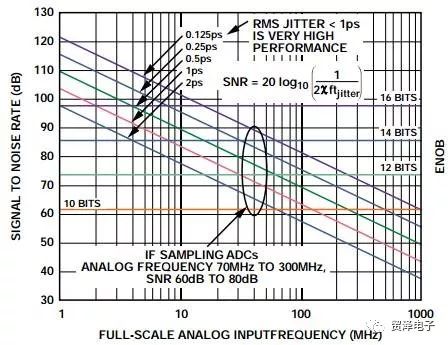

由抖動引起的信噪比和有效位數(ENOB)的關系由以下公式定義:

SNR = 6.02 N + 1.76 dB

其中N =有效位數。滿量程100 MHz輸入時,14位有效位數要求均方根抖動不超過0.125 ps或125 fs。該公式假定ADC具有無限分辨率,其中的唯一誤差是由時鐘抖動產生的噪聲。

圖4. 由抖動產生的理論信噪比和有效位數與滿量程正弦波模擬輸入頻率的關系

頻域圖

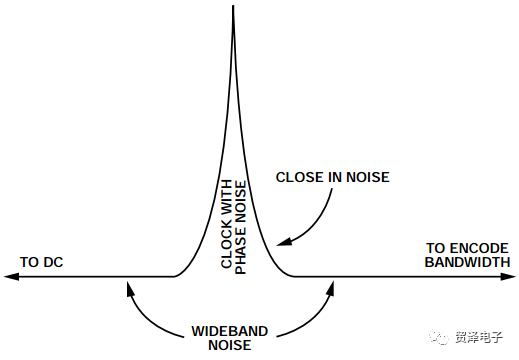

近載波噪聲出現在采樣時鐘中心頻率和等于信號帶寬一半的單邊帶(SSB)失調之間。寬帶噪聲的范圍從單邊帶失調到?時鐘接收器帶寬。

圖5. 頻域圖

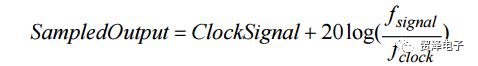

時間的乘法運算是在頻域中進行卷積。因此,時鐘上在頻域上的任何“裙邊”都會施加于數字信號。這會增加信號的EVM,降低整體性能。卷積到采樣信號上的噪聲量取決于模擬頻率與采樣頻率的關系。

圖6.卷積到采樣信號上的噪聲取決于模擬頻率和采樣頻率的關系

相位域圖

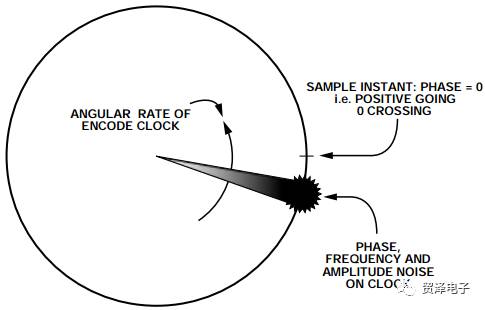

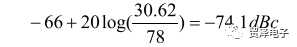

相位噪聲由每個時鐘周期之間的時間變化引起。最終結果是時鐘信號在基波頻率周圍變化,這一頻率范圍變化會降低ADC的信噪比。

圖7.抖動的相位域圖

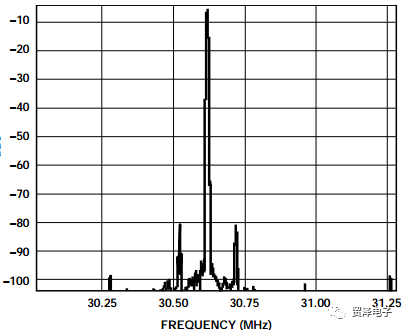

圖8所示的例子中,?66 dBc的雜散增加到78 MHz時鐘上,用來將ADC采樣控制在30.62 MHz模擬信號。

圖8. 使用噪聲時鐘采樣時的30.62 MHz信號

雜散為?74.1 dBc,按以下公式計算:

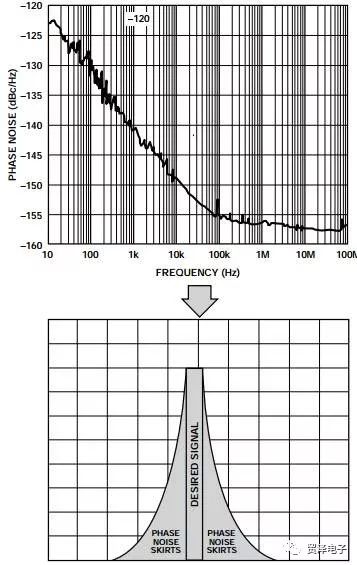

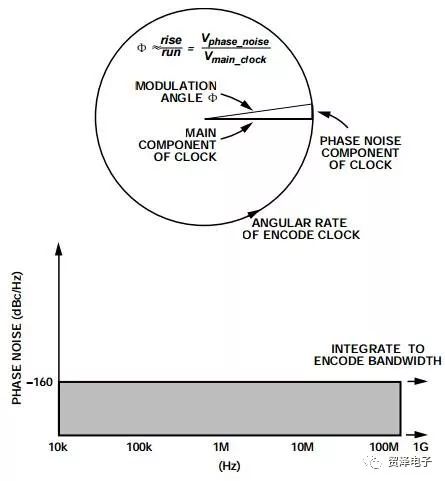

時鐘設計人員通常會提供一個相位噪聲,但不提供抖動規格。相位噪聲規格可以轉換為抖動,首先確定時鐘噪聲,然后通過小角度計算將噪聲與主時鐘噪聲成分進行比較。相位噪聲功率通過計算圖9中的灰色區域積分得出。

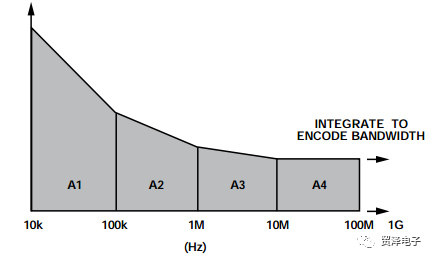

圖9. 對編碼帶寬的近載波到時鐘輸出噪聲進行積分計算

高度為?160 dBc,寬度為10 KHz至245.76 MHz。因此,

10×log(245.7e6 ? 10e3)

= 83.9 dB,?160 + 83.9 dB

= 76.1 dBc

得出積分噪聲。

載波的失調不同,噪聲的斜率也不同。例如,A1區域通常為1/f噪聲,而A4區域則視為寬帶噪聲。

圖10.在頻率范圍內的噪聲變化情況

A =面積=積分相位噪聲功率(dBc)抖動可以通過對編碼帶寬的近載波到時鐘輸出的噪聲進行積分計算確定。頻率范圍應分為較小的頻帶,然后相加得到總的結果:A = 10 log10 (A1 + A2 + A3 + A4)

-

頻率

+關注

關注

4文章

1558瀏覽量

60040 -

時鐘抖動

+關注

關注

1文章

63瀏覽量

16135 -

模擬信號

+關注

關注

8文章

1158瀏覽量

53278

發布評論請先 登錄

利用頻域時鐘抖動分析加快設計驗證過程

時鐘抖動(CLK)和相位噪聲之間的轉換

時鐘抖動時域分析

關于時鐘抖動的原因及查看途徑分析

關于時鐘抖動的原因及查看途徑分析

評論