FPGA 的基本結構包括可編程輸入輸出單元,可配置邏輯塊,數(shù)字時鐘管理模塊,嵌入式塊RAM,布線資源,內(nèi)嵌專用硬核,底層內(nèi)嵌功能單元。由于FPGA具有布線資源豐富,可重復編程和集成度高,投資較低的特點,在數(shù)字電路設計領域得到了廣泛的應用。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614026 -

嵌入式

+關注

關注

5141文章

19526瀏覽量

314885 -

RAM

+關注

關注

8文章

1391瀏覽量

116776

發(fā)布評論請先 登錄

相關推薦

熱點推薦

基于FPGA的除法器純邏輯設計案例

前邊寫了很多關于板上外圍器件的評測文章,這篇是FPGA純邏輯設計,是FPGA的另一部分——算法實現(xiàn),上篇文章做了HDC1000傳感器的使用,當時說FPGA是不支持小數(shù)的,本篇記述的是

如何快速入門FPGA?

快速入門FPGA可以遵循以下步驟:

理解FPGA基礎知識:

FPGA(Field Programmable Gate Array)即現(xiàn)場可編

發(fā)表于 04-28 08:54

如何快速入門FPGA

快速入門FPGA可以遵循以下步驟:

理解FPGA基礎知識:

FPGA(Field Programmable Gate Array)即現(xiàn)場可編

發(fā)表于 04-28 09:06

FPGA培訓--FPGA高級邏輯設計研修班

及路線圖詳見報到通知)四、 課程簡介本課程為期三天,旨在幫助已經(jīng)掌握一定設計基礎的工程師進一步了解FPGA邏輯設計的方法與優(yōu)化技巧。講述了邏輯設計的驗證、高級狀態(tài)機的設計、基于FPGA

發(fā)表于 07-24 13:13

急聘!FPGA邏輯設計部門經(jīng)理

部門內(nèi)邏輯開發(fā)問題的定位及排障工作;3.與軟件、硬件配合進行產(chǎn)品調(diào)試測試工作。 崗位要求: 1.從事FPGA相關開發(fā)經(jīng)驗在5年以上;2.精通常用接口邏輯,如DDR、SPI、LOCAL

發(fā)表于 01-21 14:42

邏輯設計是什么意思

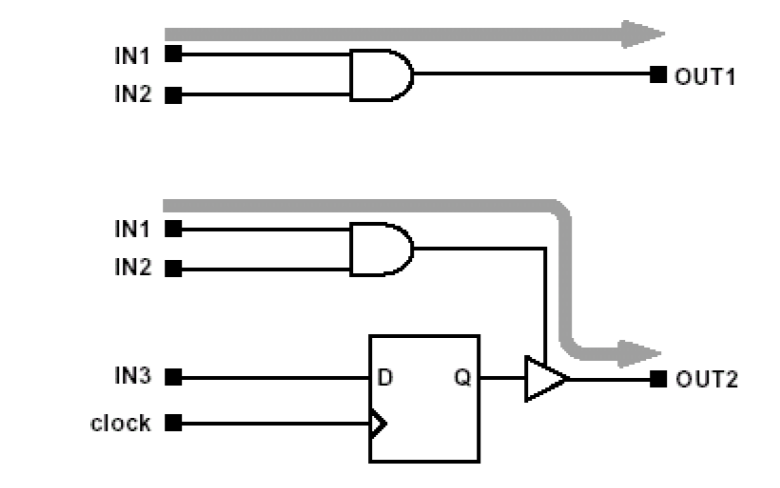

偏硬件:接口電路中的門組合電路;偏軟件:算法、接口控制器實現(xiàn)中的狀態(tài)機群或時序電路。隨著邏輯設計的深入,復雜功能設計一般基于同步時序電路方式。此時,邏輯設計基本上就是在設計狀態(tài)機群或計數(shù)器等時序電路

發(fā)表于 11-10 06:39

如何去實現(xiàn)FPGA的邏輯設計呢

前言FPGA 可以實現(xiàn)高速硬件電路,如各種時鐘,PWM,高速接口,DSP計算等硬件功能。這是Cortex-M 處理器軟件無法比擬的。要實現(xiàn)FPGA 的

發(fā)表于 12-21 06:13

基于FPGA的MDIO接口邏輯設計

本文介紹了一種基于FPGA 的用自定義串口命令的方式實現(xiàn)MDIO 接口邏輯設計的方法,并對系統(tǒng)結構進行了模塊化分解以適應自頂向下的設計方法。所有功能的實現(xiàn)全部采用VHDL 進行描

發(fā)表于 12-26 16:48

?103次下載

FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明

本文檔的主要內(nèi)容詳細介紹的是FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明免費下載。

發(fā)表于 03-27 10:56

?20次下載

華為FPGA硬件的靜態(tài)時序分析與邏輯設計

本文檔的主要內(nèi)容詳細介紹的是華為FPGA硬件的靜態(tài)時序分析與邏輯設計包括了:靜態(tài)時序分析一概念與流程,靜態(tài)時序分析一時序路徑,靜態(tài)時序分析一分析工具

發(fā)表于 12-21 17:10

?21次下載

快速入門FPGA硬件邏輯設計

快速入門FPGA硬件邏輯設計

評論