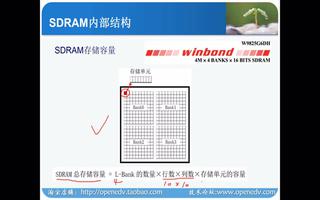

同步動態(tài)隨機存取內(nèi)存(synchronous dynamic random-access memory,簡稱SDRAM)是有一個同步接口的動態(tài)隨機存取內(nèi)存(DRAM)。通常DRAM是有一個異步接口的,這樣它可以隨時響應(yīng)控制輸入的變化。而SDRAM有一個同步接口,在響應(yīng)控制輸入前會等待一個時鐘信號,這樣就能和計算機的系統(tǒng)總線同步。時鐘被用來驅(qū)動一個有限狀態(tài)機,對進入的指令進行管線(Pipeline)操作。這使得SDRAM與沒有同步接口的異步DRAM(asynchronous DRAM)相比,可以有一個更復(fù)雜的操作模式。

-

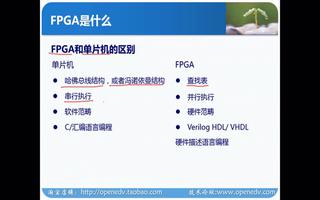

FPGA

+關(guān)注

關(guān)注

1645文章

22049瀏覽量

618405 -

SDRAM

+關(guān)注

關(guān)注

7文章

442瀏覽量

56310 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3124瀏覽量

75268

發(fā)布評論請先 登錄

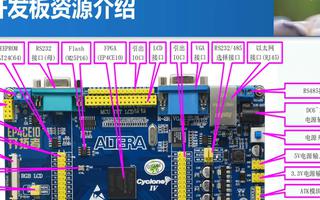

分享正點原子FPGA開發(fā)板全套資料

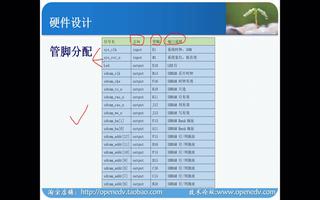

正點原子開拓者FPGA開發(fā)板資料連載第三十三章SDRAM讀寫測試

正點開拓者FPGA開發(fā)板使用問題

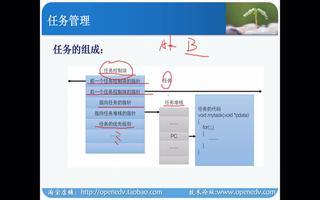

正點原子開拓者FPGA Qsys視頻:uCOS II任務(wù)管理與時間管理(2)

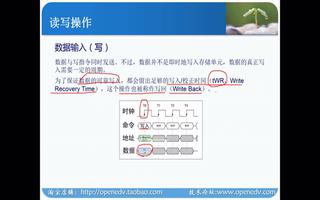

正點原子開拓者FPGA:SDRAM時序操作(2)

正點原子開拓者FPGA:SDRAM讀寫測試實驗

正點原子開拓者FPGA:SDRAM時序操作

正點原子開拓者FPGA:SDRAM時序操作

評論