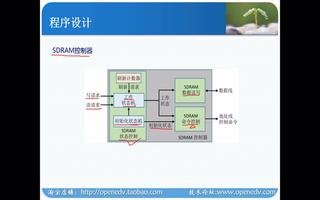

SDRAM具有多種工作模式,內(nèi)部操作是一個復(fù)雜的狀態(tài)機。SDRAM器件的引腳分為以下幾類。(1)控制信號:包括片選、時鐘、時鐘使能、行列地址選擇、讀寫有效及數(shù)據(jù)有效。(2)地址信號:時分復(fù)用引腳,根據(jù)行列地址選擇引腳,控制輸入的地址為行地址或列地址。(3)數(shù)據(jù)信號:雙向引腳,受數(shù)據(jù)有效控制。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613911 -

控制

+關(guān)注

關(guān)注

5文章

1021瀏覽量

123521

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

FPGA讀寫SDRAM的實例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計論文

,SDRAM的原理和時序,SDRAM控制器,動態(tài)隨即存儲器SDRAM模塊功能簡介,基于FPGA的SDRA

發(fā)表于 12-25 08:00

?57次下載

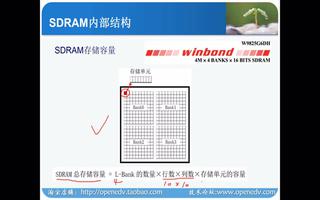

正點原子開拓者FPGA視頻:SDRAM簡介

同步動態(tài)隨機存取內(nèi)存(synchronous dynamic random-access memory,簡稱SDRAM)是有一個同步接口的動態(tài)隨機存取內(nèi)存(DRAM)。通常DRAM是有一個異步接口

基于FPGA的DDR3SDRAM控制器設(shè)計及實現(xiàn)簡介

基于FPGA的DDR3SDRAM控制器設(shè)計及實現(xiàn)簡介(arm嵌入式開發(fā)平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計及實現(xiàn)

發(fā)表于 07-30 09:05

?7次下載

基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)簡介

基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)簡介(嵌入式開發(fā)工程師和基層公務(wù)員)-該文檔為基于FPGA的SDRAM控制器的設(shè)計與實現(xiàn)

發(fā)表于 07-30 09:34

?11次下載

【正點原子FPGA連載】第三章 硬件資源詳解 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

【正點原子FPGA連載】第三章 硬件資源詳解 -摘自【正點原子】新起點之

發(fā)表于 11-21 14:06

?19次下載

【正點原子FPGA連載】第二十五章HDMI方塊移動實驗 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

【正點原子FPGA連載】第二十五章HDMI方塊移動實驗 -摘自【正點原子】新起點之

發(fā)表于 11-24 14:36

?13次下載

【正點原子FPGA連載】第九章按鍵控制LED燈實驗 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

【正點原子FPGA連載】第九章按鍵控制LED燈實驗 -摘自【正點原子】新起點之

發(fā)表于 12-04 13:06

?10次下載

【正點原子FPGA連載】第三十五章高速AD/DA實驗 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

【正點原子FPGA連載】第三十五章高速AD/DA實驗 -摘自【正點原子】新起點之

發(fā)表于 12-04 15:06

?12次下載

正點原子FPGA之SDRAM:SDRAM簡介

正點原子FPGA之SDRAM:SDRAM簡介

評論