緊耦合就是模塊或者系統(tǒng)之間關系太緊密,存在相互調用。緊耦合系統(tǒng)的缺點在于更新一個模塊的結果導致其它模塊的結果變化,難以重用特定的關聯(lián)模塊。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614052 -

耦合

+關注

關注

13文章

595瀏覽量

101486 -

存儲

+關注

關注

13文章

4502瀏覽量

87065

發(fā)布評論請先 登錄

相關推薦

熱點推薦

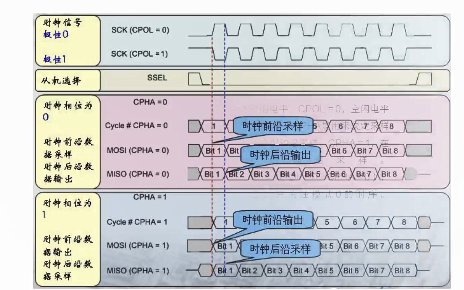

FPGA實戰(zhàn)演練邏輯篇55:VGA驅動接口時序設計之2源同步接口

VGA驅動接口時序設計之2源同步接口本文節(jié)選自特權同學的圖書《FPGA設計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 好,有了

發(fā)表于 07-29 11:19

基于NIOS II的SOPC中存儲器型外設接口的設計

器FIFO、緊耦合存儲器及16位的SRAM集成在SOPC系統(tǒng)中,并在FPGA開發(fā)板上實現的方法,其內容包括外設的接入方法,以及緊

發(fā)表于 12-07 10:27

使用Nios II緊耦合存儲器教程

使用Nios II緊耦合存儲器教程 Chapter 1. Using Tightly Coupled Memory with the Nios II Processor Reasons

發(fā)表于 10-17 14:43

?48次下載

FPGA之軟核演練篇:DMA傳輸的過程步驟介紹

DMA方式主要適用于一些高速的I/O設備。這些設備傳輸字節(jié)或字的速度非常快。對于這類高速I/O設備,如果用輸入輸出指令或采用中斷的方法來傳輸字節(jié)信息,會大量占用CPU的時間,同時也容易造成數據

FPGA 系統(tǒng)中的處理器核們(二):軟核,可殺雞亦可屠龍?

在前文中,我們了解到兩種 FPGA 嵌入式處理器核方案:軟核與硬核。本文將展開討論軟核在一個基于

發(fā)表于 02-07 10:07

?3次下載

FPGA之軟核演練篇:緊耦合指令或數據存儲端口

FPGA之軟核演練篇:緊耦合指令或數據存儲端口

評論