PLL介紹

PLL,即鎖相環(huán)。簡單的理解,給PLL一一個時鐘輸入(--般是外部晶振時鐘),然后經(jīng)過PLL內(nèi)部的處理以后,在PLL的輸出端口就可以得到一定范圍的時鐘頻率。其之所以應(yīng)用廣泛,因為從PLL輸出得到的時鐘不僅僅從頻率和相位上比較穩(wěn)定,而且其時鐘網(wǎng)絡(luò)延時也相比內(nèi)部邏輯產(chǎn)生的分頻時鐘要小得多。”下面就如何配置一一個PLL做一些說明。

PLL的配置需求

假定設(shè)計者已經(jīng)新建了-一個工程,然后需要配置-一個PLL。該P(yáng)LL的輸入時鐘為FPGA外部的25MHz晶振,希望得到一個50MHz(輸入時鐘的2倍頻)的系統(tǒng)時鐘供FPGA內(nèi)部使用。該P(yáng)LL的輸入輸出接口如表5.22所示。

PLL設(shè)置序列

要使PLL初始化運(yùn)行,那么必須按步驟完成下面的序列:

1.如果PLL已被連接,則用一個饋送序列斷開與PLL的連接。

2.用一個饋送序列禁止PLL。

3.如果需要,在沒有PLL的情況下改變CPU時鐘分頻器設(shè)置來加速操作。

4.寫時鐘源選擇控制寄存器來改變時鐘源。

5.寫PLLCFG并用一個饋送序列使其有效。PLLCFG僅可在PLL被禁止時更新。

6.用一個饋送序列使能PLL。

7.改變CPU時鐘分頻器設(shè)置使之與PLL一起操作。在連接PLL之前完成這個操作是很重要的。

8.通過監(jiān)控PLLSTAT寄存器的PLOCK位或使用PLOCK中斷來等待PLL實現(xiàn)鎖定,或當(dāng)PLL的輸入時鐘為低(也就是32kHz)時等待一個固定的時間。當(dāng)PLL參考頻率(REFCLK的頻率FREF與預(yù)分頻器值分頻所得的PLL輸入頻率相等)少于100kHz或大于20MHz時,PLOCK的值可能不穩(wěn)定。在這些情況下,可以假設(shè)PLL在啟動時間過后穩(wěn)定下來。當(dāng)FREF大于400kHz時,這個時間為500μs;當(dāng)FREF少于400kHz時,這個時間為200/FREF秒。

9.用一個饋送序列連接PLL。

具體的PLL的配置步驟請跟著視頻操作。

-

開發(fā)板

+關(guān)注

關(guān)注

25文章

5680瀏覽量

104713 -

SF-EP1C

+關(guān)注

關(guān)注

0文章

9瀏覽量

2870

發(fā)布評論請先 登錄

【Banana Pi BPI-RV2開發(fā)板試用體驗】開箱上電

基于DE1-SOC開發(fā)板的oneAPI實驗教程(2)

瑞芯微RK3506開發(fā)板之Qt應(yīng)用開發(fā)手冊(上) 深圳觸覺智能出品,嵌入式方案商

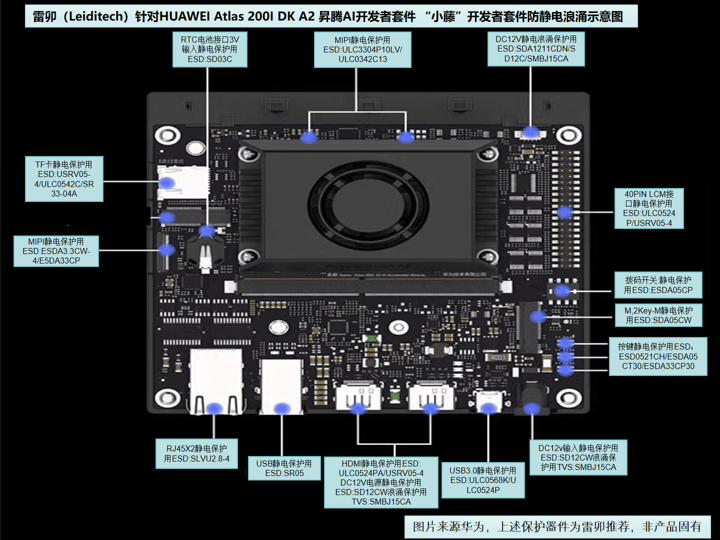

雷卯收集AI實驗課程開發(fā)板

【新品】ESP32-P4全功能開發(fā)板,啟明云端WT99P4C5-S1多媒體開發(fā)板強(qiáng)勢來襲!

飛凌嵌入式ElfBoard ELF 1板卡-開發(fā)板適配之CSI

Air780EP之RC522開發(fā)板,你了解嗎?

4G通信先鋒:Air780EP開發(fā)板與RC522的結(jié)合

設(shè)計TMS320C548/9 DSP開發(fā)板

低功耗4G模組:Air780EP開發(fā)板RC522實例

北京迅為RK3568開發(fā)板嵌入式學(xué)習(xí)之Linux驅(qū)動全新更新-CAN+

合宙LuatOS開發(fā)板Core_Air780EP使用說明

SF-EP1C開發(fā)板之PLL配置仿真實驗

SF-EP1C開發(fā)板之PLL配置仿真實驗

評論