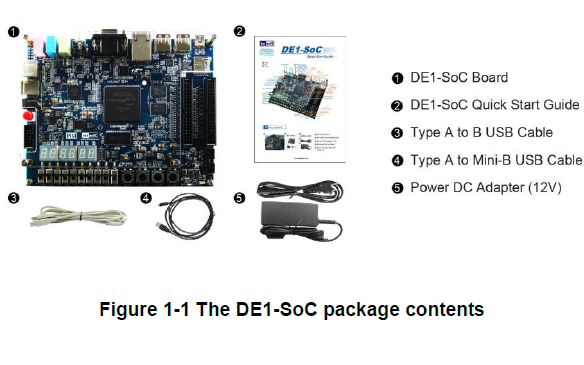

本期我們介紹在DE1-SoC開發板的FPGA上實現并部署Simple DMA和Simple Adder兩個案例。

上一期我們從oneAPI CLI Samples Browser復制保存的Simple DMA是基于Quartus Pro的Nios V示例,無法直接用在DE1-SoC開發板上,因此這一節我們用的Simple DMA是基于Quartus Standard的Nios II 示例,后續會計劃用新版Quartus Standard軟件將DE1-SoC的oneAPI示例升級到Nios V。

注:請復制鏈接http://mail.terasic.com.cn/~bingxia/My_First_oneAPI_de1_soc.zip到瀏覽器去下載My_First_oneAPI_de1_soc BSP,內含example code。

一、配置Simple DMA IP

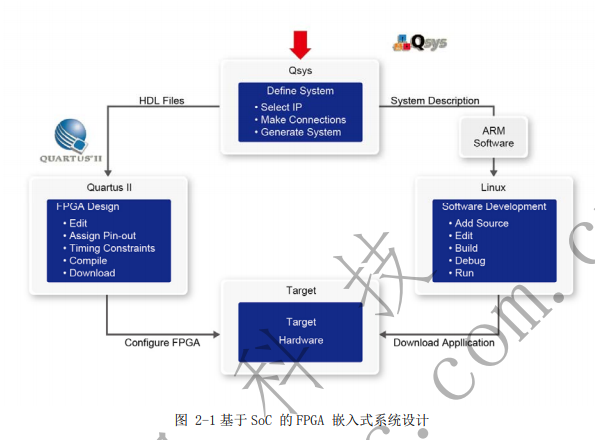

使用oneAPI DPC++/C++編譯器可以將Simple DMA編譯成RTL IP硬件模塊,然后將RTL IP集成到FPGA,使用Plarform Designer可以將該IP核集成到設計中。

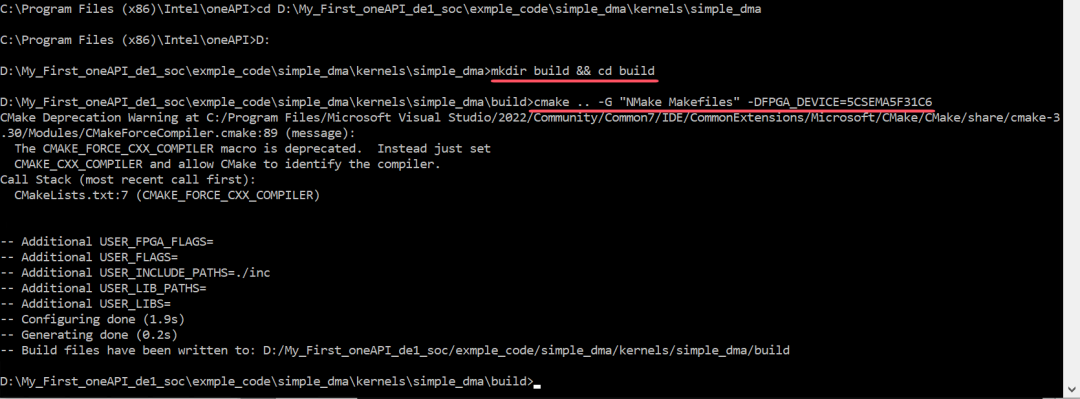

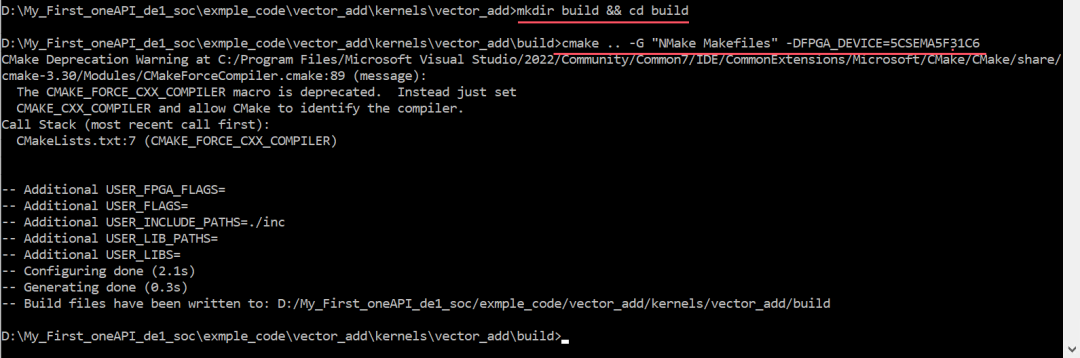

1. 打開Intel oneAPI命令窗口,切換到My_First_oneAPI_de1_socexmple_codesimple_dmakernelssimple_dma路徑,執行以下命令創建build文件夾,并指定FPGA為DE1-SoC開發板的5CSEMA5F31C6。

mkdir build && cd build

cmake .. -G "NMake Makefiles" -DFPGA_DEVICE=5CSEMA5F31C6

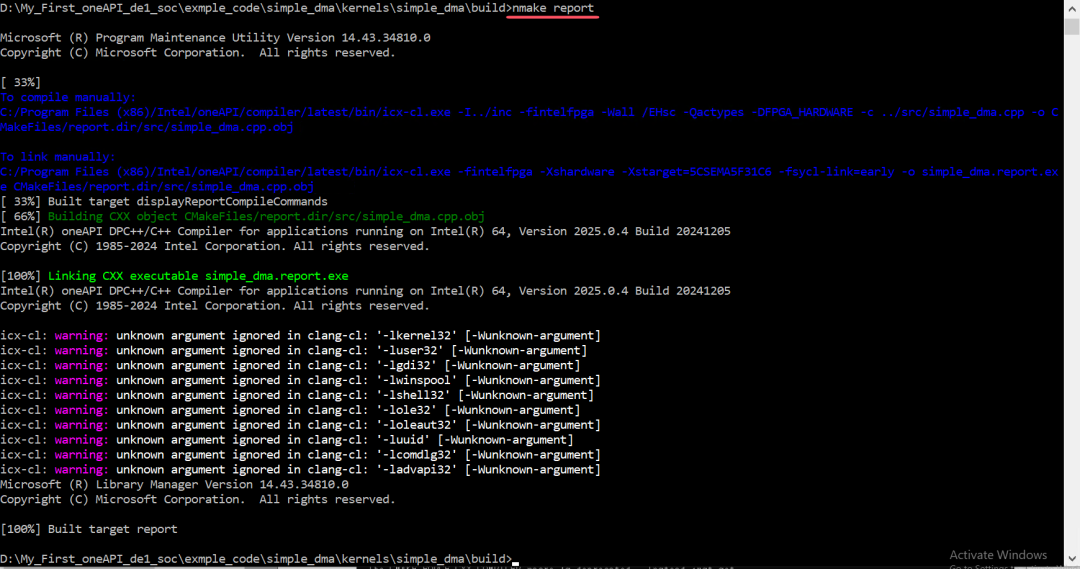

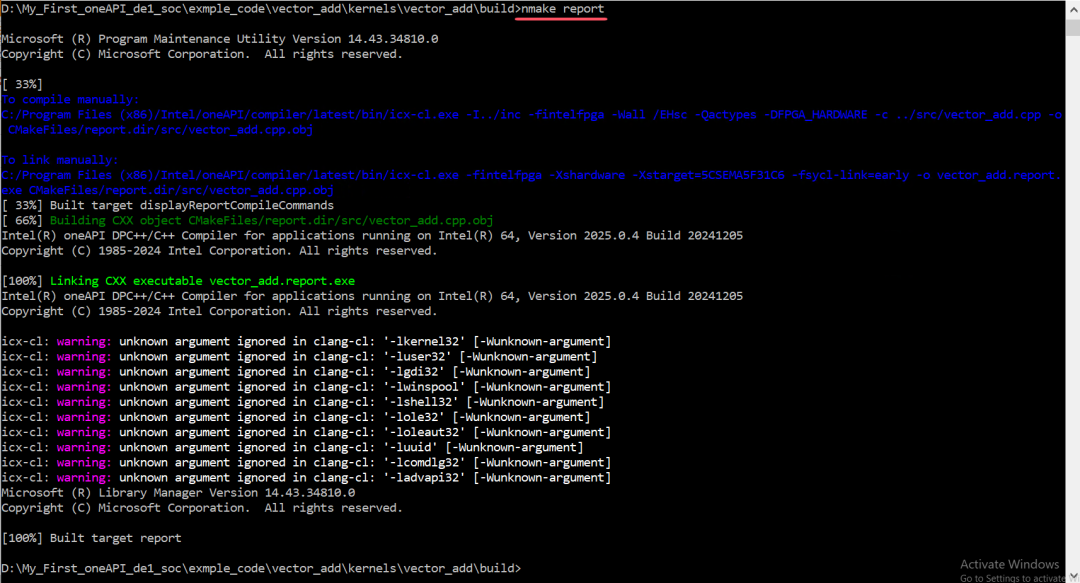

2. 執行nmake report編譯DMA IP,生成IP組件及優化報告。

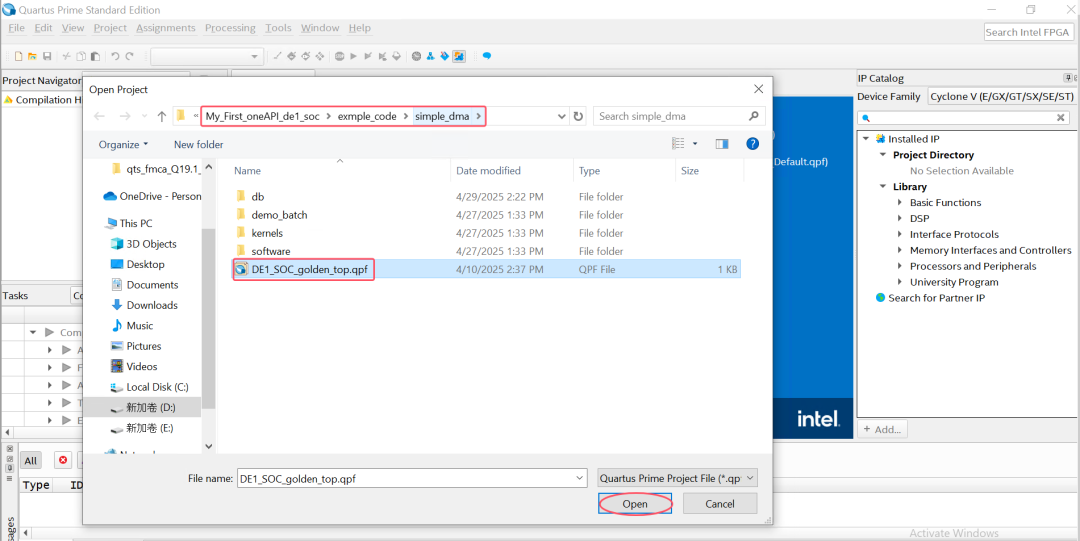

3. 打開My_First_oneAPI_de1_socexmple_codesimple_dma路徑下的Quartus工程。

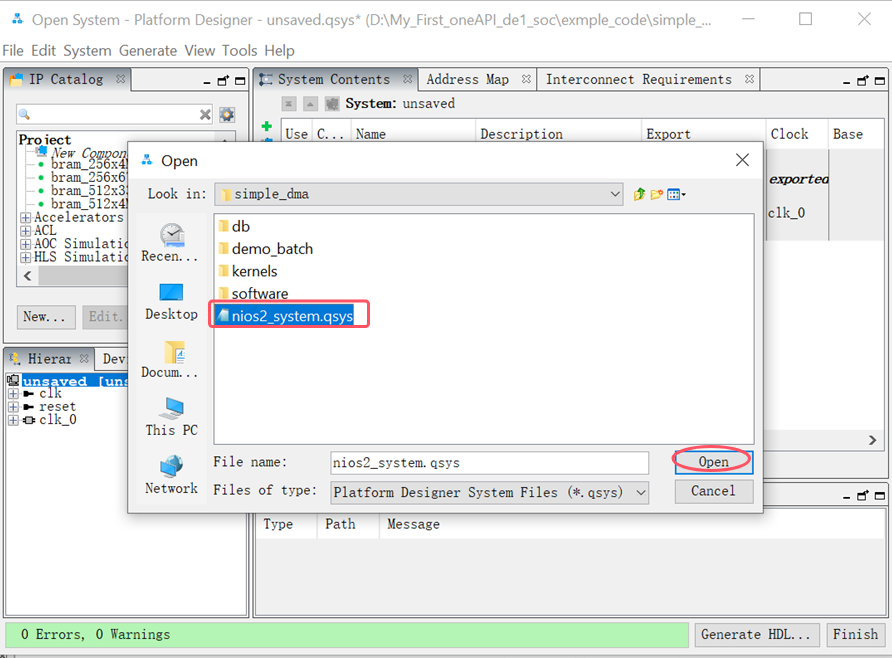

4. 從Quartus Tools菜單欄里打開Platform Designer,并打開simple_dma/nios2_system.qsys工程。

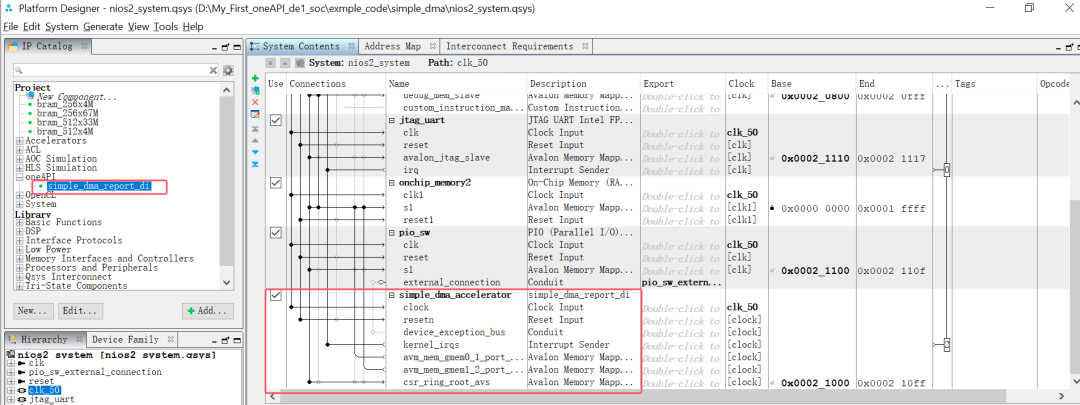

5. 在nios2_system.qsys里添加oneAPI -->simple_dma_report_di IP,并按下圖所示連接,再完成Assign Base Addresses。

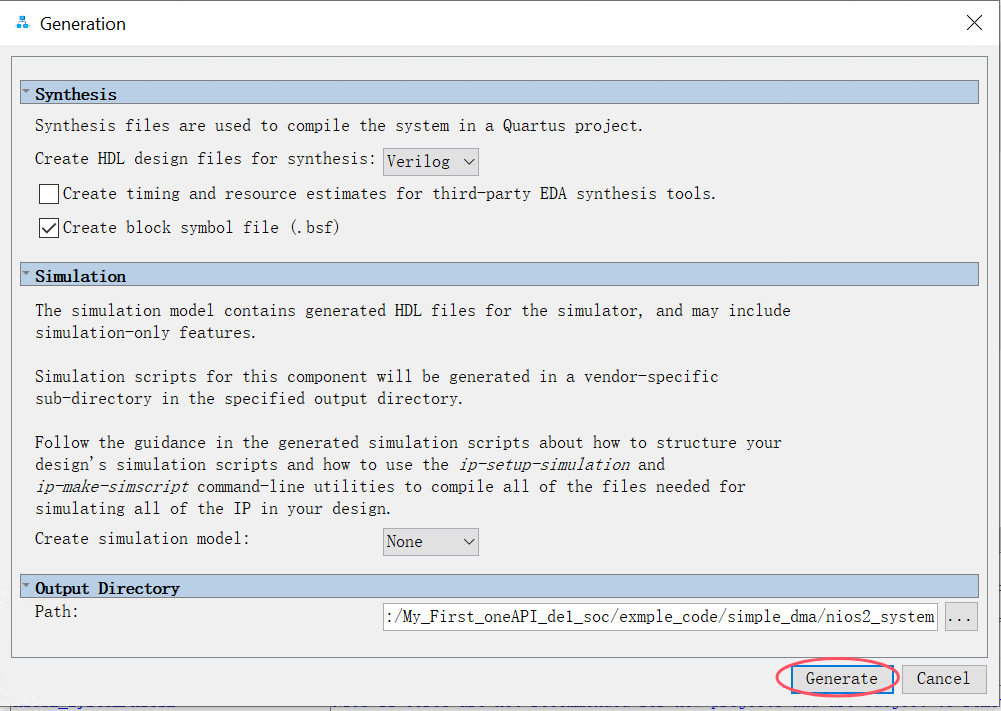

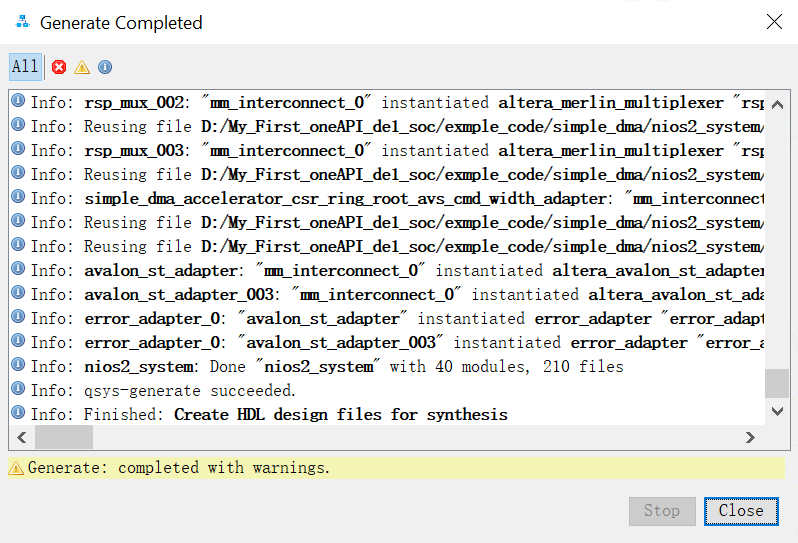

6. 點擊Generate HDL-->Generate,生成HDL代碼。

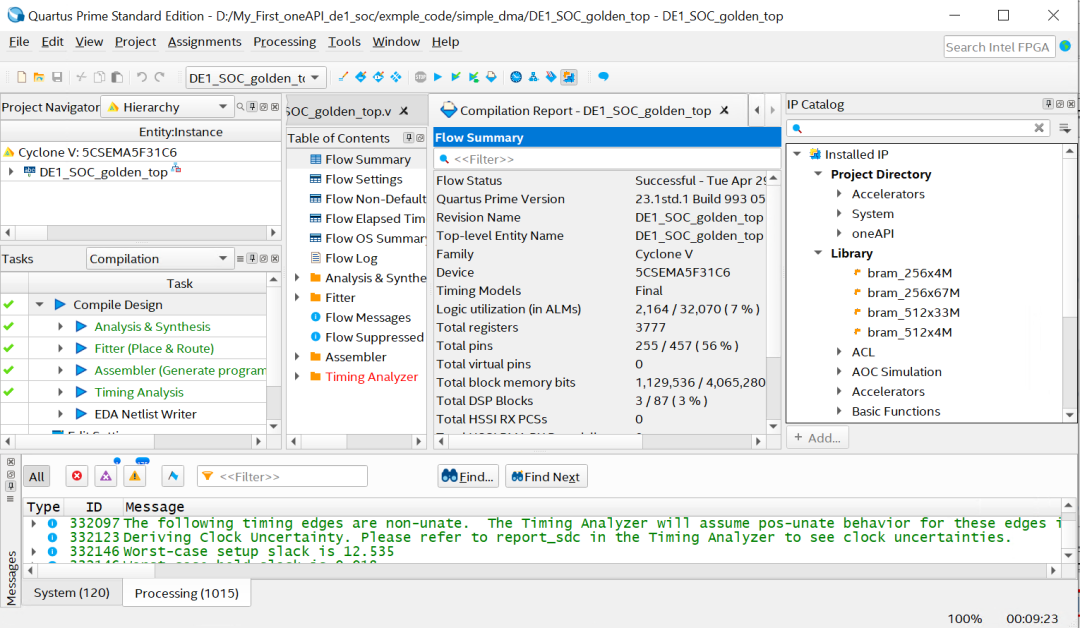

7. 編譯Quartus工程。

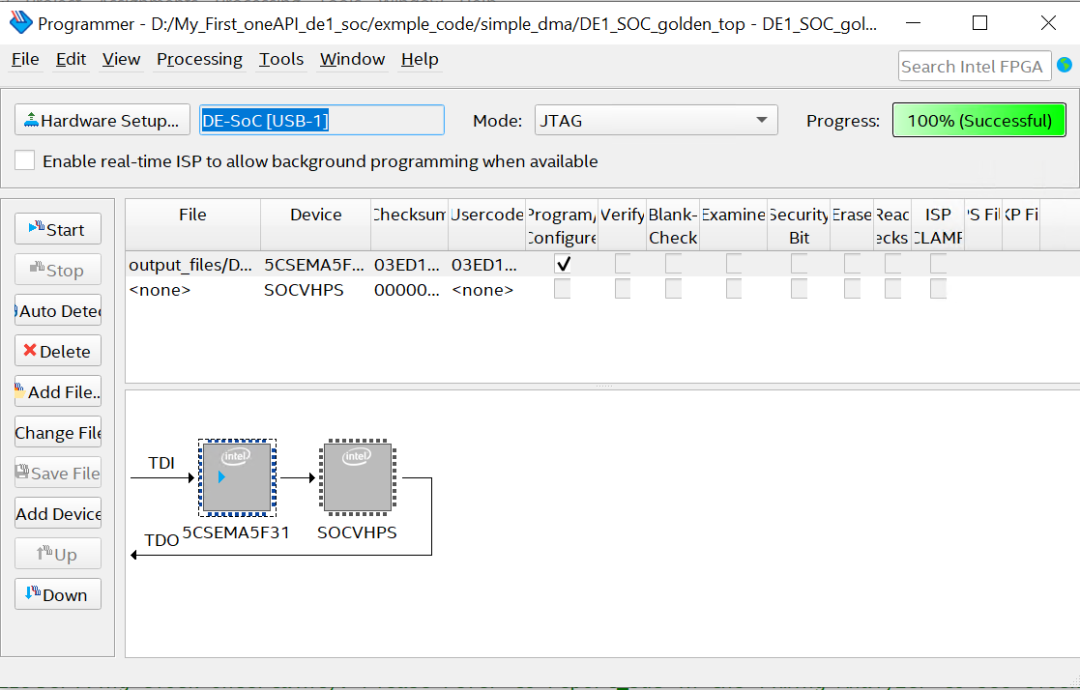

8. 將編譯生成的.sof文件燒錄到FPGA。

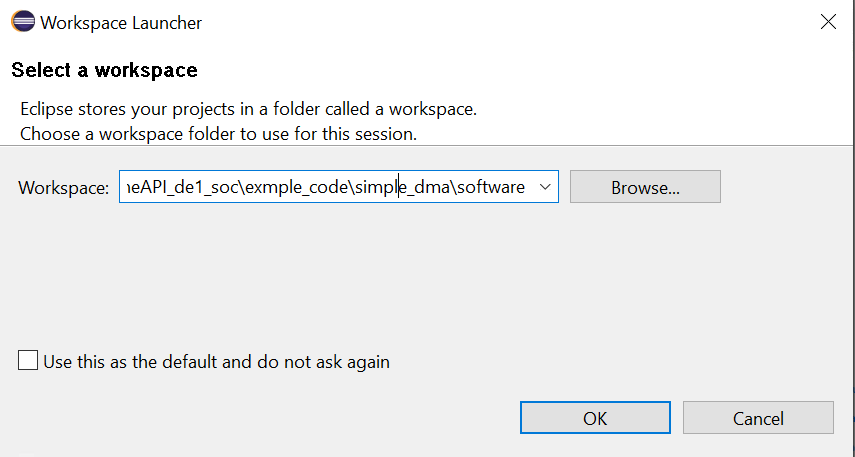

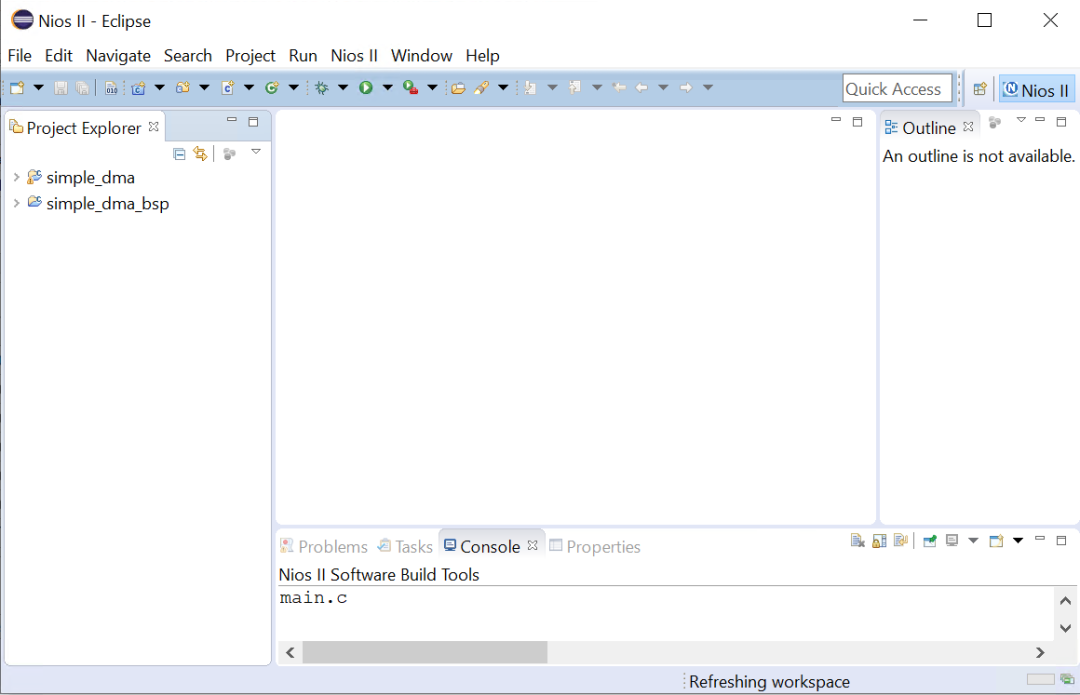

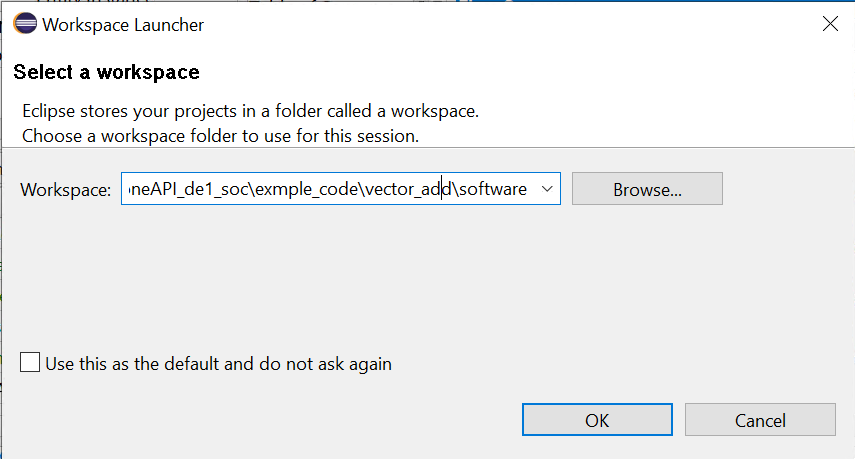

9. 從Quartus Tools里打開Nios II Software Build Tools for Eclipse,workspace切換到simple_dma/software。

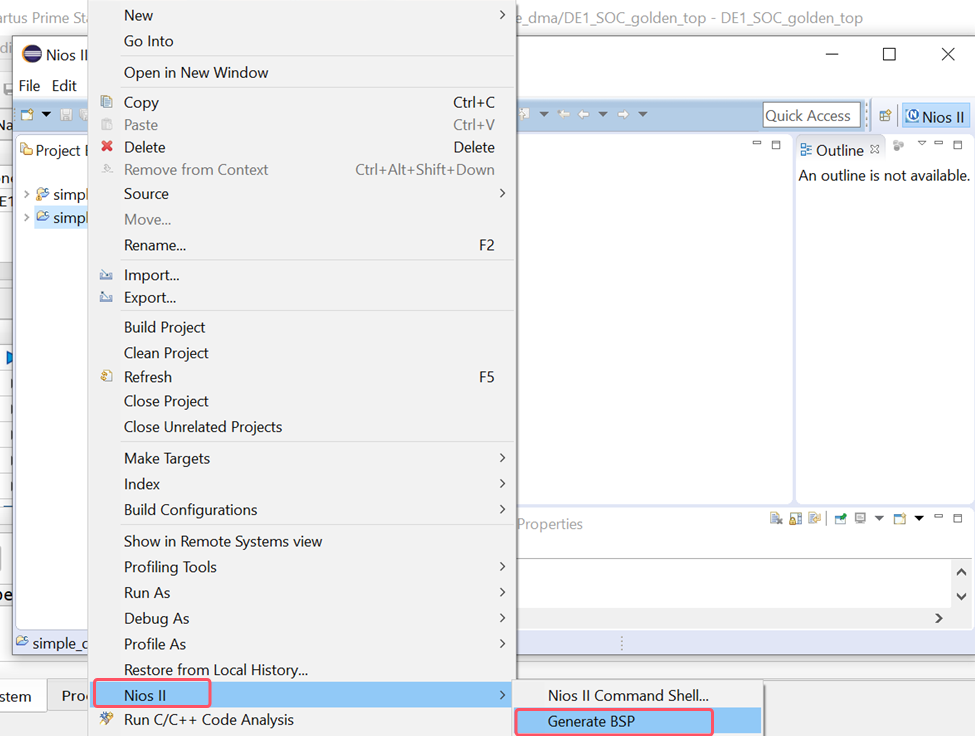

10. 右鍵點擊simple_dma_bsp,選擇Nios II > Generate BSP。

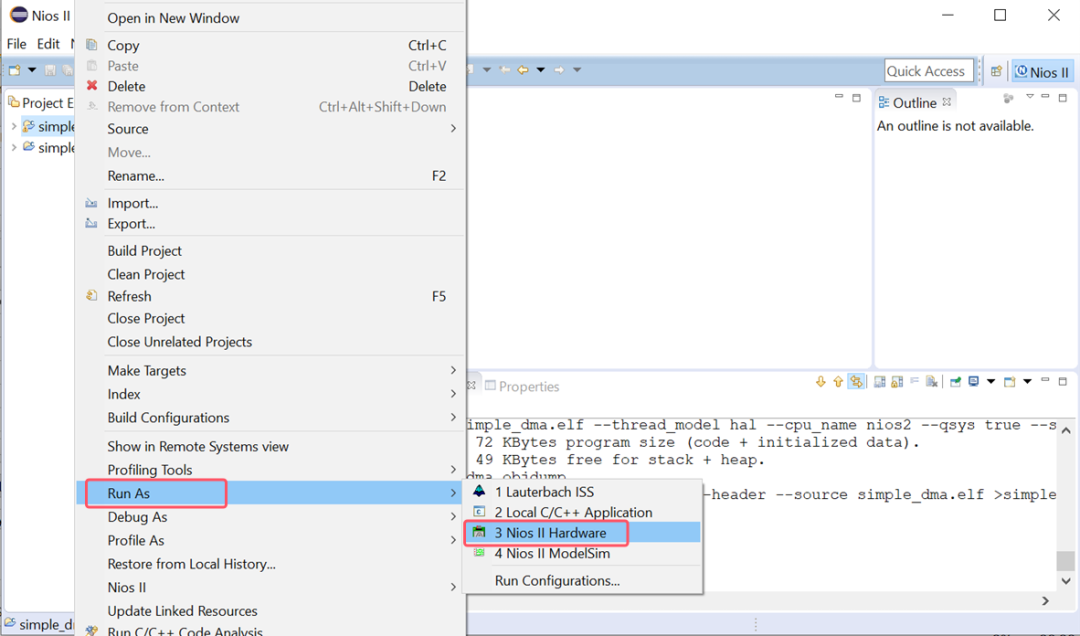

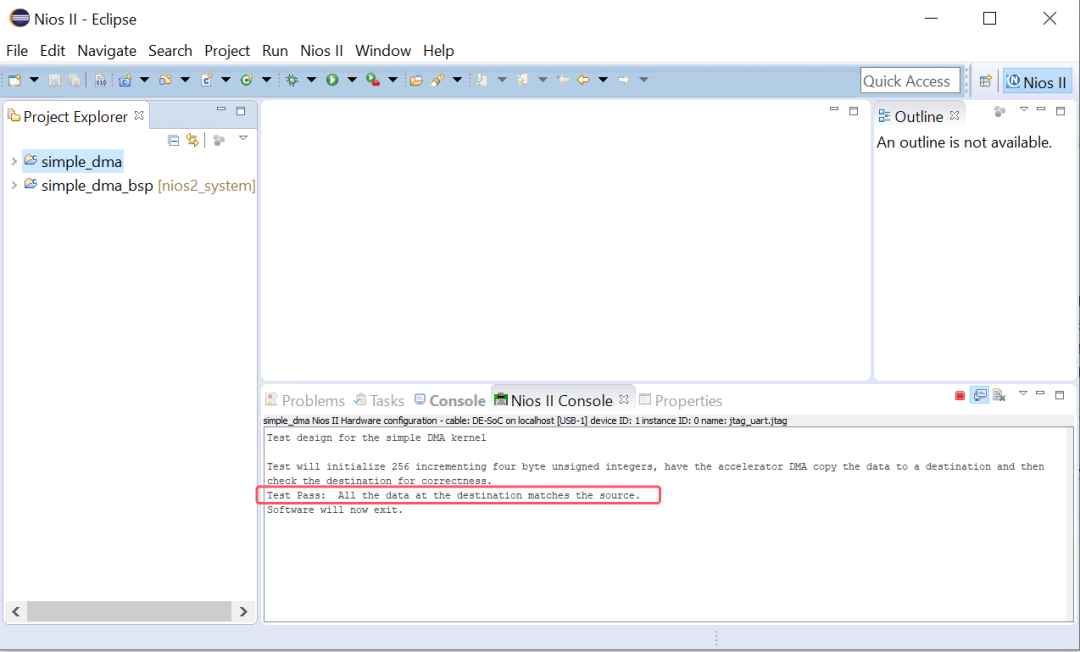

11. 右鍵點擊simple_dma -->Run As --> 3 Nios II Hardware。

12. 在Nios II Console終端上會顯示程序運行結果。

二、修改Simple DMA為Simple Adder

本節通過對Simple DMA設計進行擴展,添加基本算術功能,將其轉換為Simple Adder。在保留原有DMA數據傳輸機制的同時引入兩種類型的常量輸入: c1--通過conduit接口提供;c2--通過CSR(Control and Status Register)配置。

在傳輸過程中,這些常量會被添加到數據中,這為如何在FPGA上集成數據處理和控制邏輯提供了一個示例。

接下來我們將解釋如何配置和使用conduit接口與CSR接口以及它們之間的差異,并演示如何在Platform Designer中連接這些接口。我們還將介紹完整的開發流程,包括從SYCL(基于 C++ 的開放標準,用于簡化異構計算如 CPU、GPU、FPGA 等并行設備的編程)示例代碼編譯到IP生成、Quartus集成、硬件配置以及在FPGA上驗證結果。

conduit接口

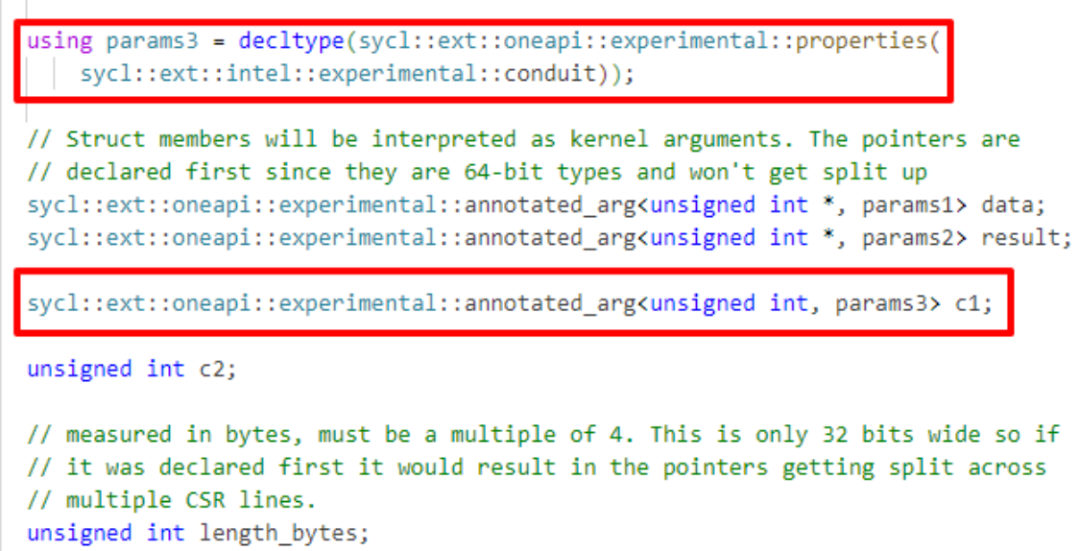

SYCL示例代碼(My_First_oneAPI_de1_socexmple_codevector_addkernelsvector_addsrcvector_add.cpp)如下,將其配置成conduit。

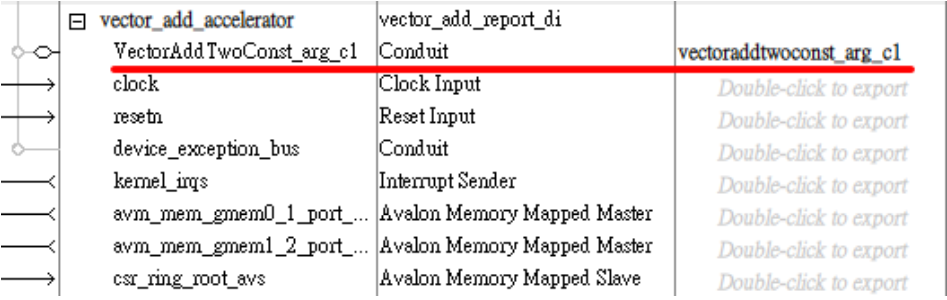

將代碼轉換為RTL IP后,該接口就可以在Platform Designer中看到。

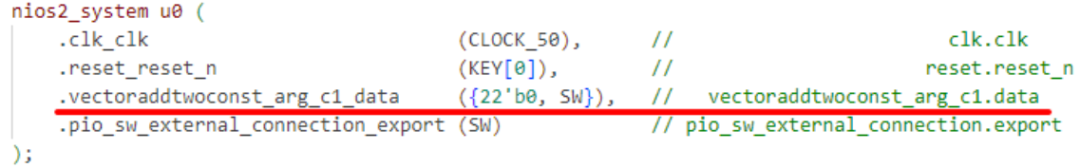

導出conduit接口,并在DE1_SOC_golden_top.v文件中例化連接到DE1-SoC開發板的滑動開關。

控制狀態寄存器

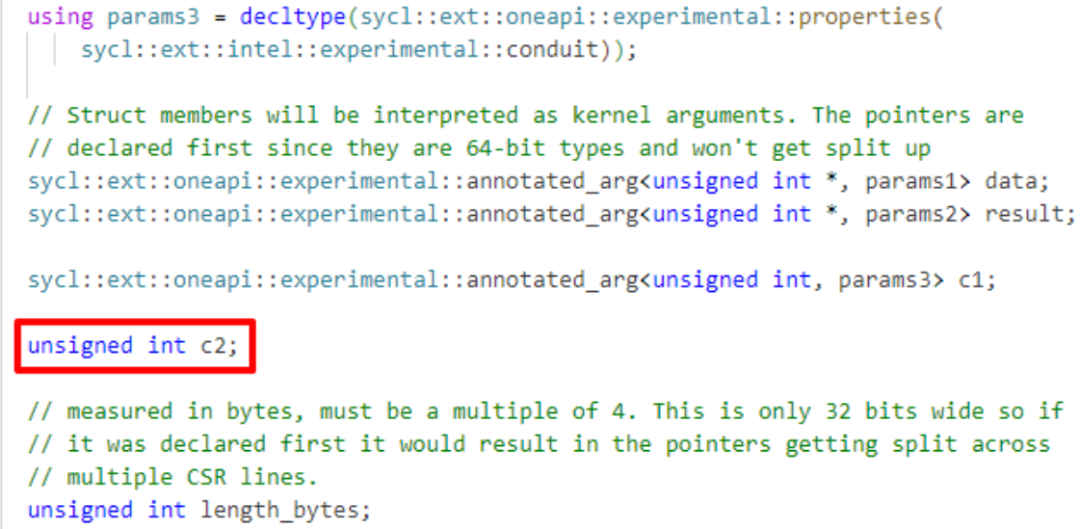

常量c2使用控制狀態寄存器(CSR)來定義。在內核中聲明此變量時,不需要額外的參數,默認為控制狀態寄存器(CSR)。

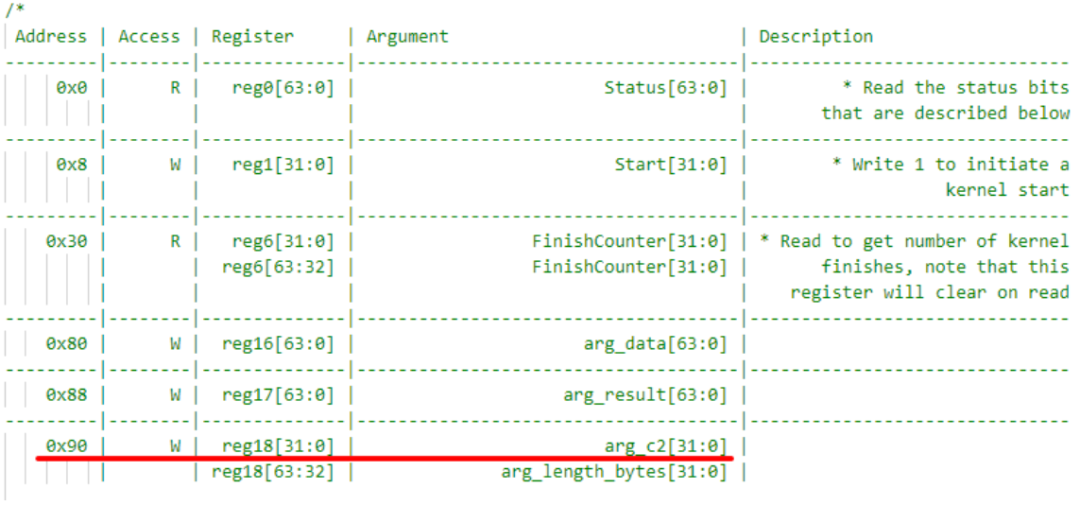

c2的寄存器偏移自動產生,可在kernels/vector_add/build/vector_add.report.prj/include/kernel_headers/VectorAddTwoConst_register_map.h中找到。

測試步驟

按照以下步驟在DE1-SoC開發板的FPGA上實現并部署Simple Adder。

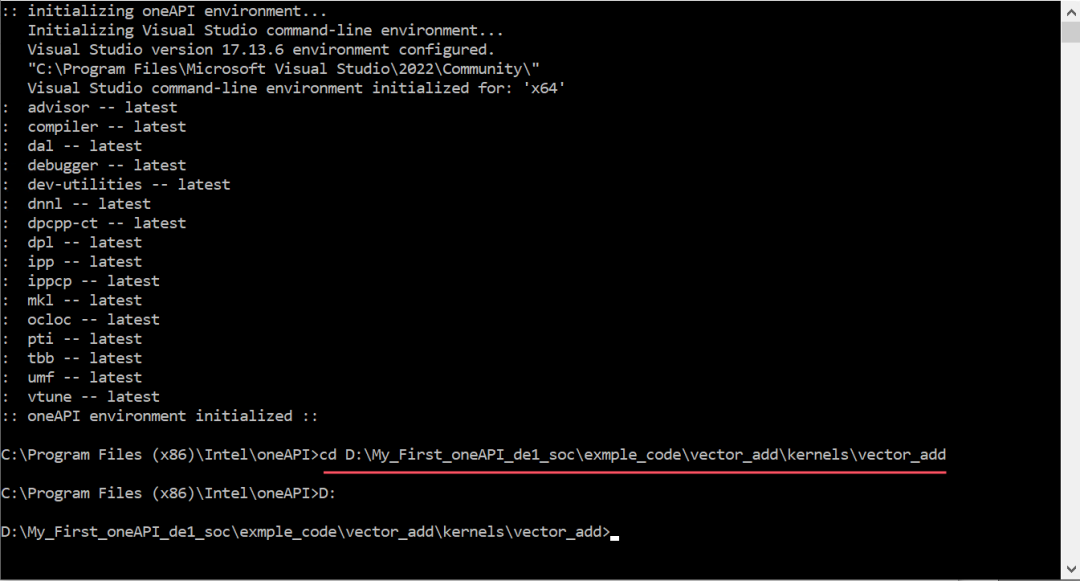

1. 打開Intel oneAPI 命令窗口,執行chcp 65001命令將語言編碼更改為UTF-8,并切換到My_First_oneAPI_de1_socexmple_codevector_addkernelsvector_add路徑。

2. 執行以下命令創建并切換到build文件夾,以及指定FPGA為DE1-SoC開發板的5CSEMA5F31C6。

mkdir build && cd build

cmake .. -G "NMake Makefiles" -DFPGA_DEVICE=5CSEMA5F31C6

3. 執行nmake report命令編譯Simple Adder IP,生成IP組件以及優化報告。

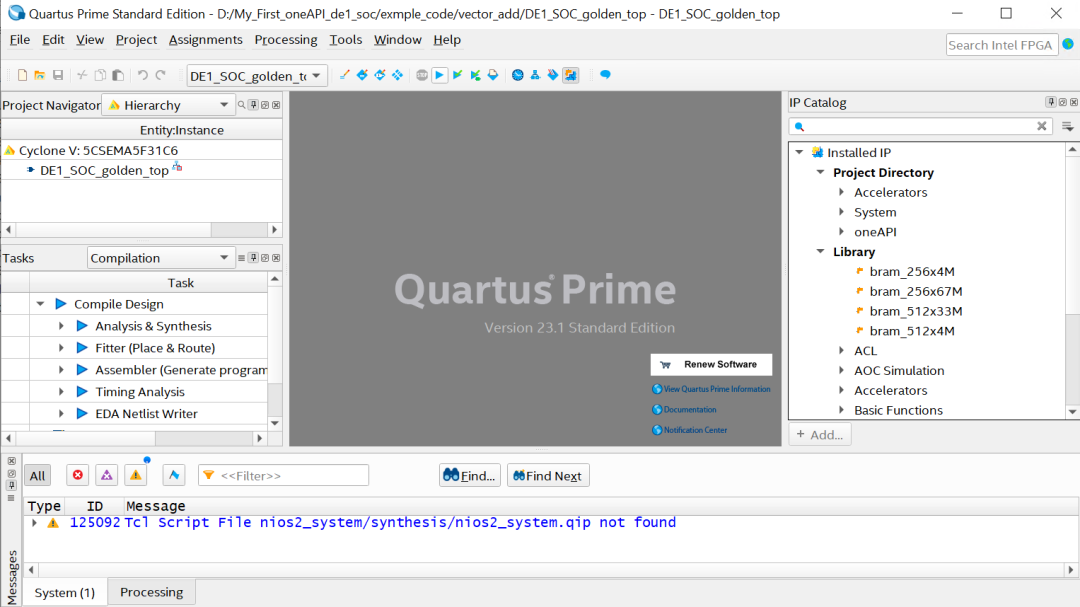

4. 打開DE1_SOC_golden_top.qpf工程。

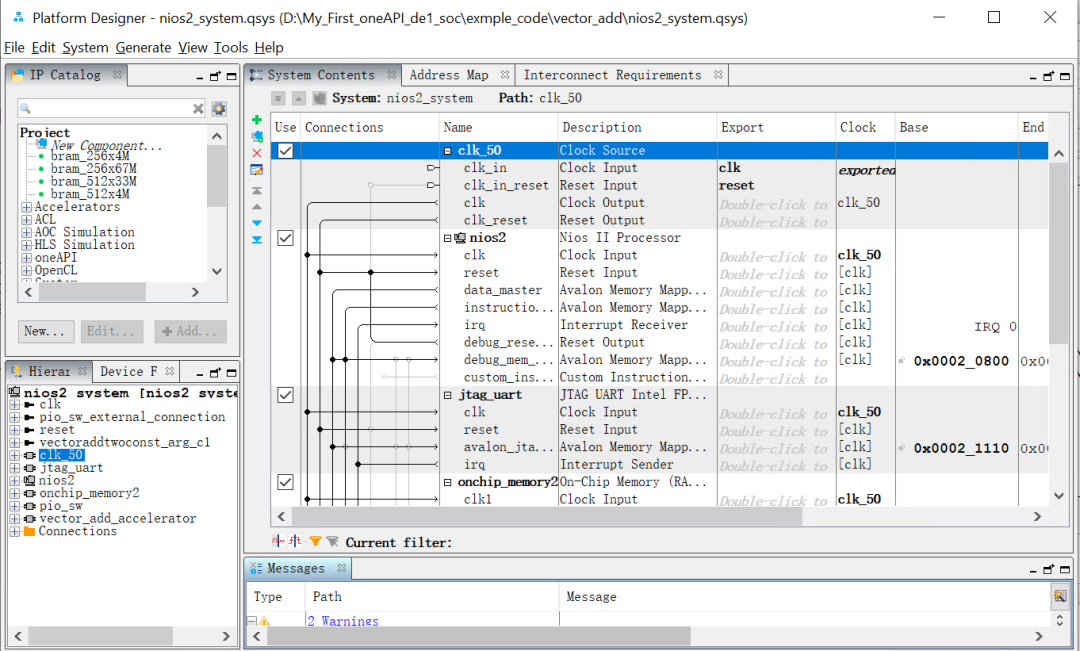

5. 打開vector_add/nios2_system.qsys工程。

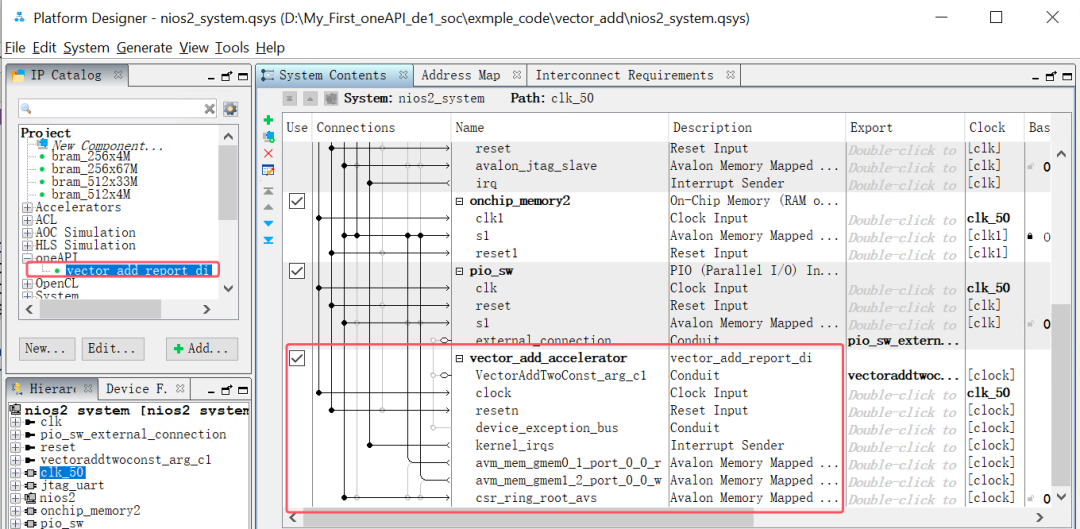

6. 添加oneAPI里的vector_add_report_di,并按下圖所示連接。

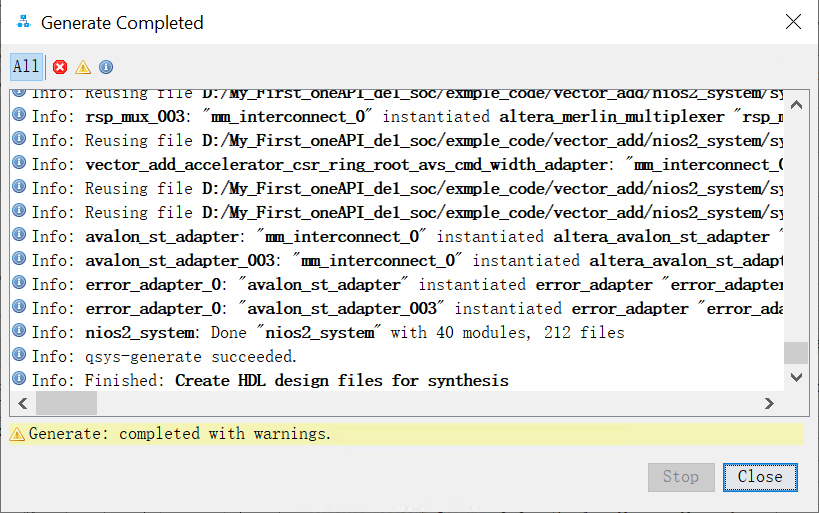

7. 點擊Generate HDL-->Generate生成HDL。

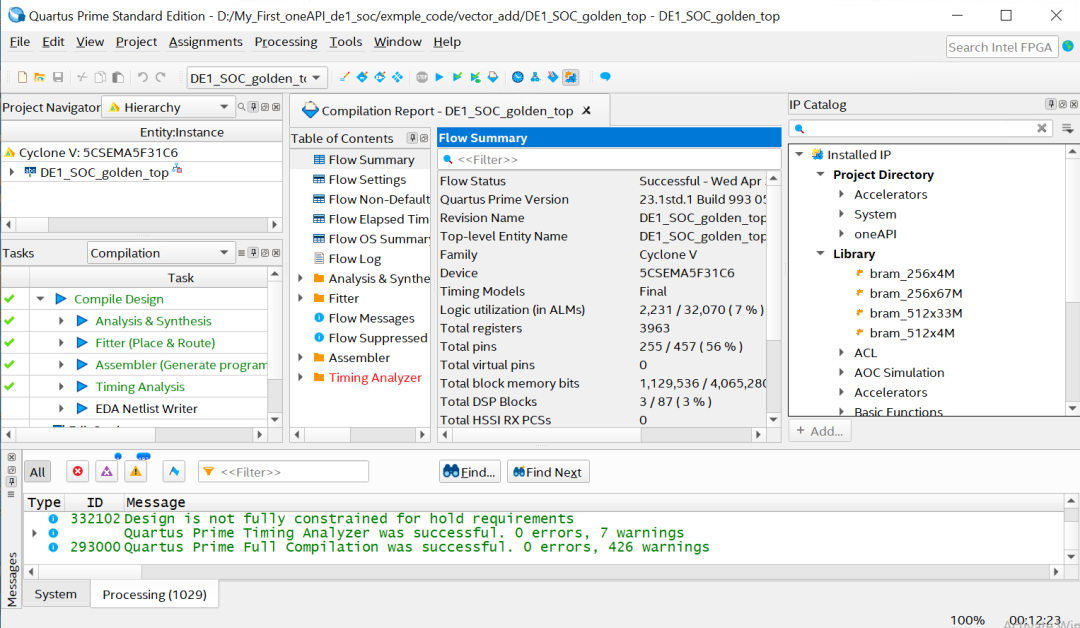

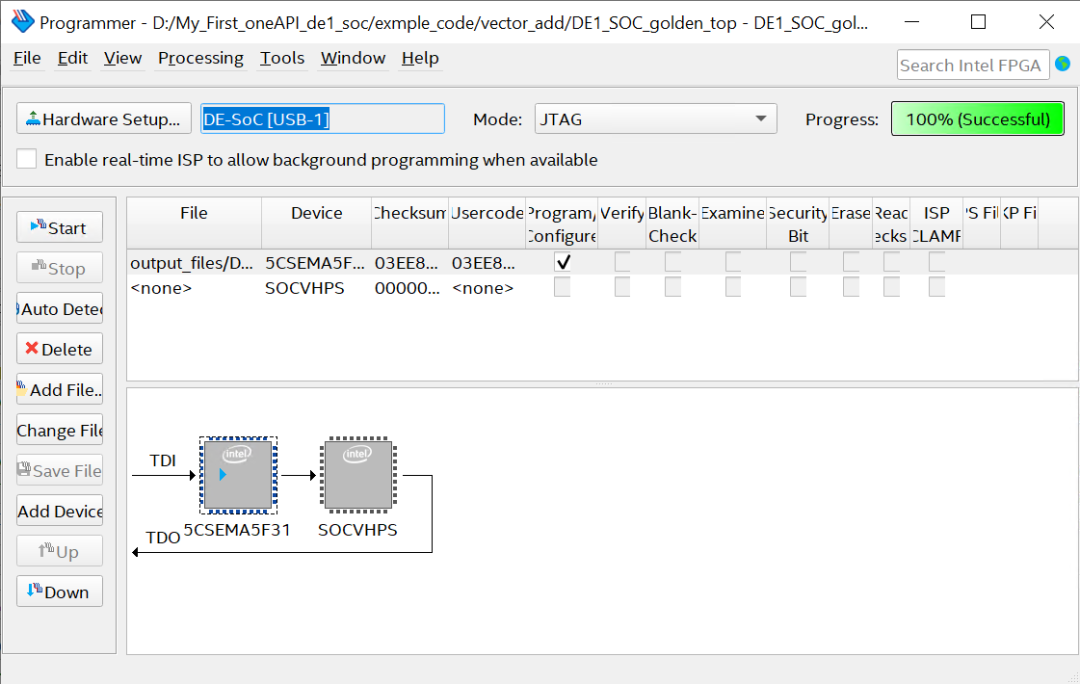

8. 編譯Quartus工程,并將生成的.sof燒錄到FPGA。

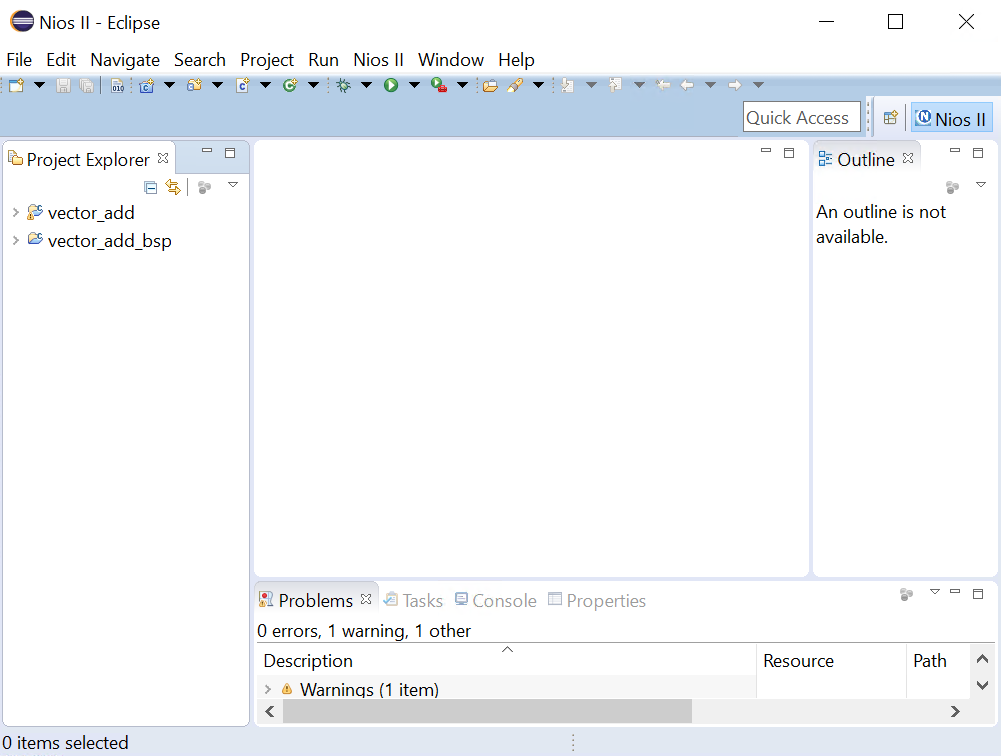

9. 運行Nios II Software Build Tools for Eclipse,將workspace切換到vector_add/software。

10. 右鍵點擊vector_add_bsp,選擇Nios II -->Generate BSP,生成BSP;右鍵點擊vector_add選擇Build Project編譯工程。

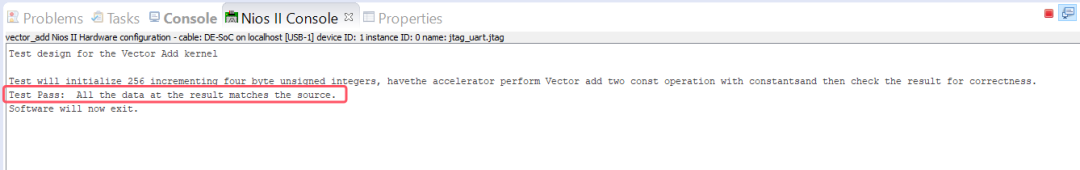

11. 右鍵點擊vector_add,選擇Run As > 3 Nios II Hardware,燒錄.elf文件運行工程。然后在Nios II Console終端顯示結果。

三、Q&A

1. Quartus Standard v23.1的Nios II Software Build Tools for Eclipse如果無法運行起來,請參考Getting Start Install Eclipse IDE into Nios EDS文檔里的步驟安裝Eclipse IDE。

2. vector_add Nios II工程無法編譯,請參考Getting Start Install WSL安裝WSL。

-

FPGA

+關注

關注

1644文章

21998瀏覽量

615630 -

dma

+關注

關注

3文章

575瀏覽量

102621 -

開發板

+關注

關注

25文章

5593瀏覽量

103246 -

編譯器

+關注

關注

1文章

1658瀏覽量

49992

原文標題:基于DE1-SoC的My_First_oneAPI(二)

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于DE1-SOC開發板的oneAPI實驗教程(1)

DE1-SOC新貨轉讓

DE1-SoC官方自帶ControlPanel代碼解讀與AV圖像采集處理?

大神幫忙看看,為什么我的開發板無法用電腦進行配置

小弟求購Altera DE1-SOC開發板,哪位大神玩剩下了傳承一下,多謝!

de1-soc FPGA(Quartus工程含Qsys系統) + HPS 操作步驟

Altera DE2 開發板測試說明

如何在DE1-SOC開發板上搭建NIOS II處理器運行UCOS

DE1-SoC開發工具包的詳細用戶和使用手冊資料免費下載

ALTERA公司的DE1 SoC FPGA開發板的培訓教程免費下載

基于DE1-SOC開發板的oneAPI實驗教程(2)

基于DE1-SOC開發板的oneAPI實驗教程(2)

評論