乘法器是眾多數字系統中的基本模塊。從原理上說它屬于組合邏輯范疇:但從工程實際設計上來說,它往往會利用時序邏輯設計的方法來實現,屬于時序邏輯的范疇。

通過這個實驗使大家能夠掌握利用FPGA/CPLD設計乘法器的思想,并且能夠將我們設計的乘法器應用到實際工程中。乘法器的設計方法有兩種:組合邏輯設計方法和時序邏輯設計方法。采用經合邏輯設計方法,電路事先將所有的乘積項全部計算出來,最后加法運算。采用時序邏輯設計方法,電路將部分已經得到的乘積結果右移,然后與乘積項相加并保存和值,反復迭代上述步驟直到計算出最終乘積。

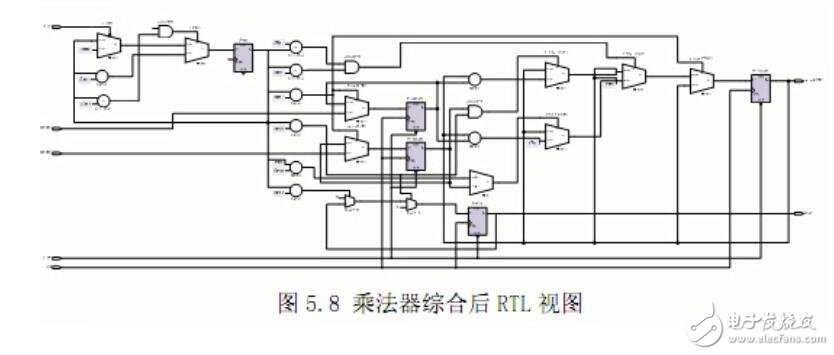

在該實驗中就是要利用時序邏輯設計方法來設計-一個16位乘法器,既然是利用時序邏輯設計方法那么就得利用時鐘信號控制乘法器運算。用時序邏輯設計方法與用組合邏輯設計方法比較,它有什么好處呢?利用時序邏輯設計方法可以使整體設計具備流水線結構的特征,能適用在各種實際工程設計中。

更多關于BJ-EPM240學習板之乘法器設計實驗請看視頻。

-

FPGA

+關注

關注

1643文章

21963瀏覽量

614078 -

乘法器

+關注

關注

9文章

211瀏覽量

37813

發布評論請先 登錄

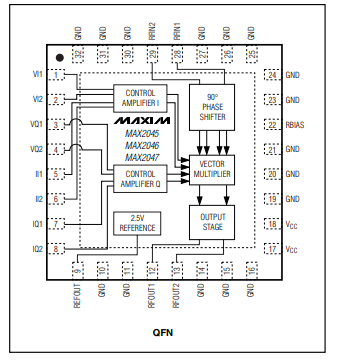

MAX2046高增益矢量乘法器技術手冊

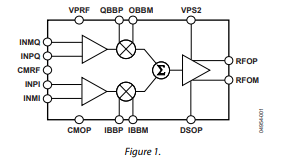

ADL5390 RF矢量乘法器技術手冊

ADA-28F00WG乘法器Marki

求助,LMX2572LP參考時鐘路徑中的乘法器MULT的輸入頻率范圍問題求解

請問如何用VCA810實現模擬乘法器?

CDC906可編程3-PLL時鐘合成器/乘法器/分頻器數據表

CDCF5801A具有延遲控制和相位對準的時鐘乘法器數據表

CDCS503帶可選SSC的時鐘緩沖器/時鐘乘法器數據表

BJ-EPM240學習板之乘法器設計實驗

BJ-EPM240學習板之乘法器設計實驗

評論