1、在總線連接的結構上。總線上掛有多個設備,設備于總線以高阻的形式連接。這樣在設備不占用總線時自動釋放總線(放棄對總線的使用),以方便其他設備獲得總線的使用權。

2、大部分單片機I/O使用時都可以設置為高阻輸入,如陵陽,AVR等等。高阻輸入(類似于CMOS輸入阻抗)可以認為輸入電阻是無窮大的,認為I/O對前級影響極小,而且不產生電流(不衰減),而且在一定程度上也增加了芯片的抗電壓沖擊能力。

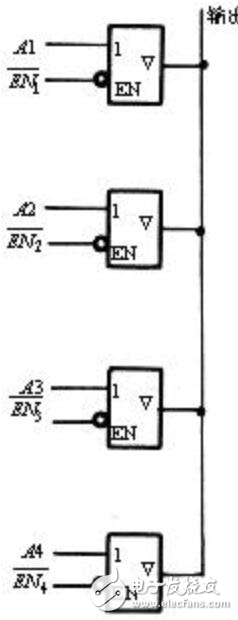

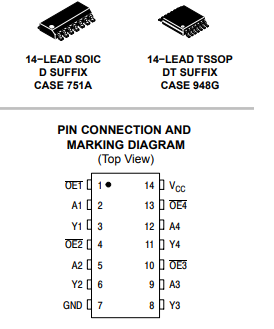

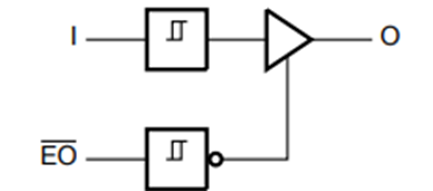

將74LS125的四個三態門的輸出端接在一起,形成總線形式。如圖所示。再將四個三態門電路的輸入端分別接上不同的信號,然后將四個三態門的控制端分別依次接上低電平的控制信號,用示波器觀察輸出端的輸出波形,并繪出相應波形。(注意:當一個控制端接上低電平時,其他的控制端必需接到高電平。)

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

總線

+關注

關注

10文章

2959瀏覽量

89729 -

三態門

+關注

關注

1文章

34瀏覽量

19013

發布評論請先 登錄

相關推薦

熱點推薦

AiP74LVC125帶三態控制的4路緩沖器/線驅動器產品說明書

電子發燒友網站提供《AiP74LVC125帶三態控制的4路緩沖器/線驅動器產品說明書.pdf》資料免費下載

發表于 05-06 15:28

?0次下載

SN74AVC2T244的使能引腳OE到底是OE=低電平時輸出三態,還是OE=高電平時輸出三態?

SN74AVC2T244的使能引腳OE到底是OE=低電平時輸出三態,還是OE=高電平時輸出三態?

TI的手冊也能漏洞百出?

發表于 12-04 07:48

【「數字IC設計入門」閱讀體驗】+目錄和前2章

4.2.7移位操作符36

4.2.8條件操作符37

4.2.9連接和復制操作37

4.3表達式種類38

第5章門電平模型化39

5.1內置基本門39

5.2多輸入門39

5.3多輸出門41

5.4三態

發表于 10-10 17:12

CDC2536具有三態輸出的3.3鎖相LO0P時鐘驅動器數據表

電子發燒友網站提供《CDC2536具有三態輸出的3.3鎖相LO0P時鐘驅動器數據表.pdf》資料免費下載

發表于 08-21 10:32

?0次下載

三態緩沖器在總線控制中的應用

三態緩沖器在總線控制中的應用是計算機系統設計中的一個關鍵環節,其獨特的三態輸出特性使得它在實現多設備間數據共享和傳輸時顯得尤為重要。以下將詳細探討三態緩沖器在總線控制中的應用,包括其基本原理、功能優勢、具體實現方式以及在實際系統

三態緩沖器在計算機中的應用

三態緩沖器(Tri-state Buffer)在計算機系統中扮演著至關重要的角色,其應用廣泛且深入。三態緩沖器不僅具備基本的信號放大、去噪和波形整形功能,還能通過特定控制信號實現開關效果,使得單個

三態緩沖器的工作原理和應用

三態緩沖器(Three-state buffer),又稱為三態門、三態驅動器,是一種特殊的邏輯門電路,其工作原理主要基于三態輸出控制。

三態輸出門可以實現線與功能嗎

三態輸出門(Tri-State Output Gate)是一種特殊類型的邏輯門,它具有三個狀態:高電平、低電平和高阻抗狀態(也稱為高阻抗或浮空狀態)。這種門在數字電路設計中非常有用,因

三態門電路的輸出有哪三種狀態

三態門電路是一種特殊的數字邏輯電路,其輸出可以有三種狀態:高電平、低電平和高阻抗狀態。這種電路在數字系統中有著廣泛的應用,如數據總線、地址總線等。 一、三態門電路的工作原理 三態門電路

三態門的應用

三態門的應用

評論