隨著時(shí)代的發(fā)展,越來越多的技術(shù)伴著EDA工具的不斷完善以及工作的細(xì)分,從前覺得很專業(yè)的事情,現(xiàn)在變得門檻越來越低,閑下來的時(shí)候想想如果我依然只會(huì)畫畫原理圖,畫畫PCB,那么遲早會(huì)被更加有精力、更加專業(yè)的人替代就覺得心慌。比如五年前,我當(dāng)時(shí)能夠完成一拖8的DDR3設(shè)計(jì),在當(dāng)時(shí)可以靠這個(gè)混口飯吃。然而現(xiàn)在你在去看,滿大街的layout工程師,他們比我有精力、比我更渴望學(xué)習(xí)、比我更加容易接受新的EDA工具和新的設(shè)計(jì)理念。因此我必需給自己找條更好的路,讓自己的技術(shù)更加豐富起來,更加有能力去解決一些在當(dāng)下很多人無法解決的問題。 我覺得在未來,底層的layout也好,數(shù)字電路設(shè)計(jì)也好,基本一個(gè)普通的大專生培訓(xùn)3個(gè)月就可以非常輕松的上手,毫不夸張的說,只要你懂歐姆定律,就可以實(shí)現(xiàn)一個(gè)平板電腦的設(shè)計(jì),因?yàn)楝F(xiàn)在的很多功能都已經(jīng)sip到了芯片內(nèi)部去了,哪怕是模擬的RF部分,現(xiàn)在也將LNA、SWITCH等等射頻電路集成了,前端只有做個(gè)天線的阻抗匹配即可,所以你可以看到,其實(shí)技術(shù)依然在,只是越來越多的活被做芯片人干掉了,所以我以時(shí)俱進(jìn),去干一干系統(tǒng)集成的一個(gè)部分:如何通過芯片級(jí)的設(shè)計(jì)去解決一些板級(jí)發(fā)生的問題。

在研究挖礦機(jī)的時(shí)候,我發(fā)現(xiàn)了一個(gè)比較嚴(yán)峻的問題:

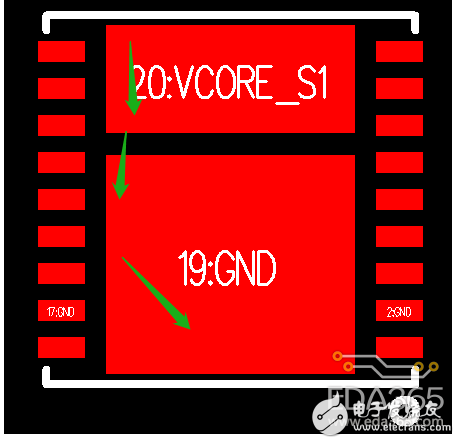

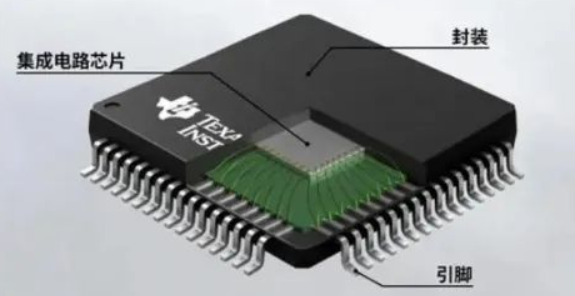

由于芯片的電流非常的大,傳統(tǒng)的芯片VCC和VSS的焊盤設(shè)計(jì)見下圖:

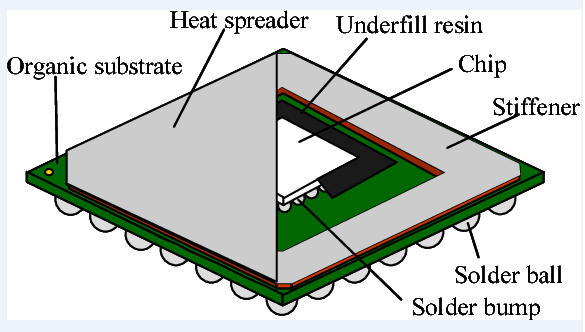

上圖設(shè)計(jì),工程師一般要把DIE放置在VSS焊盤上,因此我們會(huì)看到,電流的流通路徑必然會(huì)是從VCC焊盤取電,然后通過基板在通過DIE的BALL傳遞到內(nèi)核,在經(jīng)過die的BALL傳導(dǎo)到基板在下到PAD在回到電源負(fù)極,見圖,

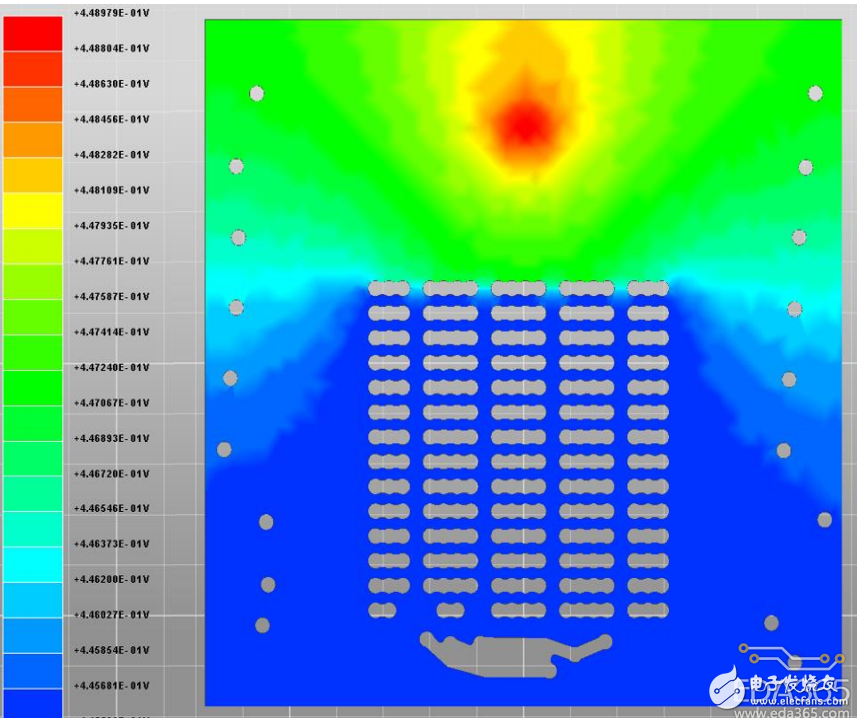

如果電流很小,那么我么可以不用考慮這個(gè)路徑上的阻抗導(dǎo)致的drop。然而BTC的芯片過電流往往會(huì)是30A以上,因此我以30A模擬仿真了下數(shù)據(jù),可以發(fā)現(xiàn)一些端倪:

上圖可以看到,紅色部分為VCC焊盤下方,設(shè)置的輸入源,我們看IR-DROP可以看到,在DIE的下端明顯壓降遠(yuǎn)遠(yuǎn)大于上端。這就會(huì)造成一個(gè)問題:DIE下端的單元獲取到電壓會(huì)低于上端電壓,進(jìn)而如果按理論VCC=0.5V供電會(huì)導(dǎo)致下端的計(jì)算單元的正確率低于上端,如何解決該問題呢?一個(gè)簡(jiǎn)單的辦法就是加壓:把電壓抬高到下端能夠達(dá)到0.5V,但是這樣造成一個(gè)新問題:上端的單元供電電壓偏高進(jìn)而造成功耗增大。。 ^. E’ W“ |; Z$ u

以上問題,如果是一個(gè)原理工程師或者PCB工程師或者單純的substrate工程師都可能無法真正的認(rèn)識(shí)到并做出改進(jìn),因?yàn)閷?shí)際上對(duì)于封裝工程師而言,也許他不會(huì)意識(shí)到系統(tǒng)設(shè)計(jì)上的大電流給后端造成的困擾,而原理圖工程師由于不清楚封裝設(shè)計(jì)原理從而無從下手,很好,我發(fā)現(xiàn)我可以做這件事,因?yàn)槲壹榷冒寮?jí)設(shè)計(jì)又懂芯片設(shè)計(jì),應(yīng)該有機(jī)會(huì)靠這個(gè)混碗飯吃。1 p& Q” \/ C3 E4 r

如何改進(jìn)改辦法呢?我們還是要分析一下,用的知識(shí)點(diǎn)不懂,就是歐姆定律:壓降大原因是阻抗大,為什么阻抗大?是因?yàn)檫^電流層只有基板上的銅,而這個(gè)銅一般只有30um,在30A的電流下,催生了如此大的壓降。因此改進(jìn)點(diǎn)就是:如何降低路徑上的阻抗。方法如下:- S4 M. P5 a2 ` {。 x8 d9 v/ j

1、基板加層。我去,太貴了。

2、基板銅厚增加,一樣,太貴了。

3、減短路徑。

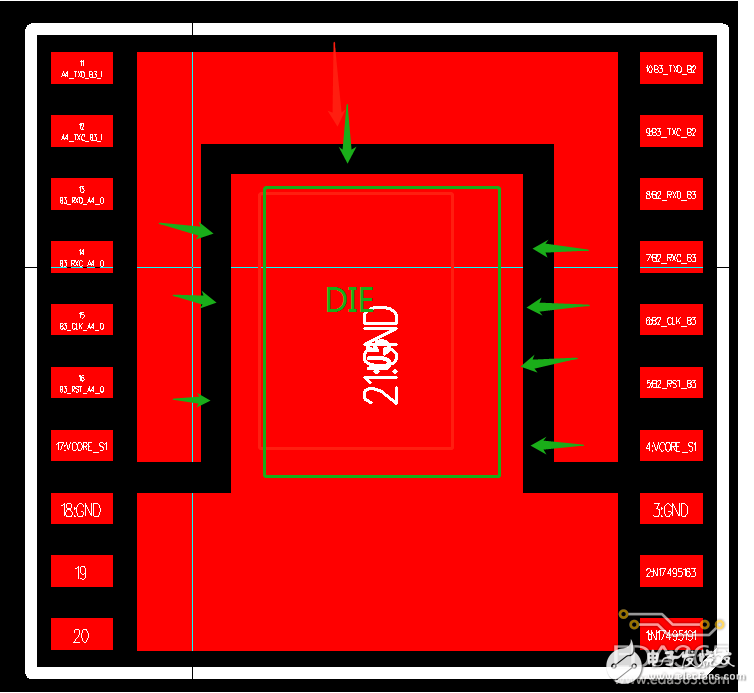

我考慮了下,第三個(gè)辦法應(yīng)該是可行的,如何減短路徑?我把焊盤重新調(diào)整了下:

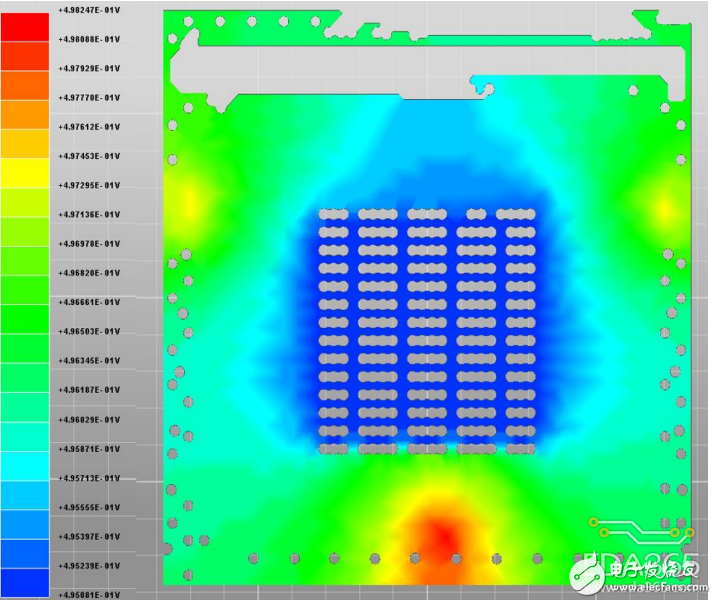

上圖的改進(jìn)點(diǎn)在于,我將電源的焊盤延伸下來了,由于PCB銅厚可以做的2OZ,因此可以大大減小路徑阻抗,同時(shí)由于四周都進(jìn)電源,也能側(cè)面減小路徑,看一下仿真圖:

結(jié)果果然:very good!

真想做一下這個(gè)測(cè)試,可惜做一個(gè)16nm的芯片從RTL設(shè)計(jì)到板級(jí) 沒有2000萬是下不來了,遺憾沒有辦法實(shí)際來驗(yàn)證一下這個(gè)結(jié)論。然而從這里有可以看到,越往芯片級(jí)的設(shè)計(jì),越需要設(shè)計(jì)者考慮的更加的充分,做好仿真,通過理論和仿真進(jìn)行對(duì)比,進(jìn)而做出最優(yōu)的設(shè)計(jì),因?yàn)槟阍僖膊桓艺f:錯(cuò)了沒事,咱在打一板不就得了。

-

pcb

+關(guān)注

關(guān)注

4352文章

23417瀏覽量

406719 -

eda

+關(guān)注

關(guān)注

71文章

2886瀏覽量

176450 -

挖礦機(jī)

+關(guān)注

關(guān)注

1文章

68瀏覽量

5158

發(fā)布評(píng)論請(qǐng)先 登錄

半導(dǎo)體后端工藝:封裝設(shè)計(jì)與分析

如何通俗理解芯片封裝設(shè)計(jì)

芯片封裝設(shè)計(jì)中的wire_bonding知識(shí)介紹

回收螞蟻礦機(jī),回收比特大陸礦機(jī),收購(gòu)比特幣礦機(jī)

回收比特幣礦機(jī),回收虛擬幣挖礦機(jī),收購(gòu)神馬礦機(jī)

礦機(jī)電源在比特幣礦機(jī)中的重要性

SMT電路板安裝設(shè)計(jì)方案

為什么需要封裝設(shè)計(jì)?

為什么需要封裝設(shè)計(jì)?

芯片封裝設(shè)計(jì)

全球范圍內(nèi)先進(jìn)封裝設(shè)備劃片機(jī)市場(chǎng)將迎來新的發(fā)展機(jī)遇

RedEDA使用教程(芯片封裝設(shè)計(jì)RedPKG)

為什么需要封裝設(shè)計(jì)?封裝設(shè)計(jì)做什么?

礦機(jī)中的芯片封裝設(shè)計(jì)方案

礦機(jī)中的芯片封裝設(shè)計(jì)方案

評(píng)論