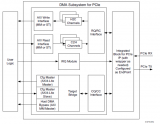

本視頻將介紹 Xilinx PCIe DMA 子系統(tǒng)的設(shè)置過程與性能測(cè)試,先展示可實(shí)現(xiàn)的硬件性能,然后說明用軟件進(jìn)行實(shí)際傳輸怎么會(huì)影響性能。最后將討論不同的選項(xiàng),以提高包括選擇最佳傳輸量與輪詢?cè)趦?nèi)的性能。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132357 -

硬件

+關(guān)注

關(guān)注

11文章

3484瀏覽量

67498 -

PCIe

+關(guān)注

關(guān)注

16文章

1342瀏覽量

85143

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

NVMe IP高速傳輸卻不依賴便利的XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

請(qǐng)求數(shù)據(jù)傳輸, 數(shù)據(jù)傳輸通過 AXI4總線接口對(duì)接用戶邏輯, 使用突發(fā)傳輸提高數(shù)據(jù)傳輸性能。

圖1 Nvme邏 輯加速IP系統(tǒng)架構(gòu)圖

新系統(tǒng)中,Nvme邏輯加速IP通過 PCIe 3.

發(fā)表于 06-29 17:42

基于AMD Versal器件實(shí)現(xiàn)PCIe5 DMA功能

Versal是AMD 7nm的SoC高端器件,不僅擁有比16nm性能更強(qiáng)的邏輯性能,并且其PS系統(tǒng)中的CPM PCIe也較上一代MPSoC PS硬核

基于PCIe(XDMA/QDMA)的多路視頻采集與顯示IP 多路高速AD采集與DA回放IP

隊(duì)列管理和PCIe C2H DMA引擎,將采集到的視頻幀實(shí)時(shí)傳遞到上位機(jī)采集緩沖區(qū)。在超帶寬視頻采集情況下,支持采集丟幀操作,后續(xù)視頻可以正常采集。視頻采集與顯示子系統(tǒng)使用高效的PCIe

發(fā)表于 04-14 15:17

在RC測(cè)試中執(zhí)行pcitest-S-r-s 1024后ep系統(tǒng)崩潰了怎么解決?

] pci_epf_test pci_epf_test.0:無法獲取 DMA 通道

在 RC 測(cè)試中執(zhí)行 pcitest-S-r-s 1024 后 ep 系統(tǒng)崩潰

發(fā)表于 03-25 07:04

PCIE XDMA開發(fā)環(huán)境搭建以及環(huán)路測(cè)試

大家 XILINX FPGA PCIE 應(yīng)用解決方案。 本教程以MZ7035FA作為樣機(jī)測(cè)試。在正式開始教程內(nèi)容前,有必要把MZ7035FA開發(fā)板的特點(diǎn)說明下。這是一款高性價(jià)比的FPGA開發(fā)板。帶

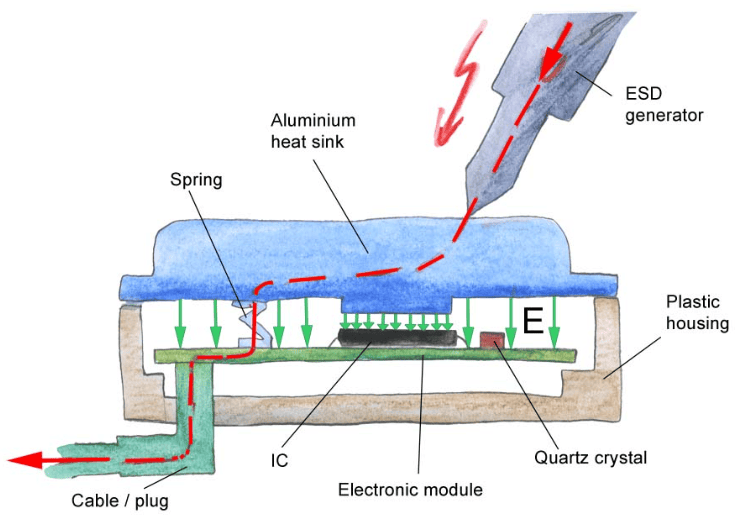

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(一) — 電子系統(tǒng)性能要求與ESD問題

此專題將從三個(gè)方面來分享: 一、電子系統(tǒng)性能要求與ESD問題 二、集成電路ESD問題應(yīng)對(duì)措施 三、集成電路ESD 測(cè)試與分析 工業(yè)、消費(fèi)及汽車電子模塊開發(fā)的 EMC 問題會(huì)導(dǎo)致極高的開發(fā)成本和時(shí)間

整車空調(diào)測(cè)試系統(tǒng)設(shè)計(jì)

隨著電子技術(shù)的發(fā)展以及汽車空調(diào)控制器性能的提高,汽車空調(diào)控制器的電子系統(tǒng)越來越復(fù)雜,系統(tǒng)使用的電子元器件的數(shù)量越來越龐大,系統(tǒng)要實(shí)現(xiàn)的功能也越來越多。為保證經(jīng)過多道工序裝配完工的電

PCIe延遲對(duì)系統(tǒng)性能的影響

隨著技術(shù)的發(fā)展,計(jì)算機(jī)系統(tǒng)對(duì)性能的要求越來越高。PCIe作為連接處理器、內(nèi)存、存儲(chǔ)和其他外圍設(shè)備的關(guān)鍵接口,其性能直接影響到整個(gè)系統(tǒng)的表現(xiàn)。

pcie帶寬對(duì)計(jì)算性能的影響

在現(xiàn)代計(jì)算機(jī)系統(tǒng)中,PCI Express(PCIe)接口已經(jīng)成為連接各種高速設(shè)備的標(biāo)準(zhǔn)。從顯卡到固態(tài)硬盤,再到網(wǎng)絡(luò)接口卡,PCIe提供了一種高速的數(shù)據(jù)傳輸方式。然而,PCIe的帶寬并

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+02.PCIE接口測(cè)試(zmj)

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+02.PCIE接口測(cè)試(zmj)

1.FPGA程序設(shè)計(jì)

PCI Express (peripheral component

發(fā)表于 11-12 16:05

DMA是什么?詳細(xì)介紹

DMA(Direct Memory Access)是一種允許某些硬件子系統(tǒng)直接訪問系統(tǒng)內(nèi)存的技術(shù),而無需中央處理單元(CPU)的介入。這種技術(shù)可以顯著提高數(shù)據(jù)傳輸速率,減輕CPU的負(fù)擔(dān),并提高整體

如何測(cè)試PCIe插槽的速度

插槽的速度取決于其版本和通道數(shù)。例如,PCIe 3.0 x16插槽的理論最大帶寬為32 Gbps,而PCIe 4.0 x16插槽的理論最大帶寬為64 Gbps。 2. 檢查硬件規(guī)格 在測(cè)試之前,需要

PCIe 4.0與PCIe 3.0的性能對(duì)比

隨著科技的快速發(fā)展,計(jì)算機(jī)硬件也在不斷地更新?lián)Q代。PCI Express(PCIe)作為一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),廣泛應(yīng)用于計(jì)算機(jī)硬件連接,如顯卡、固態(tài)硬盤等。 1. 帶寬對(duì)比 PCIe

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成塊,支持8.0Gb/s數(shù)據(jù)速率的PCI Express 3.0。本文介紹了7系列FPGA PCIe Gen3的應(yīng)用接口及一些特性。

PCIe 5.0 SerDes 測(cè)試

#01 PCIe Gen 5 簡(jiǎn)介 PCIe 是用于硬盤、固態(tài)硬盤 (SSD)、圖形卡、Wi-Fi 和內(nèi)部以太網(wǎng)連接的先進(jìn)互連 I/O 技術(shù)。PCIe 由一組快速、可擴(kuò)展且可靠的 I/O 標(biāo)準(zhǔn)組成

Xilinx PCIe DMA子系統(tǒng)的性能測(cè)試

Xilinx PCIe DMA子系統(tǒng)的性能測(cè)試

評(píng)論