本期文章《基于AMD Versal器件實現PCle5 DMA功能》,誠邀您率先了解如何利用Versal強大性能實現高速數據傳輸!

序言

Versal是AMD 7nm的SoC高端器件,不僅擁有比16nm性能更強的邏輯性能,并且其PS系統中的CPM PCIe也較上一代MPSoC PS硬核PCIe單元強大得多。本節將基于AMD官方開發板展示如何快速部署PCIe5x8及DMA功能。

1測試環境

Vivado版本:2023.2/2024.2,在windows10或者ubuntu22.04

實驗板卡:VPK120

上位機主板:EPYC9124超微主板

上位機系統:Ubuntu20.04/24.04

2Vivado工程生成

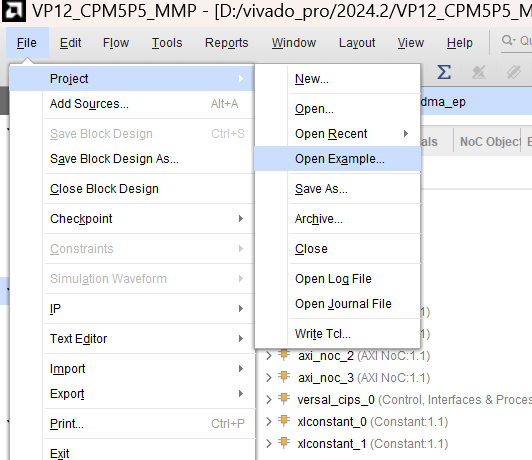

File->Project->Open Example

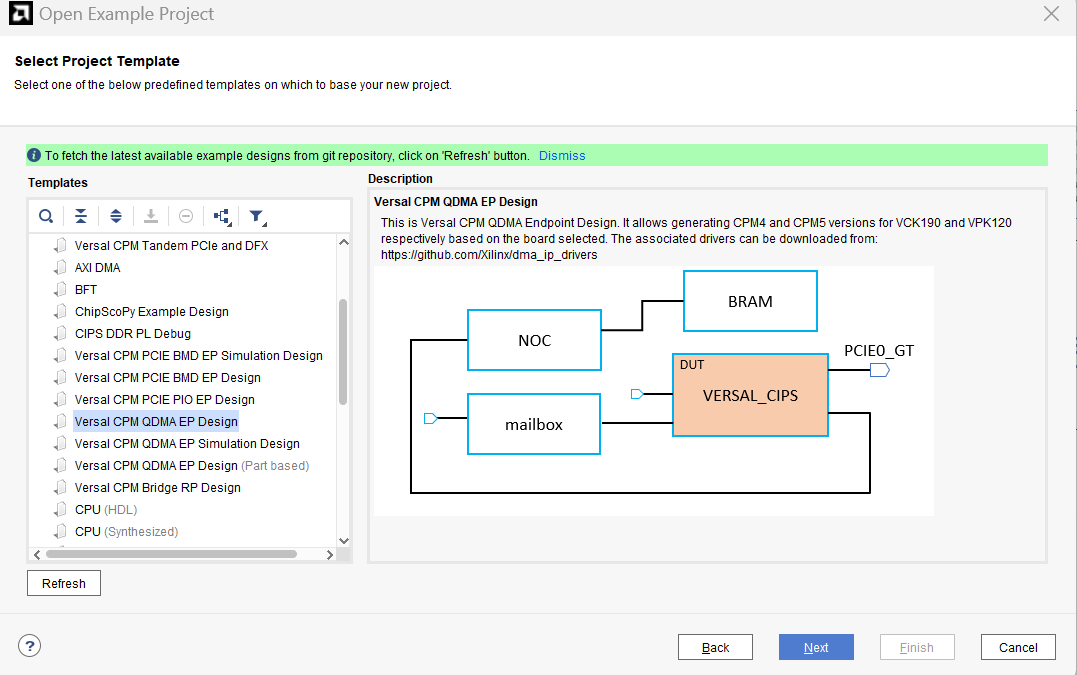

選擇Versal CPM QDMA EP Design

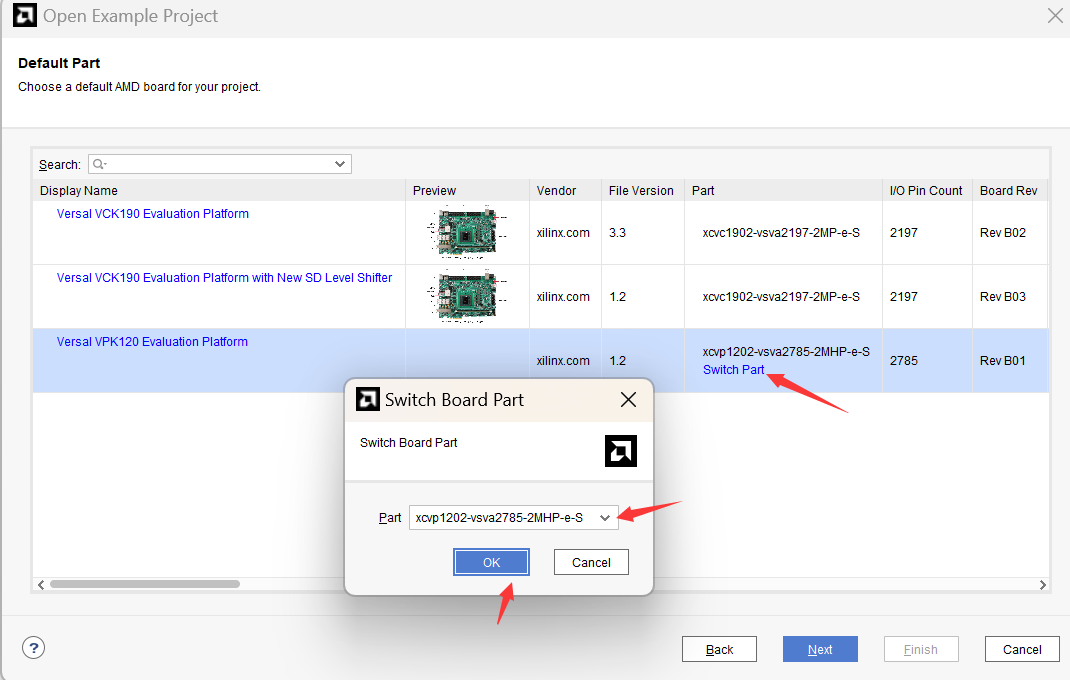

選擇名稱以后,選擇器件,注意選擇MHP

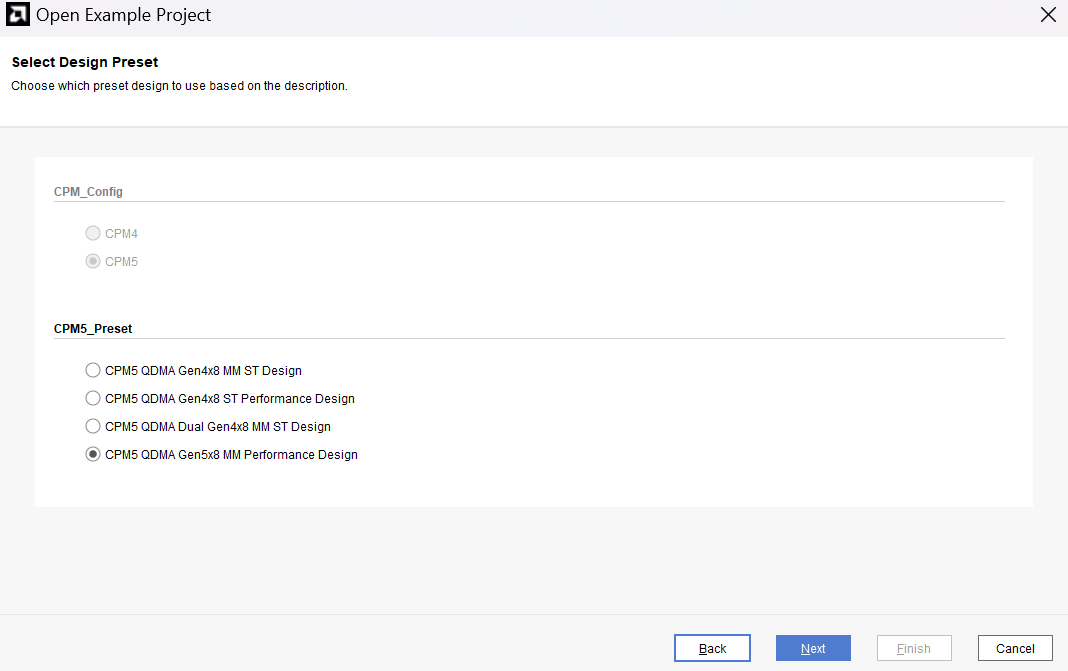

打開CPM5 QDMA Gen5x8 MM Performance Design,然后finish即可

3BD工程介紹與配置

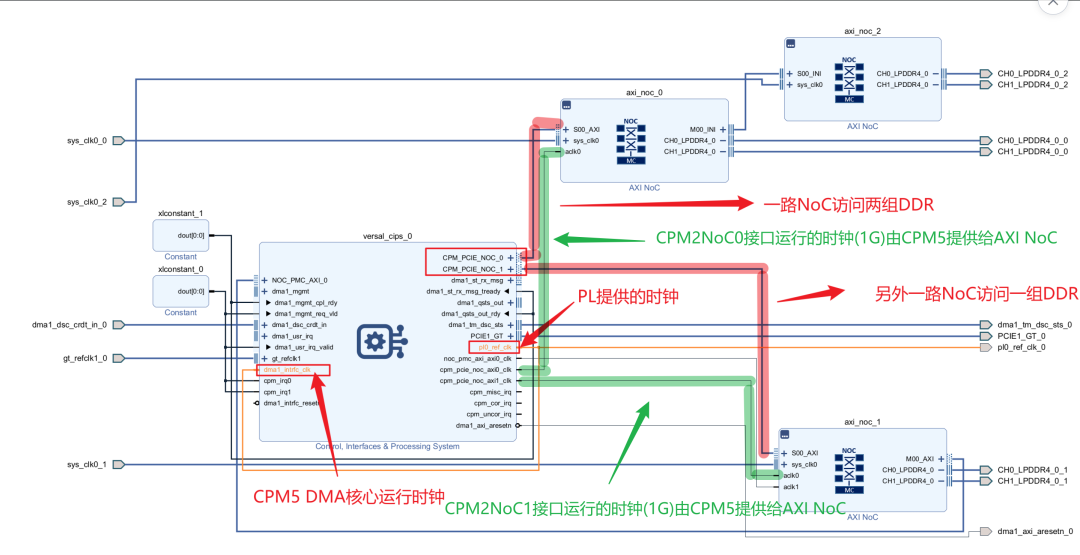

可以看到從CIPS IP中出現兩個CPM_PCIE_NOC口去訪問兩邊的DDR:

1)數據訪問架構:

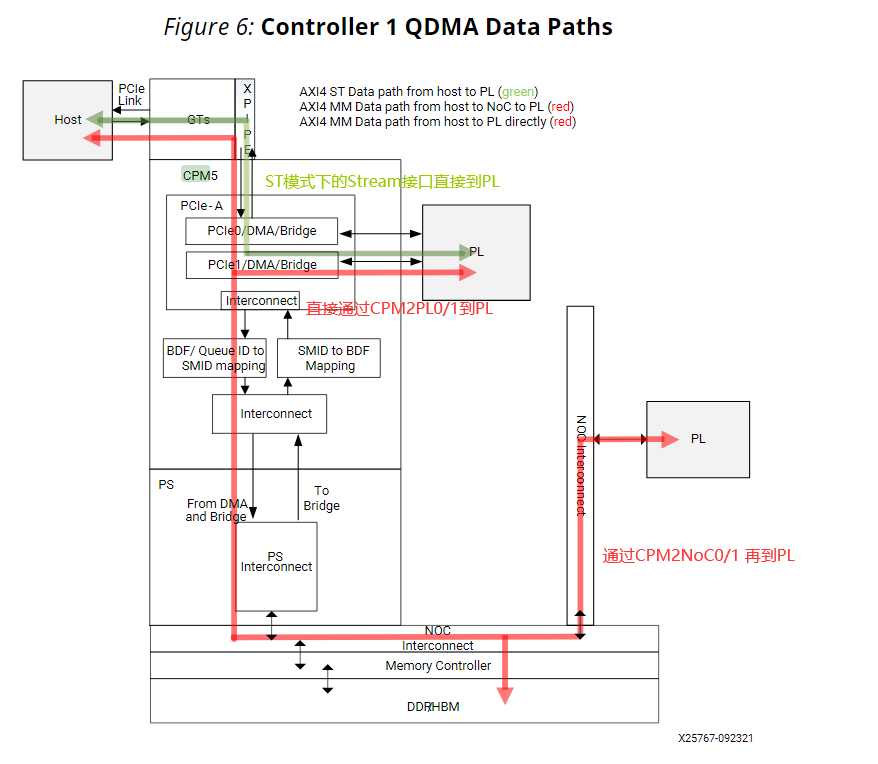

在VPK120上有兩個CPM控制器0與1,控制器1訪問數據的路徑有以下三種:ST_CPM2PL、MM_CPM2NoC、MM_CPM2PL,本次示例用兩個MM_CPM2NoC,通過NoC直接從DDR中搬運數據。

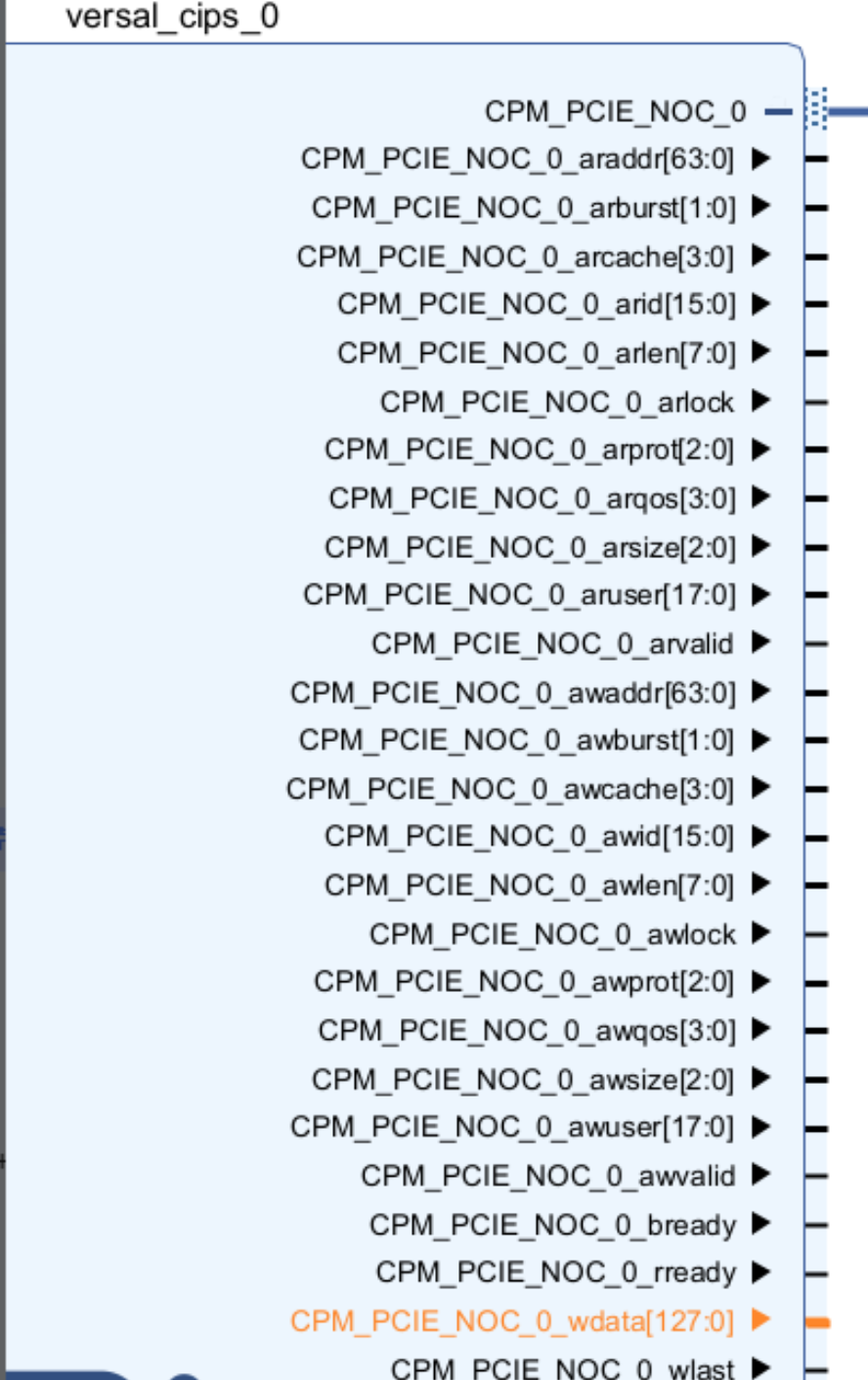

2)相關端口

為什么開兩個?

下圖是MM_CPM2NoC接口,看CPM2NoC接口的位寬與帶寬,由于走的是NoC,所以其單個接口的理論帶寬是128bit x 1000M(NoC運行頻率)=16GB,而PCIe5x8的理論帶寬是32GB/s,為此至少需要兩個MM端口,又由于擔心DDR訪問影響,所以demo中兩個端口同時去訪問兩組DDR,保證帶寬盡量不受DDR的影響。

為什么選用MM接口,而不是ST接口?

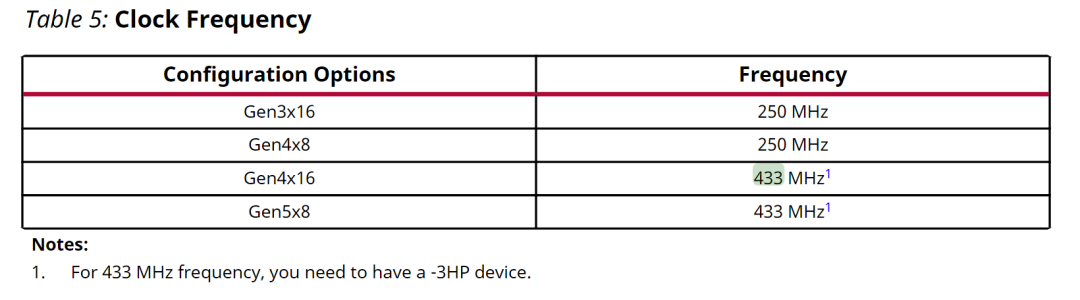

根據ds959手冊以及PG347手冊,ST模式下由于只會有一組ST_CPM2PL接口,而且位寬是512bit,所以理論上要到達PCIe5x8的帶寬,是需要時鐘跑到500M,但由于器件限制,其時鐘最高是433M,實際綜合下來時序收斂挑戰很大。

3)細節配置

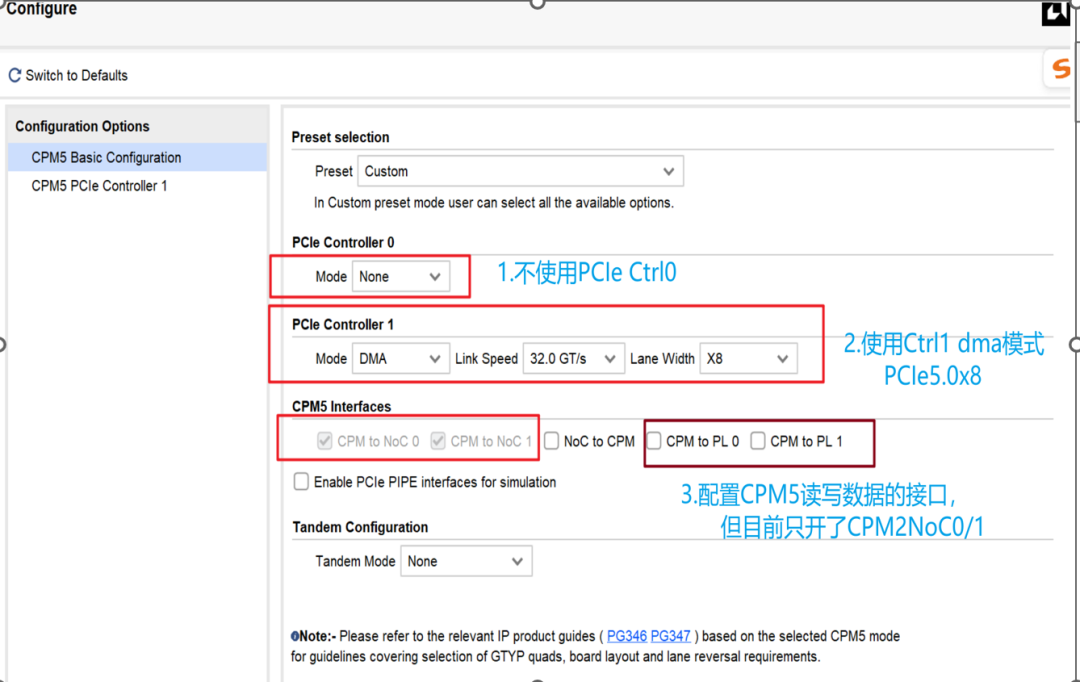

注意:CPM控制器0的數據路徑不如控制器1多,少了MM_CPM2PL,為此這里選擇控制器1。

如果要實現兩路PCIe5x8,則需要將棕色框兩個接口勾選上。

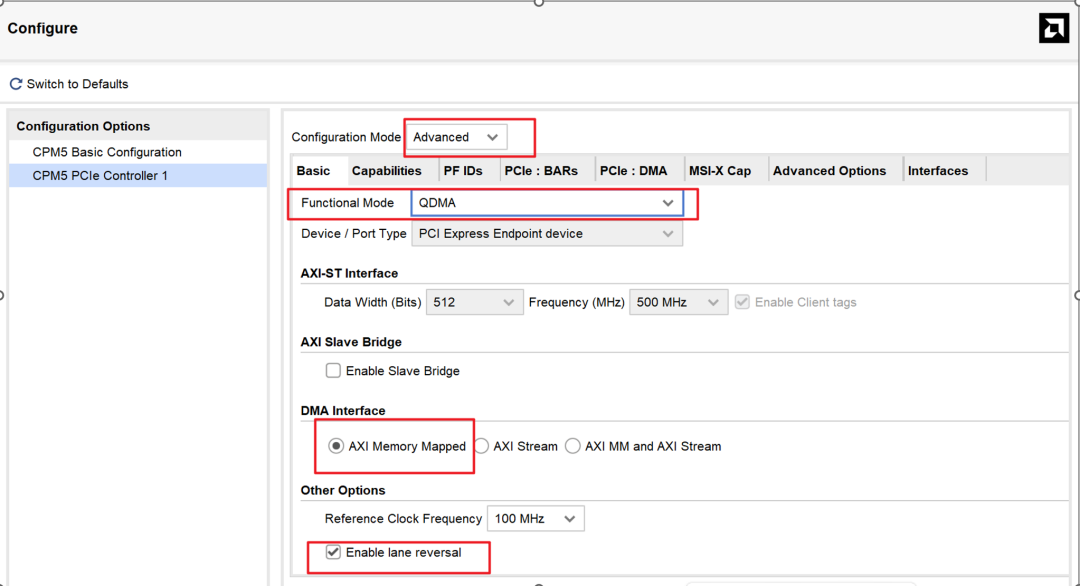

選擇QDMA模式下的AXI MM,根據硬件結構選擇Lane翻轉。

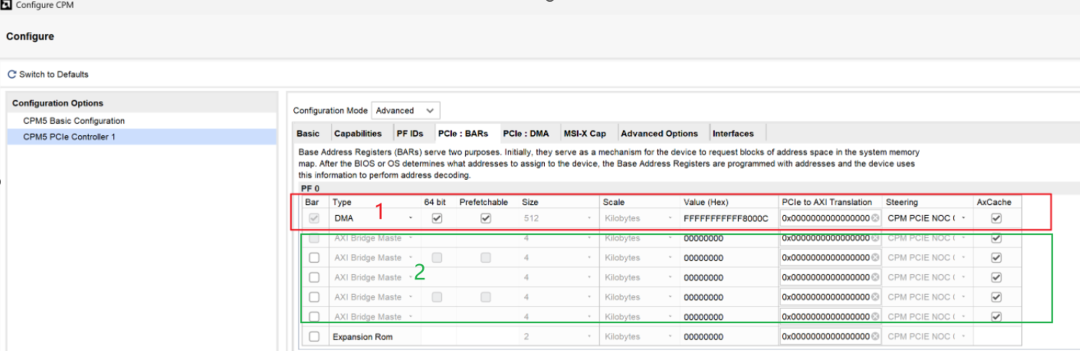

選擇bar空間

1:是主要的數據路徑接口;

2:類似于之前XDMA掛載寄存器的方式。

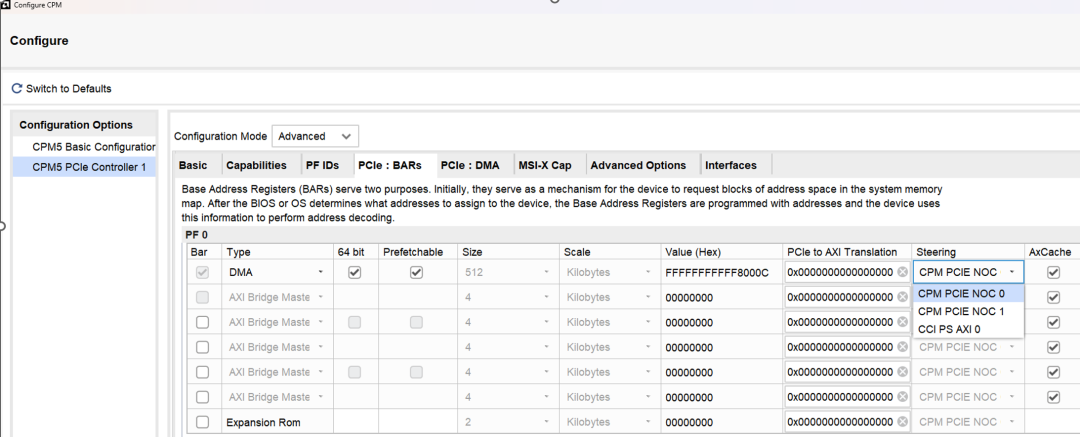

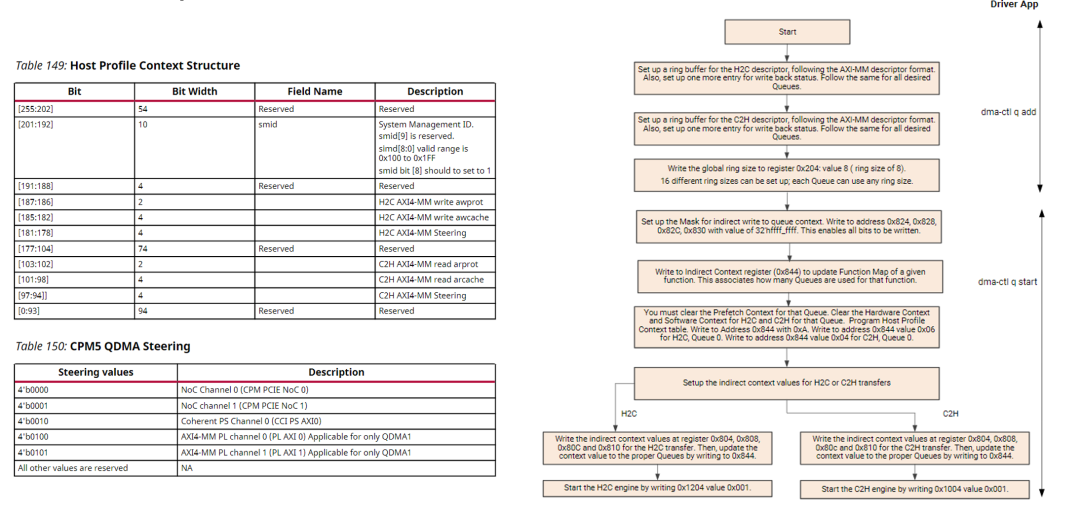

轉向器選擇:這里默認只選擇CPM2NoC0,這個后續通過Host profile來指定使用兩個CPM2NoC接口

4實際運行配置

在配置完后,直接編譯后,進入實操環節

安裝驅動

參考《pg347》的Using the Provided Software and Drivers章節

#下載驅動源碼,注意最好跟vivado版本對應上,master是最新的,對應vivado2024.1/2

git clone https://github.com/Xilinx/dma_ip_drivers.git

#如果之前已經加載過驅動,則先刪除驅動

rmmod qdma_pf

rm -rf dma_ip_drivers

#清理+編譯

make clean & make

make install

modprobe qdma-pf #安裝驅動

lspci -vvv -d 10ee: #查看設備節點是否存在

配置host profile

參考《pg347》的Host profile章節以及下面的鏈接

https://adaptivesupport.amd.com/s/article/000035811?language=en_US

是通過相關設備節點配置寄存器

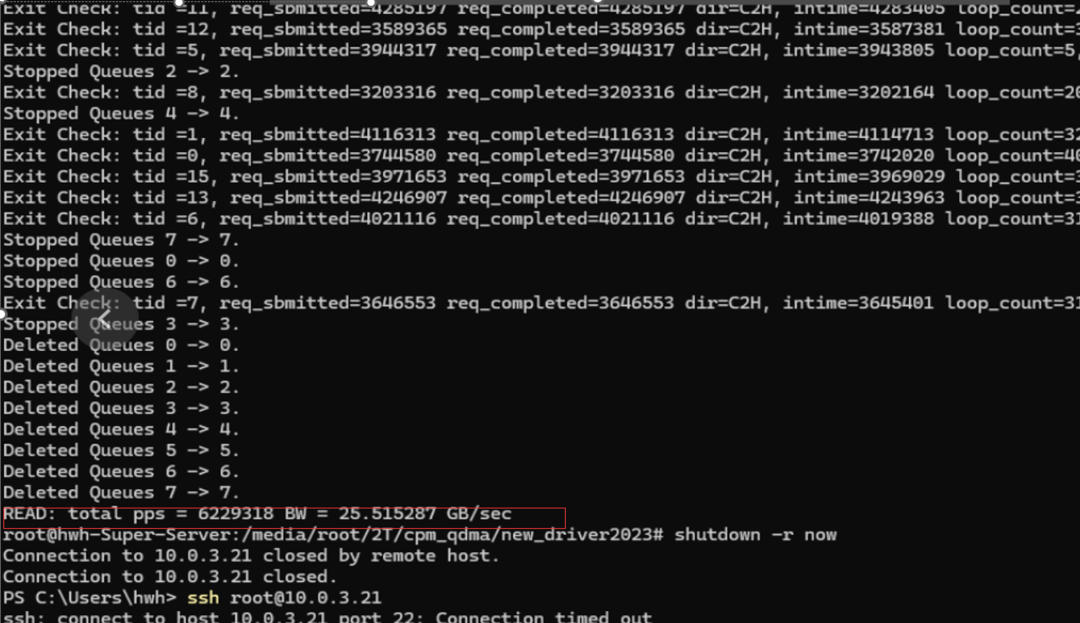

執行CFG啟動測試

CFG相關參考:

https://adaptivesupport.amd.com/s/article/Understanding-the-Versal-CPM5-QDMA-Gen4x8-ST-Only-Performance-Design-CED-Example-in-Vivado-2023-2?language=en_US

可以看到能夠到25GB/s左右

5總結

AMD Versal器件CPM單元集成了硬核QDMA功能,只需使用少量邏輯便能實現PCIe Gen5高帶寬數據傳輸。同時官方也集成好了dma-perf等測試程序以及相關驅動,可以快速地進行驗證與產品化,但需要注意的是MM模式的優劣以及性能影響因素,比如DDR、NoC帶寬等,不是所有應用都適用,適當在ST與MM模式下做選擇,可以幫助實現更高的性能。如果想在一個VP1202上實現兩個PCIe5x8 MM,如果想在一個VP1202上實現兩個PCIe5x8 MM,您可發送郵件至此郵箱尋求技術支持:[email protected]。

關于安富利

安富利是全球領先的技術分銷商和解決方案提供商,在過去一個多世紀里一直秉持初心,致力于滿足客戶不斷變化的需求。通過遍布全球的專業化和區域化業務覆蓋,安富利可在產品生命周期的每個階段為客戶和供應商提供支持。安富利能夠幫助各種類型的公司適應不斷變化的市場環境,在產品開發過程中加快設計和供應速度。安富利在整個技術價值鏈中處于中心位置,這種獨特的地位和視角讓其成為了值得信賴的合作伙伴,能夠幫助客戶解決復雜的設計和供應鏈難題,從而更快地實現營收。

-

amd

+關注

關注

25文章

5573瀏覽量

136028 -

soc

+關注

關注

38文章

4357瀏覽量

221949 -

開發板

+關注

關注

25文章

5581瀏覽量

103024 -

Vivado

+關注

關注

19文章

833瀏覽量

68360

原文標題:基于AMD Versal器件實現PCIe5 DMA功能

文章出處:【微信號:AvnetAsia,微信公眾號:安富利】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之 Versal 介紹(2)

PCIe DMA設計實現

Versal CPM AXI Bridge模式的地址轉換

基于AMD FPGA的PCIE DMA邏輯實現

Xilinx高性能PCIe DMA控制器IP,8個DMA通道

AMD Versal? Adaptive SoC CPM PCIE PIO EP設計CED示例

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

AMD第二代Versal自適應SoC的主要特色

AMD推出第二代Versal Premium系列

第二代AMD Versal Premium系列產品亮點

AMD Versal自適應SoC器件Advanced Flow概覽(上)

AMD Versal自適應SoC器件Advanced Flow概覽(下)

基于AMD Versal器件實現PCIe5 DMA功能

基于AMD Versal器件實現PCIe5 DMA功能

評論