來源:學習那些事

異構集成

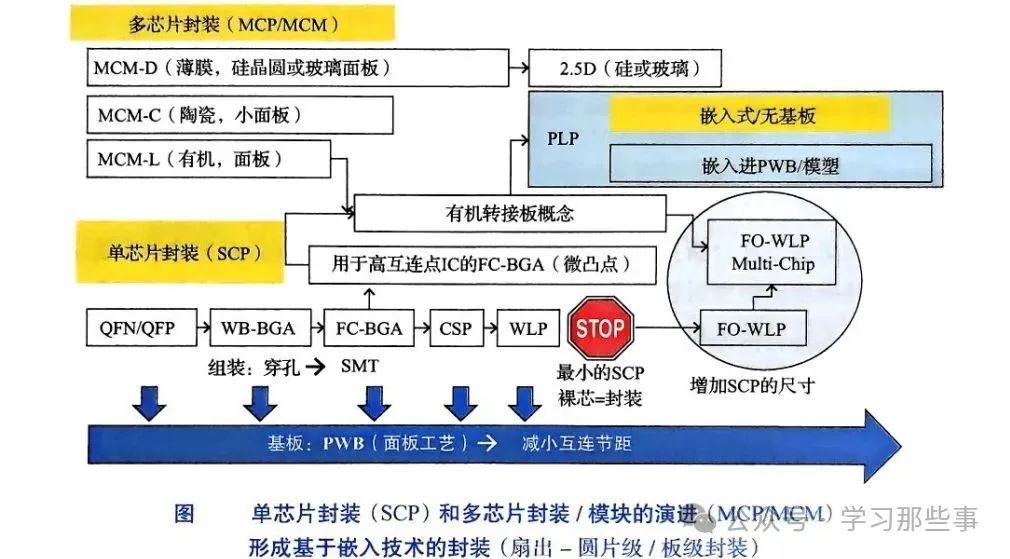

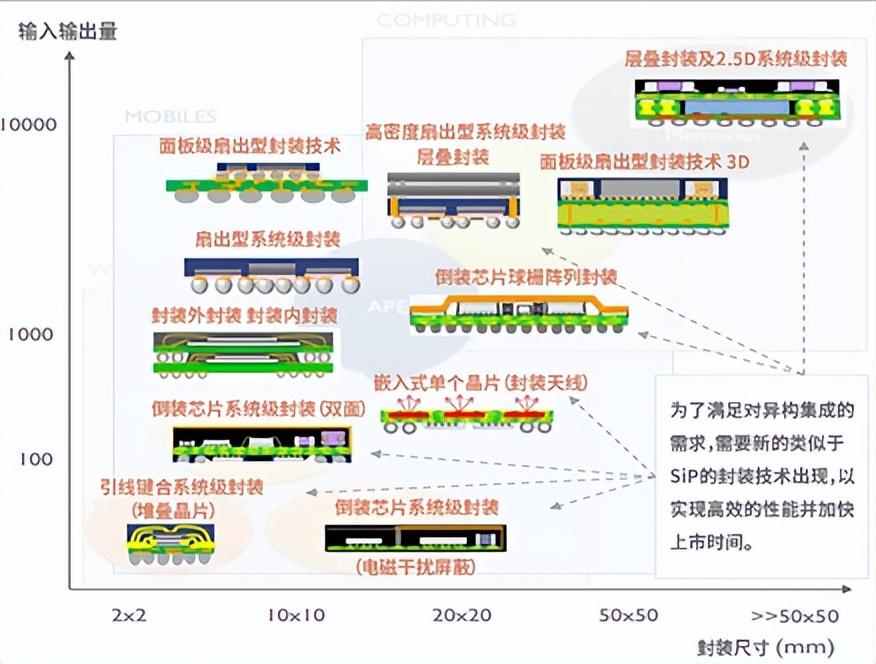

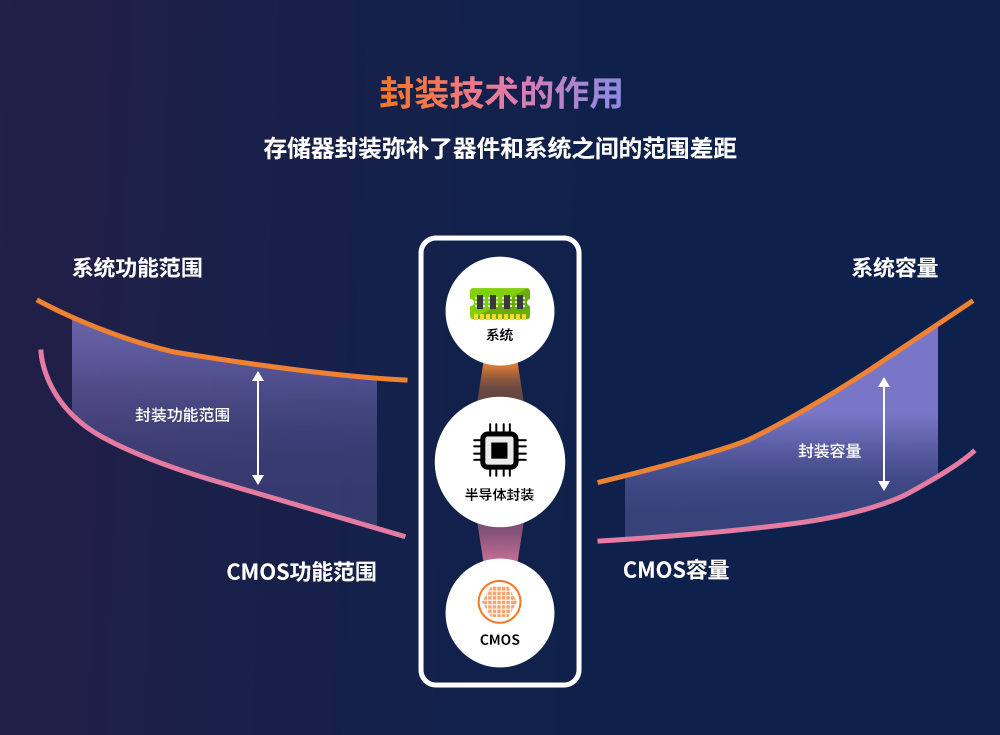

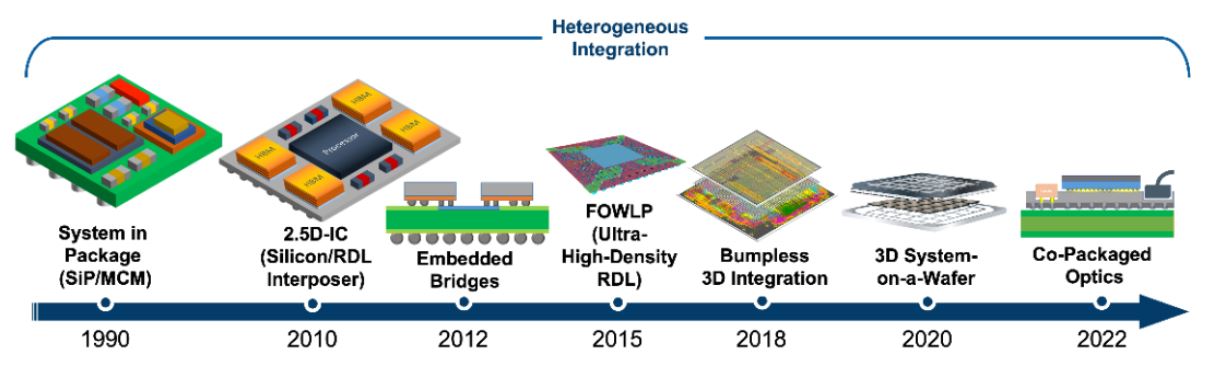

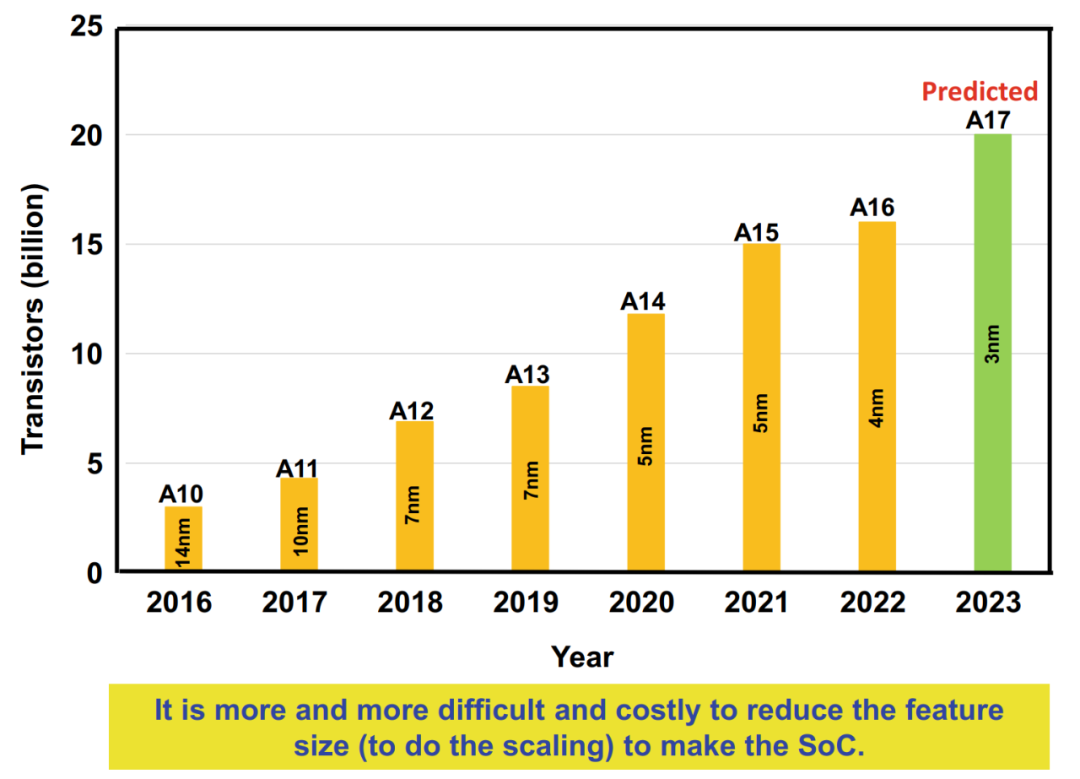

基于板級封裝的異構集成作為彌合微電子與應用差距的關鍵方法,結合“延續摩爾”與“超越摩爾”理念,通過SiP技術集成多材料(如Si、GaN、光子器件等)裸片及無源元件,借助扇出晶圓級/板級封裝等技術,實現更低成本、風險及更高靈活性,推動電子系統可靠性向十億分之幾故障率發展。

本文分述如下:

扇出板級封裝技術介紹

板級封裝的經濟效益分析

扇出板級封裝技術介紹

扇出板級封裝(FO-PLP)作為扇出晶圓級封裝(FO-WLP)的技術延伸,通過將有源和無源元件嵌入模塑料中,顯著提升了布線面積并推動了封裝的小型化潛力。其核心優勢在于無基板設計,采用薄膜金屬化替代傳統引線鍵合或倒裝芯片(FC)凸點,實現了更短的芯片間直接互連,從而降低了熱阻、提升了性能并減少了寄生效應,尤其在高頻應用中,相比FC-BGA封裝具有更低的電感。

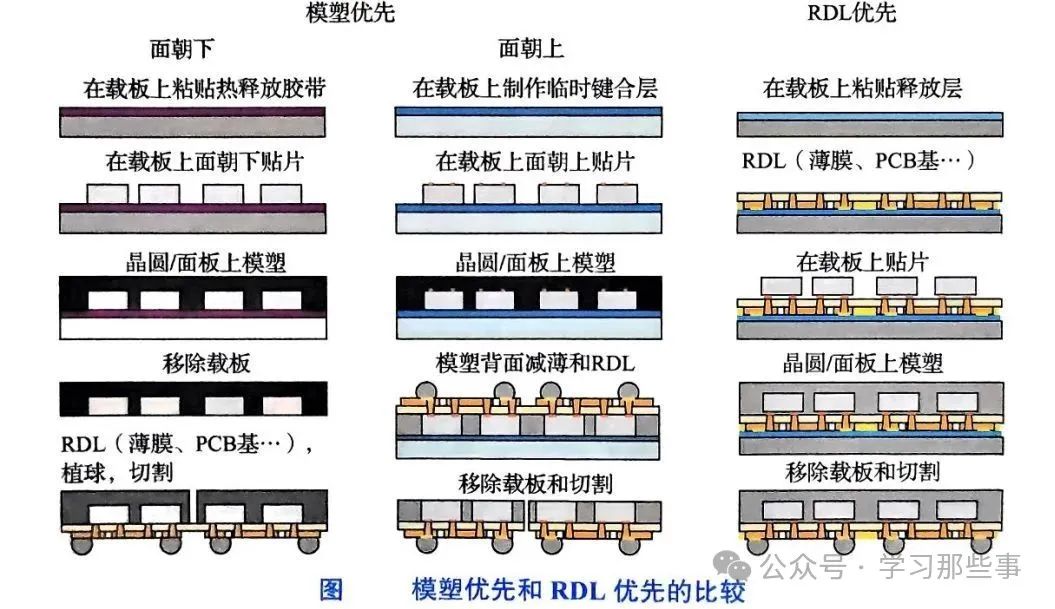

FO-PLP的工藝流程主要分為模塑優先和RDL(再布線層)優先兩類:模塑優先工藝中,面朝下路徑通過直接電鍍通孔具有最短的互連,在RF和毫米波領域表現最優,因互連路徑最短、高頻損耗最低;面朝上路徑則需銅柱互連,而RDL優先工藝需焊料互連,兩者均需額外聚合物/底部填充層。

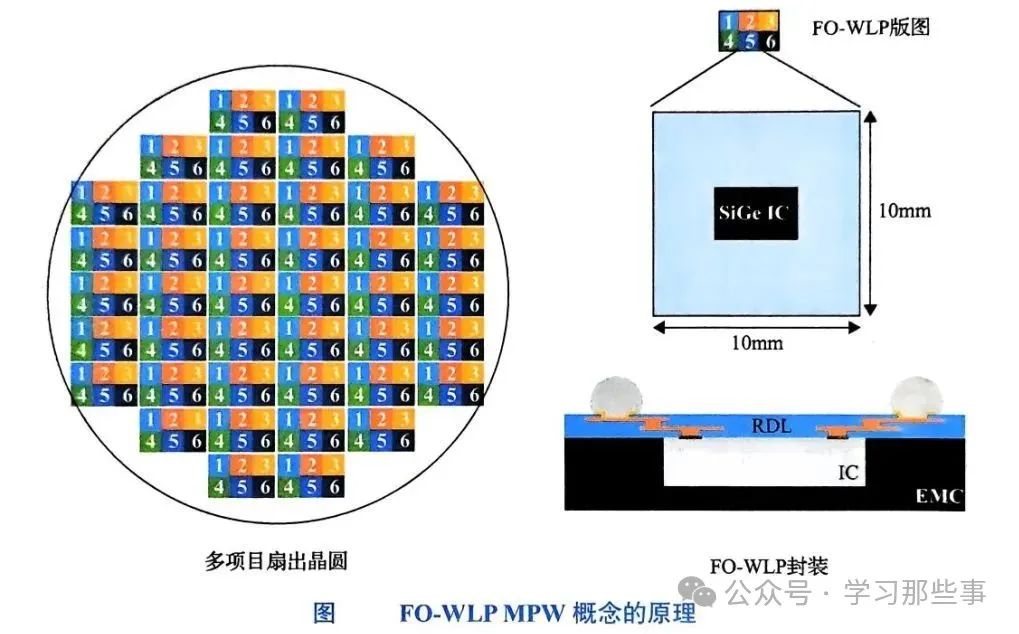

FO-PLP的異構集成能力尤為突出,可無縫集成不同材料(如Si、SiGe、GaN)、不同供應商甚至不同化合物技術的裸片,無需額外植球等準備步驟。

這一特性通過多項目晶圓(MPW)加工得到了驗證。

例如,采用250nm/130nm SiGe BiCMOS工藝制作的60GHz低噪聲放大器(LNA)、120GHz收發器、50GHz IF-IF轉換器等多種射頻IC,可集成于同一封裝中,采用低溫固化(<250℃)、低介電常數/損耗的介質層材料,配合三層介質、兩層金屬的RDL結構,最終電性能測試證實了其在異構射頻集成中的適用性。

材料與設備創新

低溫固化材料:采用介電常數低、損耗小的介質層,固化溫度低于250℃,適配環氧樹脂塑封料(EMC),玻璃化轉變溫度低于200℃。

玻璃基板:中科院等機構研發玻璃通孔(TGV)技術,提升熱穩定性與集成度,臺積電、三星等均布局玻璃基板封裝,以替代傳統硅中介層,降低翹曲率并提升良率。

最新產業動態與技術突破

臺積電:計劃2027年將FOPLP+TGV(玻璃通孔)技術導入量產,采用玻璃基面板級封裝以提升面積利用率并降低成本。2026年將設立扇出型面板級封裝實驗線,初期使用300×300mm面板,逐步過渡到更大尺寸。

三星:已將FOPLP技術用于移動或可穿戴設備(如Galaxy Watch),并開發出高達800×600mm的面板。其“3.3D”封裝技術結合RDL與3D堆疊,目標2026年量產,旨在連接邏輯芯片與高帶寬存儲器(HBM)。

日月光:FOPLP技術已量產,主要應用于射頻、電源管理等領域。2025年AI先進封裝需求強勁,將增加資本支出布局先進封裝及智能生產。

群創光電:利用舊3.5代廠轉型為全球最大尺寸FOPLP廠,2024年下半年試產,2025年逐步量產,月產能目標達3000~4500片,客戶涵蓋恩智浦、意法半導體等車用與電源管理領域廠商。

板級封裝的經濟效益分析

板級封裝的經濟效益分析需基于多層次、高顆粒度的自下而上成本模型,該模型通過詳細拆解工藝步驟(如組裝、模塑、RDL制備、UBM/球貼裝)及設備參數(投資、占地面積、處理時間、功耗),結合材料類型與用量、基建成本(電力、潔凈室、租金)等要素,實現對不同技術選擇(芯片先置/后置、光刻技術)、產品場景(裸片數量、封裝尺寸、RDL層數)及商業需求(生產地點、產量、交期)的差異化成本評估。

以面朝下模塑優先工藝為例,其成本構成涵蓋三層光敏介質RDL、鎳-金UBM及SnAgCu球的制備流程,核心挑戰集中于組裝精度與速度、模塑翹曲控制、RDL線寬/線距(L/S)優化等模塊,而測試環節未納入模型。

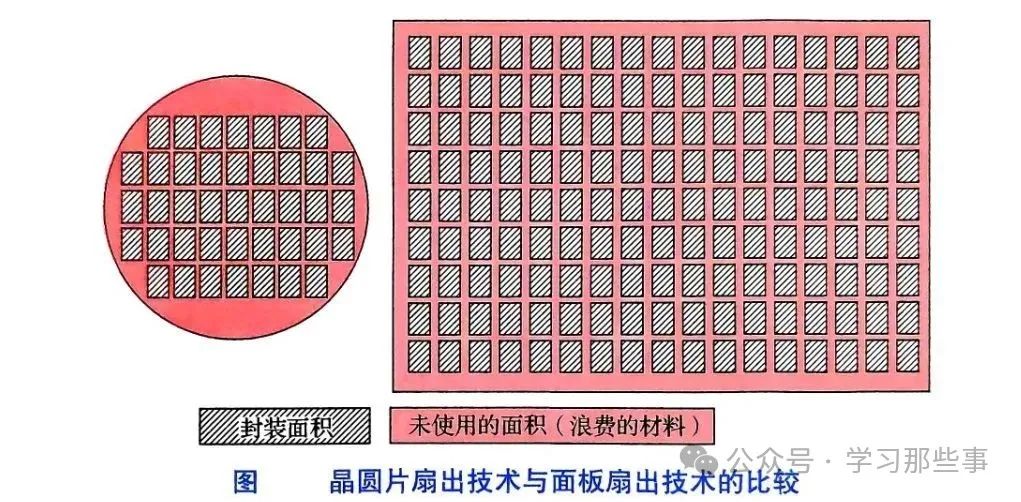

關鍵經濟優勢體現在材料利用率與面積效率的提升:

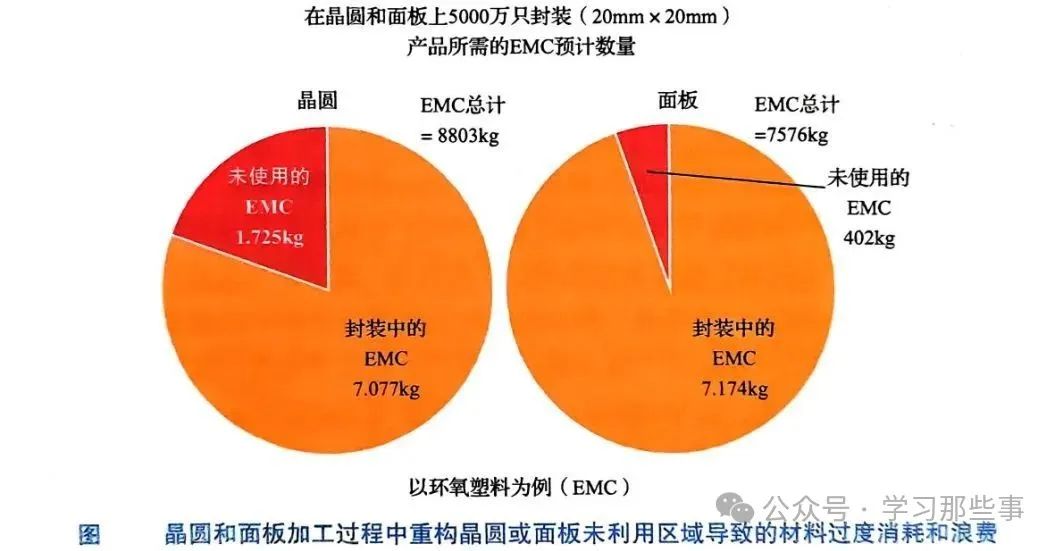

相較于300mm晶圓,457mm×610mm矩形面板在封裝尺寸較大時(如≥11mm×11mm)可實現更高的面積利用率(AU≥90%),而晶圓AU僅85%~88%且僅適用于小封裝。AU的提升直接減少基板非封裝區域的材料浪費——以生產5000萬只20mm×20mm封裝為例,面板方案較晶圓方案減少14%的環氧樹脂塑封料(EMC)消耗(402kg vs 1725kg),顯著降低材料成本(EMC為FO-PLP流程中最貴材料之一)。

此外,矩形面板的靈活性允許封裝水平或垂直放置,適配更多長寬比組合,進一步優化AU。

生產效率方面,面板方案通過提升組裝設備單位/小時(UPH)性能可降低組裝成本,且隨著面板尺寸增大(如610mm×457mm),單位基板面積的相對成本因組裝密度提升而下降,尤其對多芯片模塊(如三芯片)的成本改善更為顯著。對比300mm晶圓的單芯片封裝,大面板方案在保持芯片數量不變時,相對成本始終更低,且面板尺寸擴大進一步降低重構區域的成本分攤。

綜上,板級封裝通過高AU、低材料浪費、適配多芯片/大尺寸封裝的優勢,結合自下而上的精細成本模型驗證,展現出顯著的經濟效益,尤其在高端應用(如射頻、汽車電子、AI加速器)中,其成本效率與環境友好性成為推動異構集成技術落地的重要支撐。

-

晶圓

+關注

關注

53文章

5165瀏覽量

129792 -

封裝

+關注

關注

128文章

8684瀏覽量

145486 -

GaN

+關注

關注

19文章

2209瀏覽量

76798 -

異構集成

+關注

關注

0文章

39瀏覽量

2085

原文標題:板級封裝——異構集成

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

集成電路芯片封裝技術知識詳解

用于扇出型晶圓級封裝的銅電沉積

行業資訊 I 異構集成 (HI) 與系統級芯片 (SoC) 有何區別?

日月光應邀出席SEMICON China異構集成(先進封裝)國際會議

先進封裝技術-7扇出型板級封裝(FOPLP)

基于板級封裝的異構集成詳解

基于板級封裝的異構集成詳解

評論