異構(gòu)集成 (Heterogeneous integration,HI) 和系統(tǒng)級芯片 (System on Chip,SoC) 是設(shè)計和構(gòu)建硅芯片的兩種方式。異構(gòu)集成的目的是使用先進(jìn)封裝技術(shù),通過模塊化方法來應(yīng)對 SoC 設(shè)計日益增長的成本和復(fù)雜性。

在過去的 20 年里,Cadence 一直支持電子行業(yè)以SoC方式幫助我們的客戶追求更大的晶體管密度并不斷突破摩爾定律的界限,一直到 2nm 甚至 1nm 制程節(jié)點(diǎn)時,我們也在持續(xù)致力于幫助他們順利實(shí)現(xiàn)設(shè)計。現(xiàn)在,異構(gòu)集成提供了一種具有成本效益的替代方案,并用事實(shí)證明,對于許多應(yīng)用來說可能比單片SoC更為適合。

那么,我們來看看這兩種設(shè)計工藝之間的區(qū)別以及各自的優(yōu)勢和注意事項。

1

系統(tǒng)級芯片 (SoC)

SoC 是一種集成電路 (IC),將計算系統(tǒng)的每個部分都整合到一個硅晶粒中。其中包括一個或多個中央處理單元 (CPU) 或處理器(低功率微控制器和/或應(yīng)用處理器),每個都帶有幾個核心,以及圖形處理單元 (GPU)、Wi-Fi、藍(lán)牙或 4G/5G 蜂窩調(diào)制解調(diào)器、存儲器,甚至可能還包括存儲器等外圍設(shè)備。

在過去 20 年里,SoC 的興起和擴(kuò)展是半導(dǎo)體技術(shù)中最具創(chuàng)新性和令人興奮的變化之一。在過去,設(shè)計一個復(fù)雜的計算系統(tǒng)意味著使用離散的、現(xiàn)成的組件來設(shè)計一個系統(tǒng)。

由于 SoC 的所有部件都集成在一個晶粒上,SoC 在功率、性能和面積 (PPA) 方面提供了無與倫比的優(yōu)化。它們的運(yùn)行功率相對較小,能夠非常迅速地執(zhí)行計算功能,而且占用的物理空間也要小得多,這意味著最終設(shè)備的外形尺寸也可以更小。現(xiàn)在,全球數(shù)十億臺設(shè)備都依賴 SoC,從汽車到筆記本電腦,從智能手機(jī)到醫(yī)療器械。

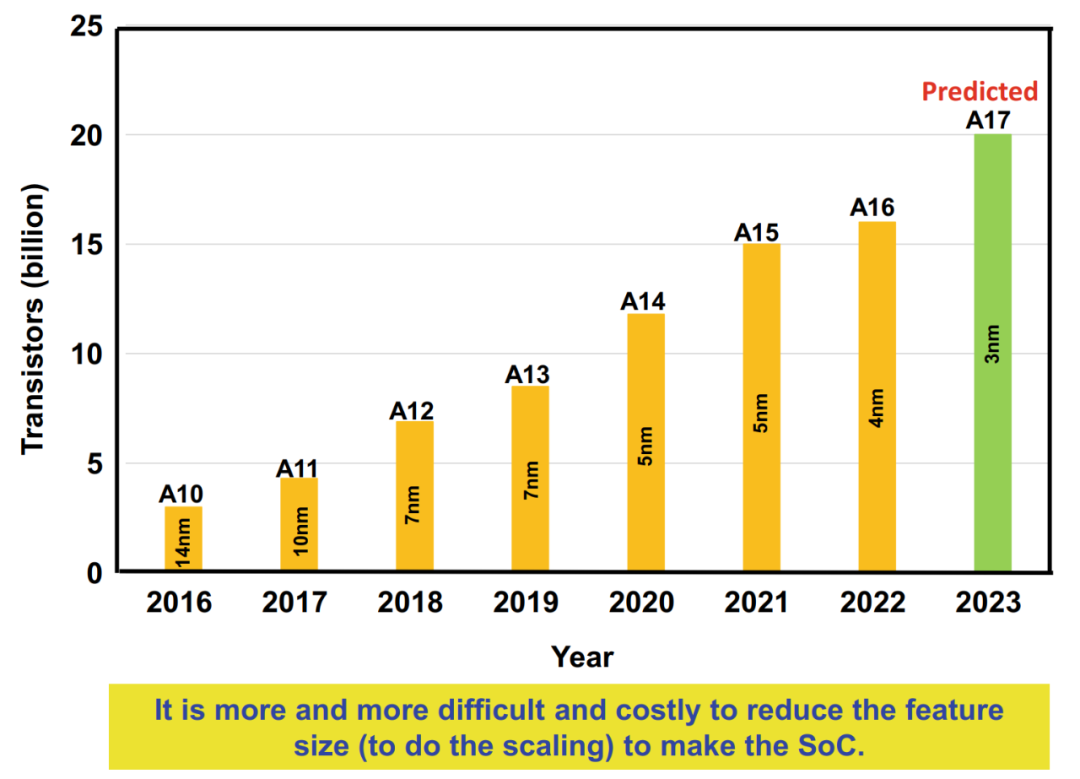

但是,制造先進(jìn)的單片 SoC,特別是如果采用最新的制程節(jié)點(diǎn)(7nm 及以下),成本變得越來越昂貴。自行業(yè)在 21 世紀(jì)前十年使用 FinFET技術(shù)以來,對于 28nm 以下的節(jié)點(diǎn),每個晶體管的成本節(jié)節(jié)升高--有能力投資最新設(shè)計節(jié)點(diǎn)的少數(shù)代工廠也開始紛紛宣布漲價。

此外還要考慮項目和初期投入工程成本 (NRE, non-recurring engineering) 。為了實(shí)現(xiàn)某個 3nm 設(shè)計,可能需要一個由數(shù)千名工程師組成的設(shè)計團(tuán)隊工作數(shù)萬小時,花費(fèi)數(shù)億美元,而這才僅僅完成了功能驗(yàn)證步驟。

如果要為面向大眾市場的智能手機(jī)打造一款 SoC,那么這筆投資也許可以收回成本。但對于小眾市場,例如國防/工業(yè)領(lǐng)域,市場需求只有 1000 件左右,再如此大費(fèi)周折就有點(diǎn)得不嘗失。

最后需要考慮物理限制。目前的 SoC 已經(jīng)達(dá)到了光刻的極限:如果不采用昂貴的縫合技術(shù),制造設(shè)備根本無法應(yīng)對不斷增長的芯片尺寸。隨著芯片尺寸增加,缺陷風(fēng)險也變得更高,導(dǎo)致晶圓的良率降低。

2

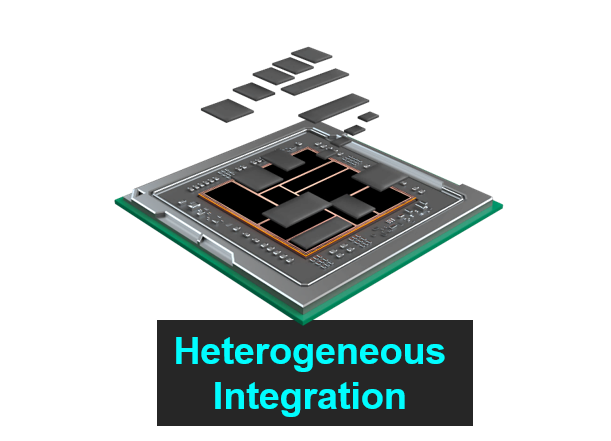

異構(gòu)集成(HI)

異構(gòu)集成為單片 SoC 提供了一種替代方案,對于復(fù)雜但成本預(yù)算有限的設(shè)計來說,異構(gòu)集成已經(jīng)成為一個非常有吸引力的選擇。

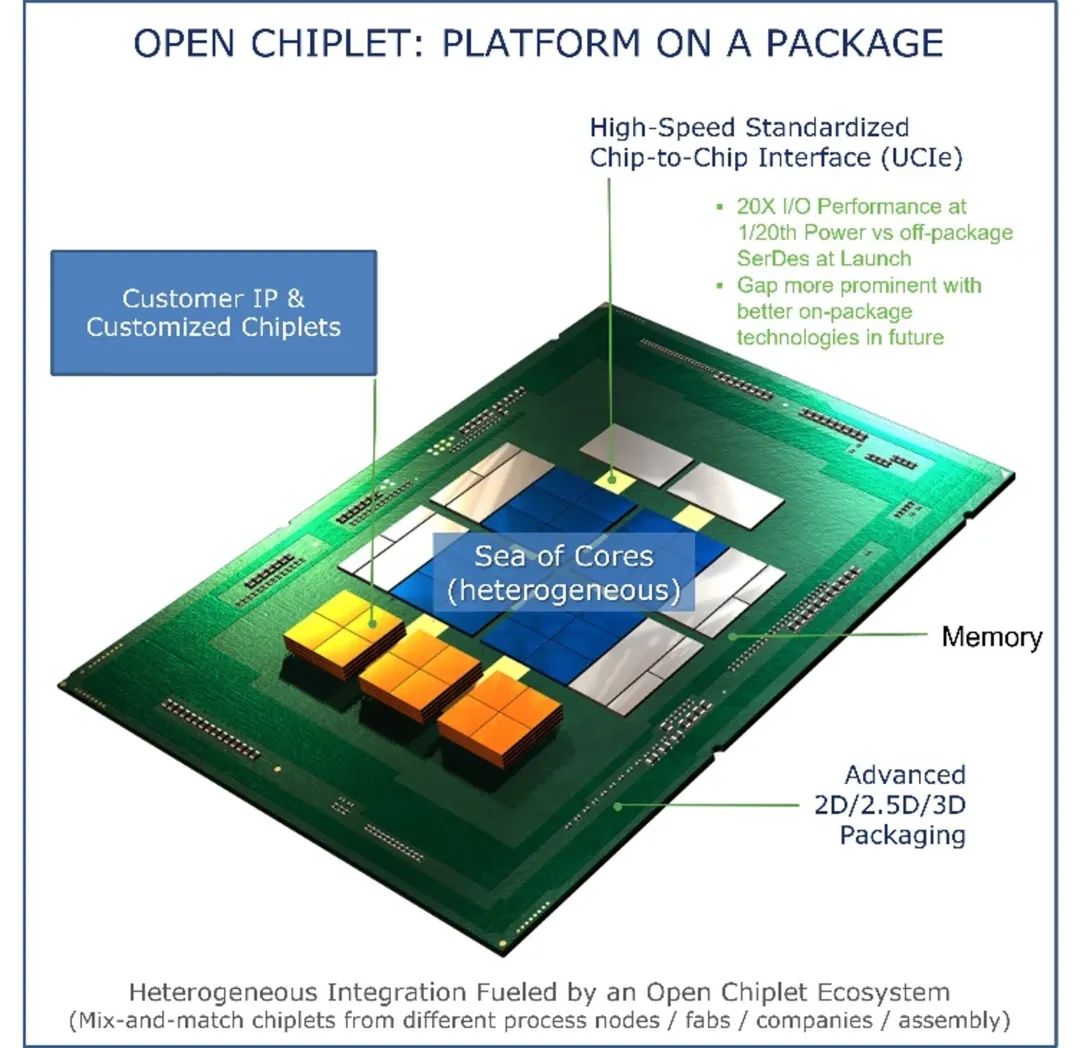

異構(gòu)集成是指使用先進(jìn)的封裝技術(shù),將較小的chiplet(芯粒/小晶片)整合到一個系統(tǒng)級封裝 (System in Package,SiP) 中;chiplet是物理上經(jīng)過實(shí)現(xiàn)和測試的 IP ,制成在芯片上并切割,可以執(zhí)行特定的邏輯功能。

可以把 SoC 看作單片機(jī),把異構(gòu)集成看作模塊化——整合來自不同芯片代工廠的不同 chiplets。每個 chiplet 都是單獨(dú)制造的,并且遠(yuǎn)遠(yuǎn)低于***可處理的極限尺寸,因此實(shí)際生產(chǎn)芯片的過程要簡單得多。Chiplets 也可以針對任何制程節(jié)點(diǎn)進(jìn)行組合設(shè)計;例如,異構(gòu)集成有可能將 28nm 的 chiplets 與 2nm 的 chiplets 整合在一起。

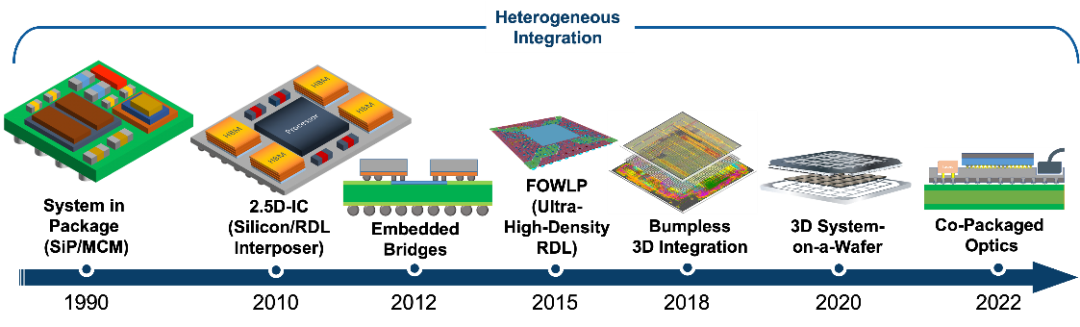

雖然先進(jìn)異構(gòu)集成仍處于發(fā)展的早期階段,但在一個共同的基板(陶瓷、硅/玻璃或有機(jī)物)上并排集成不同的芯片和分立元件并不是什么新概念。多芯片模塊 (multichip module,MCM) 和 SiP 等技術(shù)已經(jīng)問世了幾十年,每種技術(shù)都有各種不同的應(yīng)用場景。

異構(gòu)集成將 SiP 設(shè)計向前推進(jìn)了一大步,將其與 2.5D/3D-IC、扇出型芯片級封裝 (FOWLP)、硅和玻璃中介層以及嵌入式橋接器等尖端封裝和互連技術(shù)相結(jié)合。

異構(gòu)集成還能為 HPC 和服務(wù)器市場等應(yīng)用提供更大、更強(qiáng)大的芯片。在這些應(yīng)用中,封裝本身可以直接集成大量的內(nèi)存;而這在 SoC 上是根本不可能實(shí)現(xiàn)的。

然而,異構(gòu)集成也有一些注意事項。設(shè)計工作并沒有因?yàn)橛辛水悩?gòu)集成而變得簡單,反而變得更為復(fù)雜。從單一的單片 SoC 過渡到系統(tǒng)級架構(gòu),需要重新考慮原本 SoC 可以有效應(yīng)對的不良因素,如熱、電和機(jī)械性張力。在嘗試設(shè)計異質(zhì)集成芯片之前,采用正確的工具、方法和團(tuán)隊協(xié)作方式是至關(guān)重要的。

異構(gòu)集成還意味著信號路徑延長、I/O 數(shù)量增多和外形尺寸更大——這些都是不利于實(shí)現(xiàn)高效PPA的因子。異構(gòu)集成設(shè)計的芯片,其形狀參數(shù)在 X 和 Y 平面積上會變大,如果實(shí)施 3D 堆疊,甚至 Z 方向高度也會變大,而這是不可避免的。

而且異構(gòu)集成中,chiplets 的封裝方式對芯片的成功至關(guān)重要。這意味著在設(shè)計階段需要格外關(guān)注封裝技術(shù),無論是 2.5D、3D-IC,還是其他的封裝技術(shù)。

系統(tǒng)級芯片和異構(gòu)集成——

如何為設(shè)計項目選擇?

這個問題的答案在很大程度上取決于具體的應(yīng)用、設(shè)計預(yù)算,以及預(yù)期出貨片的總產(chǎn)品數(shù)量。隨著越來越多的應(yīng)用范例不斷涌現(xiàn),它們需要使用強(qiáng)大的人工智能 (AI) 和用在邊緣計算并采用高性能計算 (HPC) 的自主系統(tǒng),因此僅采用SoC 技術(shù)可能會達(dá)到其能力的物理極限。先進(jìn)異構(gòu)集成自然而然地成為了下一步的選擇。

然而,總會有很多應(yīng)用在 PPA 方面無法達(dá)成妥協(xié),在這種情況下,SoC 將仍然是最佳選擇。

3D-IC 有望在網(wǎng)絡(luò)、圖形、AI/ML 和高性能計算等領(lǐng)域產(chǎn)生廣泛影響,特別是對于需要超高性能、低功耗器件的應(yīng)用而言。具體的應(yīng)用領(lǐng)域包括多核 CPUs、GPUs、數(shù)據(jù)包緩沖器/路由器、智能手機(jī)和 AI/ML 應(yīng)用。

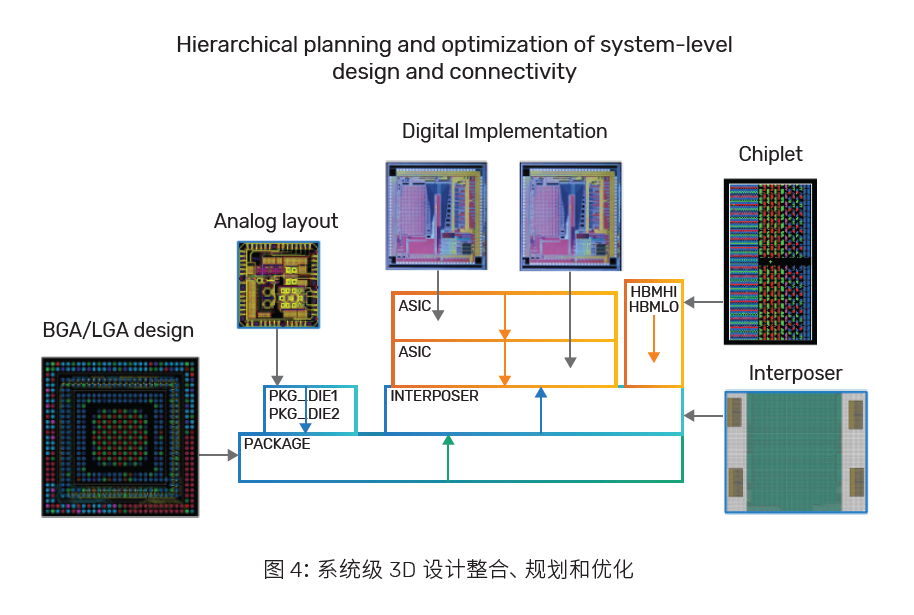

從設(shè)計的角度來看,要實(shí)現(xiàn)真正的 3D 集成,需要對某些設(shè)計工具進(jìn)行一些加強(qiáng)。尤其在架構(gòu)分析、熱分析、多裸片間的排置、時序、測試和驗(yàn)證方面的功能都需要提升。此外,還需要新的系統(tǒng)級功能,如頂層規(guī)劃和優(yōu)化、芯片裸片(die)之間和晶粒(chiplet)之間的信號完整性和 IC/封裝協(xié)同設(shè)計。

想要進(jìn)一步了解 3D 集成和多個堆疊裸片封裝的設(shè)計挑戰(zhàn)、生態(tài)系統(tǒng)要求和所需的解決方案嗎?

-

芯片

+關(guān)注

關(guān)注

459文章

52494瀏覽量

440672 -

soc

+關(guān)注

關(guān)注

38文章

4387瀏覽量

222718

發(fā)布評論請先 登錄

車規(guī)級和消費(fèi)級有什么區(qū)別?為什么自動駕駛需要車規(guī)級?

全志科技多核異構(gòu)SoC助力行業(yè)智能化創(chuàng)新

上揚(yáng)軟件助力12英寸異構(gòu)堆疊芯片企業(yè)建設(shè)MES系統(tǒng)項目

從片上系統(tǒng)(SoC)到立方體集成電路(CIC)

人工智能應(yīng)用中的異構(gòu)集成技術(shù)

soc與其他集成電路的比較分析

soc芯片與傳統(tǒng)芯片的主要區(qū)別在哪

異構(gòu)集成封裝類型詳解

最新SOC芯片技術(shù)發(fā)展

SOC芯片的定義和應(yīng)用

soc芯片和mcu芯片區(qū)別在哪

SoC芯片與CPU芯片有什么區(qū)別

從芯片到系統(tǒng):SOC如何重塑電子產(chǎn)業(yè)

行業(yè)資訊 I 異構(gòu)集成 (HI) 與系統(tǒng)級芯片 (SoC) 有何區(qū)別?

行業(yè)資訊 I 異構(gòu)集成 (HI) 與系統(tǒng)級芯片 (SoC) 有何區(qū)別?

評論