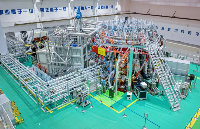

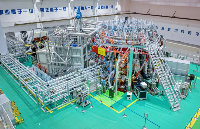

近日,由核工業(yè)西南物理研究院(簡稱“西物院”)研制的新一代人造太陽“中國環(huán)流三號”再次創(chuàng)下我國聚變裝置運(yùn)行新紀(jì)錄——實(shí)現(xiàn)百萬安培億度高約束模(H模),即裝置同時(shí)實(shí)現(xiàn)等離子體電流100萬安培、離子溫度

![的頭像]() 發(fā)表于

發(fā)表于 06-03 13:56

?396次閱讀

精彩看點(diǎn) 此次收購將幫助系統(tǒng)級芯片 (SoC) 設(shè)計(jì)人員通過經(jīng)市場檢驗(yàn)的時(shí)序約束管理能力來加速設(shè)計(jì),并提高功能約束和結(jié)構(gòu)約束的正確性 ? 西門子宣布 收購 Excellicon 公司 ,將該公司用于

![的頭像]() 發(fā)表于

發(fā)表于 05-20 19:04

?813次閱讀

本文重點(diǎn)PCBlayout約束管理在設(shè)計(jì)中的重要性Layout約束有助避免一些設(shè)計(jì)問題設(shè)計(jì)中可以使用的不同約束在PCB設(shè)計(jì)規(guī)則和約束管理方面,許多設(shè)計(jì)師試圖采用“一刀切”的方法,認(rèn)為同

![的頭像]() 發(fā)表于

發(fā)表于 05-16 13:02

?368次閱讀

摘要 :初始點(diǎn)的選擇對后續(xù)設(shè)計(jì)過程具有重大影響。除透鏡規(guī)格外,其它必要的實(shí)際約束條件也可能起到非常關(guān)鍵的作用。本研究采用“First Time Right”方法生成受約束的初始系統(tǒng),并運(yùn)用

發(fā)表于 05-07 08:57

Vivado中時(shí)序分析工具默認(rèn)會分析設(shè)計(jì)中所有時(shí)鐘相關(guān)的時(shí)序路徑,除非時(shí)序約束中設(shè)置了時(shí)鐘組或false路徑。使用set_clock_groups命令可以使時(shí)序分析工具不分析時(shí)鐘組中時(shí)鐘的時(shí)序路徑,使用set_false_path約束則會雙向忽略時(shí)鐘間的時(shí)序路徑

![的頭像]() 發(fā)表于

發(fā)表于 04-23 09:50

?453次閱讀

Vivado的時(shí)序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要創(chuàng)建xdc文件設(shè)置時(shí)序約束。時(shí)序約束文件可以直接創(chuàng)建或添加已存

![的頭像]() 發(fā)表于

發(fā)表于 03-24 09:44

?3508次閱讀

xilinx FPGA IOB約束使用以及注意事項(xiàng) 一、什么是IOB約束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距離IO最近的寄存器,同時(shí)位置固定。當(dāng)你輸入或者輸出

![的頭像]() 發(fā)表于

發(fā)表于 01-16 11:02

?896次閱讀

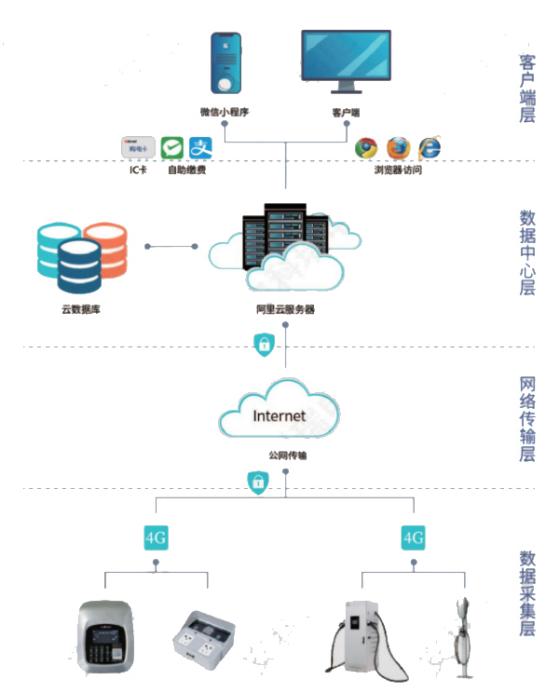

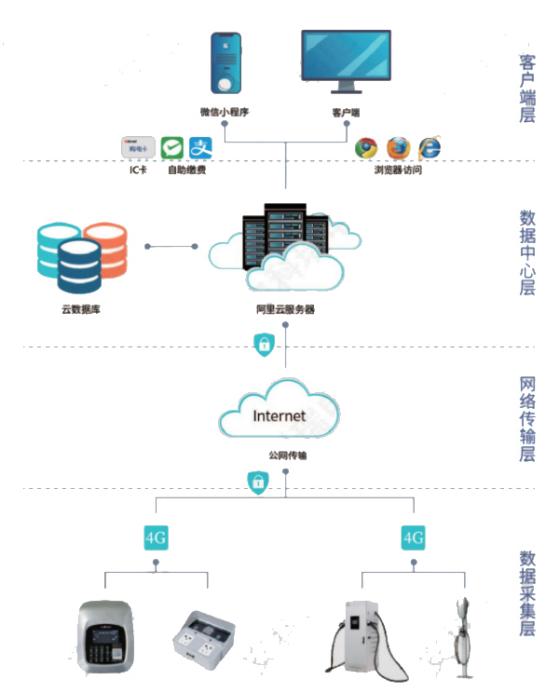

隨著電動汽車的普及,充電設(shè)施的需求日益增長,如何在多目標(biāo)優(yōu)化約束下實(shí)現(xiàn)充電設(shè)施的有序充電成為亟待解決的問題。新能源汽車的快速發(fā)展為清潔能源和可持續(xù)交通帶來了新機(jī)遇,但也引出了許多問題。其中,充電設(shè)施的有序充電控制策略在多目標(biāo)優(yōu)化約束條件下顯得尤為重要。

![的頭像]() 發(fā)表于

發(fā)表于 01-07 13:17

?487次閱讀

的輸出,對于Ultrascale和Ultrascale+系列的器件,定時(shí)器會自動地接入到GT的輸出。 1.2 約束設(shè)置格式 主時(shí)鐘約束使用命令create_clock進(jìn)行創(chuàng)建,進(jìn)入Timing

![的頭像]() 發(fā)表于

發(fā)表于 11-29 11:03

?1388次閱讀

為了防止約束失敗,我們在Tcl輸入框中驗(yàn)證,沒有告警或者錯誤說明約束的寫法是正確的set_max_delay 5.00 -from [get_cells key2_detect_inst/state

![的頭像]() 發(fā)表于

發(fā)表于 11-01 11:06

?572次閱讀

觸發(fā)器的約束條件主要涉及輸入信號和輸出信號的狀態(tài)。 以下是與非門構(gòu)成的RS觸發(fā)器的一些基本約束條件: 輸入信號的約束 : RS = 0 :當(dāng)R和S都為0時(shí),觸發(fā)器保持當(dāng)前狀態(tài)不變。這是因?yàn)閮蓚€與非門的輸入都是0,輸出Q和Q'將保

![的頭像]() 發(fā)表于

發(fā)表于 10-18 11:15

?4219次閱讀

,并且能夠在輸入信號發(fā)生變化時(shí)保持其輸出狀態(tài)。SR鎖存器(Set-Reset Latch)是一種基本的鎖存器類型,它由兩個交叉耦合的反相器和一個S(Set)輸入和一個R(Reset)輸入組成。本文將詳細(xì)介紹SR鎖存器的約束條件,以及如何根據(jù)這些條件進(jìn)

![的頭像]() 發(fā)表于

發(fā)表于 08-28 10:47

?1693次閱讀

電路的兩類約束通常指的是電氣約束和物理約束。這兩類約束在電路設(shè)計(jì)和分析中起著至關(guān)重要的作用。 一、電氣約

![的頭像]() 發(fā)表于

發(fā)表于 08-25 09:34

?2027次閱讀

建立時(shí)間和保持時(shí)間是FPGA時(shí)序約束中兩個最基本的概念,同樣在芯片電路時(shí)序分析中也存在。

![的頭像]() 發(fā)表于

發(fā)表于 08-06 11:40

?1399次閱讀

基本約束條件: SR鎖存器是一種基本的數(shù)字邏輯電路,用于存儲一位二進(jìn)制信息。它有兩個輸入端:S(Set)和R(Reset),以及兩個輸出端:Q和Q'(Q的反相)。以下是SR鎖存器的基本約束

![的頭像]() 發(fā)表于

發(fā)表于 07-23 11:34

?1805次閱讀

XDC約束及物理約束的介紹

XDC約束及物理約束的介紹

評論