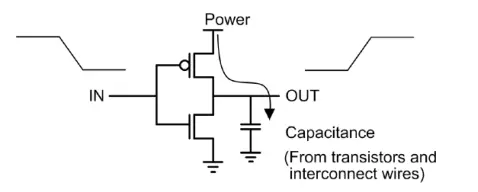

了解UltraScale DSP架構(gòu)及其如何幫助降低設(shè)計功耗,以及UltraScale時鐘架構(gòu)中的省電功能。 您還將學(xué)習(xí)估算DSP和時鐘的功率......

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

dsp

+關(guān)注

關(guān)注

555文章

8142瀏覽量

355188 -

賽靈思

+關(guān)注

關(guān)注

33文章

1795瀏覽量

132116 -

時鐘

+關(guān)注

關(guān)注

11文章

1879瀏覽量

132836

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

Xilinx Ultrascale系列FPGA的時鐘資源與架構(gòu)解析

Ultrascale是賽靈思開發(fā)的支持包含步進功能的增強型FPGA架構(gòu),相比7系列的28nm工藝,Ultrascale采用20nm的工藝,主要有2個系列:Kintex和Virtex

光模塊DSP,邁入低功耗

電子發(fā)燒友網(wǎng)報道(文/梁浩斌)? 隨著光模塊往800G、1.6T的高速方向發(fā)展,DSP也正在迎來越來越大的挑戰(zhàn),包括性能、功耗等。由于光模塊體積小,散熱困難,高性能DSP的功耗決定了在

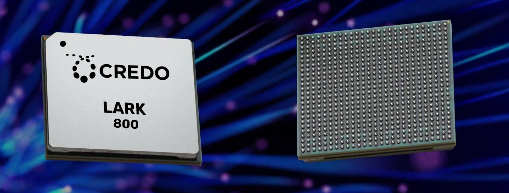

Credo發(fā)布Lark系列——為低功耗800G光學(xué)DSP樹立新標桿

榮幸地宣布:推出其超低功耗的Lark系列光DSP產(chǎn)品。 Lark系列包含兩款創(chuàng)新光DSP產(chǎn)品。Lark 800是一款高性能、高可靠性、低功耗的DSP

如何使ADS1247功耗降低?

請問如何使ADS1247功耗降低,我用CC2530控制1247,現(xiàn)在整體功耗在休眠時候是5V0.45mA,但是1247說明上有一句說是:在睡眠模式下功耗只有0.1-0.5uA,我已經(jīng)

發(fā)表于 01-10 07:58

如何降低AFE4400的功耗?

用AFE4400做血氧采集的前端,因為設(shè)備的功耗要求比較嚴格,現(xiàn)有的AFE4400的功耗為1.18Ma。請問能不能再把功耗降低?是否還有可降低

發(fā)表于 01-10 07:17

EE-216:估算ADSP-21262S SHARC DSP的功耗

電子發(fā)燒友網(wǎng)站提供《EE-216:估算ADSP-21262S SHARC DSP的功耗.pdf》資料免費下載

發(fā)表于 01-08 14:46

?0次下載

如何降低電子開關(guān)的功耗

電子開關(guān)是現(xiàn)代電子系統(tǒng)中不可或缺的組成部分,它們控制電流的流動,實現(xiàn)設(shè)備的開啟和關(guān)閉。然而,隨著電子設(shè)備功能的增強和集成度的提高,功耗問題也日益突出。降低電子開關(guān)的功耗不僅有助于節(jié)約能源,還能

Zynq UltraScale+ MPSoC數(shù)據(jù)手冊

電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+ MPSoC數(shù)據(jù)手冊.pdf》資料免費下載

發(fā)表于 12-30 14:37

?2次下載

如何降低AD1247的功耗?

為了使AD1247進入睡眠模式以降低功耗嘗試了以下兩種方法:

1、將START置為低電平 ,但是至低電平后電流沒有變化;

2、通過SLEEP指令,這個進入睡眠后AD1247的確不工作了,喚醒之后

發(fā)表于 12-24 07:51

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

“Versal AI 引擎可以在降低功耗預(yù)算的情況下提高 DSP 計算密度,”高級產(chǎn)品營銷經(jīng)理 Udayan Sinha 表示。這種效率使 Versal AI 引擎能夠在嚴格的功耗預(yù)算內(nèi)處理最苛刻

物聯(lián)網(wǎng)系統(tǒng)中TCP低功耗產(chǎn)品長連接狀態(tài)下降低功耗功能的實現(xiàn)方案

01 ?概述 TCP相關(guān)內(nèi)容參考文章《物聯(lián)網(wǎng)行業(yè)中TCP通信協(xié)議介紹以及如何實現(xiàn)》 02 ?功耗的組成 低功耗技術(shù)就是一系列的降低功耗的技術(shù)。 在了解低

OPA454如何降低功耗?

opa454 供電+60V/-15V,輸出空載懸空,放大倍數(shù)5倍,同向放大,輸入0~10V正弦波100hz,輸出為50v正弦波,發(fā)現(xiàn)功耗很大,有降低功耗措施?

發(fā)表于 07-29 06:32

wifi smartconfig時功耗比較大,如何降低?

現(xiàn)在wifi 的smartconfig 時候功耗比較大,現(xiàn)在達不到要求,需要在配網(wǎng)時降低10mA。

1,如何通過編程的手段進行降低?

2,這個需要考慮配網(wǎng)時跟路由器之間的距離嗎?

發(fā)表于 07-10 08:09

有沒有降低ESp8266功耗的方法?

與ESP8266使用UART連接。

目前,我選擇的是支持AT命令的固件,目前的問題是ESp8266,開機后電流大約為60mA,有沒有降低功耗的方法???

我看到ESP8266保持連接(不發(fā)數(shù)據(jù))的平均功耗很低啊!

發(fā)表于 07-08 06:30

一個更適合工程師和研究僧的FPGA提升課程

設(shè)計;

● UltraFast 設(shè)計方法;

● 使用UltraScale和UltraScale+架構(gòu)進行設(shè)計;

● FPGA 功耗最優(yōu)化;

● 使用 Vivado De

發(fā)表于 06-05 10:09

了解UltraScale DSP架構(gòu)如何降低設(shè)計功耗

了解UltraScale DSP架構(gòu)如何降低設(shè)計功耗

評論