DSP? 的系統(tǒng)生成器是業(yè)界領先的架構級*設計工具,可在 Xilinx 器件上定義、測試并實現(xiàn)高性能 DSP 算法。DSP 的系統(tǒng)生成器按照 Simulink? 的附加工具套件精心設計,可充分利用針對 FPGA 架構優(yōu)化的預先存在的 IP,其可由用戶進行參數(shù)化,達到算法的質量及成本目標。與傳統(tǒng) RTL 開發(fā)時間相比,DSP 系統(tǒng)生成器的特性加上 Simulink? 提供的豐富仿真及驗證環(huán)境的優(yōu)勢,只需一小部分時間就能創(chuàng)建生產質量級的 DSP 算法。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

dsp

+關注

關注

556文章

8157瀏覽量

357502 -

FPGA

+關注

關注

1645文章

22049瀏覽量

618379 -

賽靈思

+關注

關注

33文章

1797瀏覽量

132352

發(fā)布評論請先 登錄

相關推薦

熱點推薦

如何在Unified IDE中創(chuàng)建視覺庫HLS組件

Vivado IP 流程(Vitis Unified),在這篇 AMD Vitis HLS 系列 3 中,我們將介紹如何使用 Unifie

使用AMD Vitis Unified IDE創(chuàng)建HLS組件

這篇文章在開發(fā)者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統(tǒng) IDE) 的基礎上撰寫,但使用的是 AMD Vitis Unified IDE,而不是之前傳統(tǒng)版本的 Vitis

如何使用AMD Vitis HLS創(chuàng)建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 來創(chuàng)建一個 HLS IP,通過 AXI4 接口從存儲器讀取數(shù)據(jù)、執(zhí)行簡單的數(shù)學運算,然后將數(shù)據(jù)寫回存儲器。接著會在 AMD Vivado

Vivado HLS設計流程

為了盡快把新產品推向市場,數(shù)字系統(tǒng)的設計者需要考慮如何加速設計開發(fā)的周期。設計加速主要可以從“設計的重用”和“抽象層級的提升”這兩個方面來考慮。Xilinx 推出的 Vivado HLS 工具可以

EB Tresos狀態(tài)顯示無法運行生成器是什么原因導致的?

我正在嘗試集成 MCAL 包,但在生成過程中收到如下驗證錯誤:“無法為模塊”Dio_TS_T40D2M20I0R0“運行生成器

發(fā)表于 04-02 08:06

Python中的迭代器與生成器

Python迭代器與生成器 列表生成式 列表生成式也叫做列表推導式,它本身還是列表,只不過它是根據(jù)我們定義的規(guī)則來生成一個真實的列表。 ? ? list2 = [x for x in

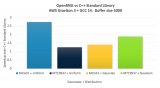

開源隨機數(shù)生成器庫OpenRNG助力實現(xiàn)移植到Arm平臺時的最佳性能

OpenRNG 實現(xiàn)了多種生成器和分布方式。生成器算法可生成“看似隨機”并具有某些統(tǒng)計特性的序列,我們將在下文進行討論。分布方式會將序列映射到常見的概率分布概念,如高斯分布或二項分布

超詳細!FMU生成器用戶手冊來啦~

FMU生成器是TSMaster中用于將模型打包生成FMU文件的一個工具,目前支持FMI3.0和FMI2.0版本,F(xiàn)MU類型僅支持Co-Simulation(CS),即聯(lián)合仿真FMU。本文將介紹

EE-322:面向SHARC處理器的專家代碼生成器

電子發(fā)燒友網站提供《EE-322:面向SHARC處理器的專家代碼生成器.pdf》資料免費下載

發(fā)表于 01-07 14:04

?0次下載

SRIO介紹及xilinx的vivado 2017.4中生成srio例程代碼解釋

1. 概述 本文是用于記錄srio的學習情況,以及一些對xilinx的vivado 2017.4中生成srio例程代碼的解釋。 2. 參考文件 《pg007_srio_gen2》 3. SRIO協(xié)議

使用C2000?嵌入式模式生成器(EPG)進行設計

電子發(fā)燒友網站提供《使用C2000?嵌入式模式生成器(EPG)進行設計.pdf》資料免費下載

發(fā)表于 09-14 10:13

?1次下載

Freepik攜手Magnific AI推出AI圖像生成器

近日,設計資源巨頭Freepik攜手Magnific AI,共同推出了革命性的AI圖像生成器——Freepik Mystic,這一里程碑式的發(fā)布標志著AI圖像創(chuàng)作領域邁入了一個全新的高度

優(yōu)化 FPGA HLS 設計

優(yōu)化 FPGA HLS 設計

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設計性能。

介紹

高級設計能夠以簡潔的方式捕獲設計,從而

發(fā)表于 08-16 19:56

TSMaster 測試報告生成器操作指南

用戶在基于TSMaster軟件開發(fā)測試用例時,或需要使用TSMaster生成HTML報告時,需要使用TSMaster測試報告生成器。1Test_Report說明Test_Report是目前

用于系統(tǒng)生成器中Vivado HLS IP模塊介紹

用于系統(tǒng)生成器中Vivado HLS IP模塊介紹

評論