隨著器件集成工藝的發(fā)展和Soc器件的出現(xiàn),現(xiàn)在的數(shù)字系統(tǒng)正在越來越多地采用可編程器件設計。這樣,不僅開發(fā)周期短,而且在價格和使用難易度上也顯示了很大的優(yōu)勢。更為重要的是,還能利用器件的現(xiàn)場可編程特性,根據(jù)應用的要求對器件進行動態(tài)配置,簡便易行地完成功能的添加或變化。

在高速的數(shù)字信號處理系統(tǒng)中,要涉及到大量的計算,為了提高運算速度,正大量使用DSP器件。目前的可編程器件,其時鐘頻率可以很高,在高速數(shù)字信號處理系統(tǒng)中將發(fā)揮越來越大的作用。因此,DSP+FPGA的方案正越來越多地被電子工程師們采用。

在很多的實際數(shù)字系統(tǒng)中,往往需要良好的用戶界面,其中LCD是被大量采用的顯示器件。由于LCD是典型的慢速設備(相對于DSP來講),在與高速微處理器接口時,會耗費大量時間,這在高速系統(tǒng)設計中是不允許的。如果DSP有不太富裕的處理余量,如何利用它對LCD完成控制呢?僅僅在兩者之間加入鎖存器之類的簡單接口電路,往往不能對LCD完成控制。不過,有了FPGA,就可以在不增加成本的情況下,在DSP和LCD之間設計一條雙向的快速通道。

1 DSP和LCD的時序

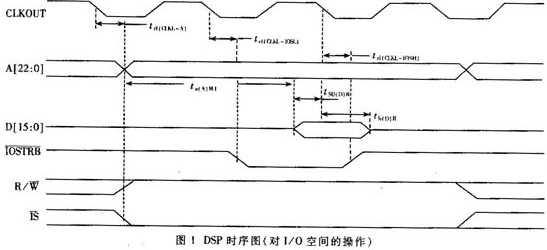

TI公司是DSP在全球的主要供應商,其低價位的TMS320VC54x系列DSP深受廣大電子工程師的青睞。下面以TMS320VC5416為例介紹DSP的時序。TMS320VC5416將尋址范圍分為存儲器空間、程序空間和I/O空間。其中,對I/O空間的操作由地址線、數(shù)據(jù)線和三根信號線IOSTRB、R/W和IS來完成,其時序圖如圖1所示。

讀操作和寫操作由R/W信號線上的高低電平?jīng)Q定。如果不采用外部插入等待周期的方法,僅靠內部的等待周期設置寄存器,訪問外部I/O空間時最多可以插入14個等待周期。如果DSP運行在100MHz的主頻上(實際上TMS320VC16可以運行在最高160MHz的主頻上),也只有0.14μs。這對于LCD來說來遠遠不夠的。

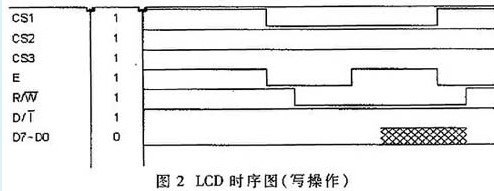

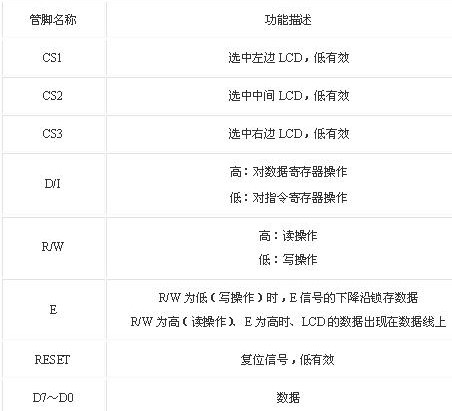

常見的192×64點陣的LCD(FM19264)實際上是由3塊獨立的64×64點陣LCD構成的,共享地址線和數(shù)據(jù)線,可由CS1、CS2和CS3分別選中。每小塊LCD都有各自獨立的指令寄存器和數(shù)據(jù)寄存器,由控制線D/I上的高低電平選擇。數(shù)據(jù)的鎖存或出現(xiàn)在數(shù)據(jù)線上由E信號決定。LCD主要控制管腳的功能如表1所示。對LCD寫操作的時序圖如圖2所示。LCD的每次讀寫操作最少要1μs。如果能使DSP對LCD的訪問象對高速設備訪問一樣,就能夠最大限度地減小DSP資源的浪費,并且能夠減少系統(tǒng)的復雜性,這就需要在FPGA中添加一個DSP與LCD之間的高速雙向通道。

表1 LCD主要控制管腳功能

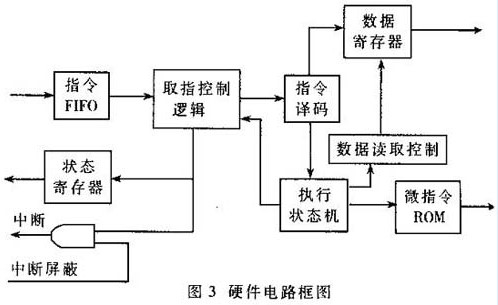

對每塊LCD的控制,是通過操作指令寄存器和數(shù)據(jù)寄存器實現(xiàn)的。在屏幕指定位置寫入數(shù)據(jù),要分三步(①寫入行地址,②寫入列地址,③寫入數(shù)據(jù))才能完成,不但耗時而且增加了軟件編程的復雜程度。如果能夠將指令和數(shù)據(jù)合在一起作為一條指令,那么設計一套簡單的指令譯碼電路執(zhí)行電路就可完成這項任務。

2 硬件電路設計

硬件框圖如圖3所示。LCD的原始控制指令如表2所示。

表2 LCD原始控制指令

LCD的顯示畫面按8行為一頁的方式進行劃分,共64行分成8頁。LCD具有列循環(huán)尋址功能,如果第一步設定了頁地址和列地址,那么以后每次向LCD寫入顯示數(shù)據(jù),列地址計數(shù)器就自動加一。除非再設定列地址,否則列地址就一直累加下去,直到63。這樣就簡化了寫入工作。

考慮到實際應用方便,可把一些常用的操作按指令的方式編碼。所得到的DSP控制指令如下:

控制顯示器開關:0010 0000 1111 111x

指定顯示起始行:0100 0000 11xx xxxx

指定列地址和頁地址:0110 0yyy yyyy yxxxy:

列地址(0~191)x:

行地址寫入數(shù)據(jù):1000 0000 xxxx xxxx

讀顯示器狀態(tài):1010 0000 0000 0000

讀顯示數(shù)據(jù):1100 0000 0000 0000

框圖中微指令ROM在接口控制中起著決定性的作用,每條指令的執(zhí)行都被看作一系列單步時序操作的集合。如果從ROM的某一地址開始依次讀出ROM里的數(shù)據(jù),那么在每一個數(shù)據(jù)位上就會出現(xiàn)隨時間變化的電平跳變。這樣就可以用它作為控制信號進行控制操作。由于ROM是并行輸出的,如果用不同的數(shù)據(jù)位代表不同的控制信號線,就能很容量地實現(xiàn)各個信號線之間的同步操作。這樣就能很容易形成時序圖中的時序邏輯,而且擴展方便。在上述的指令表示中,通過對高3位進行譯碼,可以得到ROM尋址時的起始地址。ROM各個數(shù)據(jù)位的含義如下:

[table][/table] 其中,低七位是控制LCD的接口線,F(xiàn)REE是微程序執(zhí)行完標志,每條指令所對應的微程序分為招待狀態(tài)(有多條微指令,F(xiàn)REE位為0)和閑置狀態(tài)(一條指令,F(xiàn)REE位為1)。當指令執(zhí)行狀態(tài)機檢測到FREE位的上跳沿時,加載下一條指令。LD是數(shù)字寄存器從DSP獲得數(shù)據(jù)時的加載信號,微程序執(zhí)行過程中,在某些指令執(zhí)行時需要加載數(shù)據(jù),可由該信號完成。RD是數(shù)據(jù)寄存器從LCD讀入數(shù)據(jù)的加載信號,主要完成從LCD讀入數(shù)據(jù)。

取指控制邏輯主要功能是根據(jù)FIFO的狀態(tài)決定是否寫入新的指令以及根據(jù)執(zhí)行狀態(tài)機的狀態(tài)讀入新的指令,填寫狀態(tài)寄存器,給出中斷信號。

根據(jù)上述硬件設計,DSP的軟件設計就大大簡化了。以寫入數(shù)據(jù)為例,在寫入數(shù)據(jù)前先查詢一下接口模塊的狀態(tài),如果可以寫入就寫入數(shù)據(jù);否則保持現(xiàn)有數(shù)據(jù)指針,等待下次寫入。一讀一寫兩次外部I/O操作,如果按7個等待周期、主頻100MHz計算,只有140ns,加上判斷所需時間,200ns內就可以完成寫入數(shù)據(jù)。這里,7個等待周期是考慮到系統(tǒng)內還其它器件。如果只是對該接口模塊操作,兩三個等待周期是沒有問題的。這樣,100ns內就可完成寫入數(shù)據(jù)。

在實際應用中,采用上述接口控制模塊來完成LCD控制大大減輕了DSP的壓力。推而廣泛,這種方法還可以應用在其它慢速設備上,如打印機等,對于提高系統(tǒng)效率是比較有效的。需要指出的是,盡管這種方法能夠建立雙向快速通道,卻是以占用可編程器件有限的資源為代價的。但是隨著目前可編程器件容量的日益擴大,這個問題已不是很突出的了。

-

dsp

+關注

關注

555文章

8142瀏覽量

355215 -

FPGA

+關注

關注

1643文章

21960瀏覽量

614059 -

寄存器

+關注

關注

31文章

5421瀏覽量

123324

發(fā)布評論請先 登錄

在高清晰LCD HDTV 中使用Cyclone III FPGA

基于DSP+FPGA多視頻通道的切換控

DSP與FPGA之間的通信如何實現(xiàn)

采用FPGA實現(xiàn)直接數(shù)字頻率合成器設計

如何利用DSP和FPGA技術檢測低信噪比雷達信號?

實現(xiàn)CAN與串口UART之間的雙向數(shù)據(jù)智能轉換

利用Mentor高層次綜合技術快速實現(xiàn)復雜DSP算法

基于DSP和FPGA的HDLC協(xié)議通訊電路設計

利用FPGA和DSP結合實現(xiàn)雷達多目標實時檢測

TI中基于DSP和FPGA的三電平逆變器快速控制方法

微軟面向Windows 10快速通道推送更新 默認應用配置界面新增搜索功能

在FPGA和DSP兩種處理器之間實現(xiàn)SRIO協(xié)議的方法

NanoEdge AI studio-創(chuàng)建智能產(chǎn)品的快速通道

利用FPGA技術實現(xiàn)DSP和LCD之間雙向快速通道的設計

利用FPGA技術實現(xiàn)DSP和LCD之間雙向快速通道的設計

評論