隨著超大規(guī)模集成電路(Very Large Scale Integration VLSI)工藝技術的發(fā)展,芯片的規(guī)模越來越大,集成規(guī)模以摩爾定律增長。現(xiàn)場可編程邏輯器件(FPGA)由于兼具可編程邏輯器件的現(xiàn)場可編程的靈活性,以及門陣列器件集成度高的優(yōu)點,在數(shù)字系統(tǒng)設計被廣泛采用。同時,ASIC技術的不斷完善以及功能強大的EDA軟件開發(fā)平臺的出現(xiàn),使得FPGA器件在現(xiàn)代數(shù)字系統(tǒng)設計和微電子技術應用中起著越來越重要的作用。近幾年來,Xilinx等公司推出了內(nèi)部嵌入存儲器、微處理器的FPGA器件,使得這種器件的應用更顯其優(yōu)越性;但在某些應用場合如數(shù)據(jù)采集時,需要將采集到的數(shù)據(jù)傳送給PC機,然后由PC機進行數(shù)據(jù)處理,這時就要借助單片機來完成。因此,有必要在FPGA器件中設計一種通信接口電路,以使設計的應用系統(tǒng)具備通信功能。由于SCI通信接口電路具有結構相對簡單、易于實現(xiàn)等特點,因此本文以SCI接口電路為例介紹基于FPGA器件實現(xiàn)的接口電路IP核的設計。

SCI接口電路結構

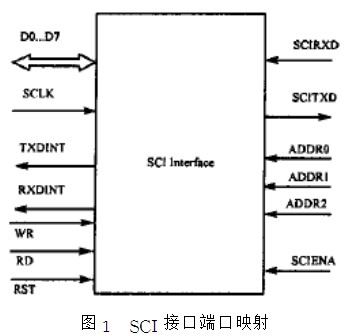

SCI接口端口映射

SCI的端口映射如圖1所示,共有20個端口,各端口的功能為:

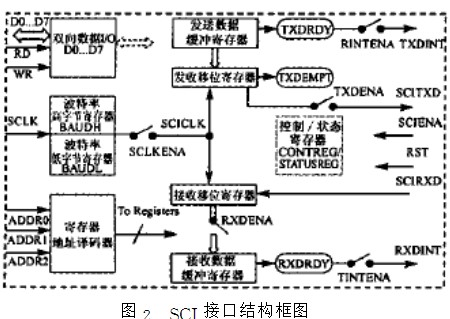

SCI接口結構框圖

為SCI接口內(nèi)部結構框圖如圖2所示,主要包括以下單元:

發(fā)送器(TX)及其控制與狀態(tài)寄存器。發(fā)送數(shù)據(jù)緩沖寄存器(TXBUF0…7)包含SCI接口要發(fā)送的數(shù)據(jù);發(fā)送移位寄存器(TXSHF);發(fā)送狀態(tài)寄存器位(TXRDY、TXEMPT);發(fā)送控制寄存器位(TINTENA、TXENA)。

接收器(RX)及其控制與狀態(tài)寄存器。接收數(shù)據(jù)緩沖寄存器(RXBUF0…7)包含SCI接口從SCIRXD接收到的數(shù)據(jù);接收移位寄存器(RXSHF);接收狀態(tài)寄存器位(RXRDY);接收控制寄存器位(RINTENA、RXENA)。

可編程波特率發(fā)生器。由波特率高byte寄存器和波特率低byte寄存器組成,可得到64k種不同的位傳輸速率。當系統(tǒng)時鐘為10MHZ時,其位傳輸速率為19.07~625.0kb/s。寄存器地址譯碼器。寄存器地址譯碼器負責對ADDR0…ADDR2進行譯碼,確保能讀/寫SCI中相應的寄存器。其與RD和WR配合完成對SCI內(nèi)部各寄存器的讀/寫操作。

數(shù)據(jù)傳輸格式

為簡化設計,SCI以固定的串行數(shù)據(jù)格式傳送數(shù)據(jù),采用NRZ幀格式對數(shù)據(jù)進行編碼,一個數(shù)據(jù)由1bit起始位、8bit數(shù)據(jù)位和一個停止bit共10bit組成。為確保采樣到的數(shù)據(jù)位可靠,選取每位數(shù)據(jù)包含8個SCICLK周期。

波特率的產(chǎn)生

SCI內(nèi)部的串行時鐘(SCICLK)由系統(tǒng)時鐘SCLK與波特率寄存器共同決定。通過16bit波特率選擇寄存器,可以為內(nèi)部串行時鐘提供64k種不同的傳輸速率,其計算公式為:

Baud=SCLK/[(BRR+1)*8]其中BRR為16bit波特率選擇寄存器的值。

SCI異步通信

如前所述,在異步通信模式下一幀數(shù)據(jù)包含一個起始bit、8個數(shù)據(jù)bit、一個停止bit。每個數(shù)據(jù)位占用8個SCICLK周期。

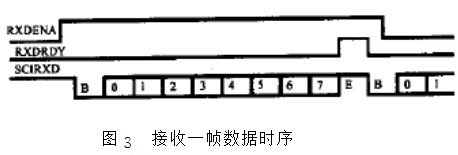

接收數(shù)據(jù)時序

接收器在收到有效的起始位后開始操作,有效的起始位由連續(xù)的0電平組成,長度為4個連續(xù)的內(nèi)部SCICLK周期。對于起始位后的各位,接收器通過對該位的中間進行3次采樣來決定位值,采用在第4、第5、第6個SCICLK周期,位值取決于多數(shù)采樣點的值。數(shù)據(jù)從SCIRXD進入RXSHF,移位進入RXBUF寄存器,并產(chǎn)生中斷請求,RXDRDY置1,表示已經(jīng)接收到新字符]。接收一幀數(shù)據(jù)的時序如圖3所示。

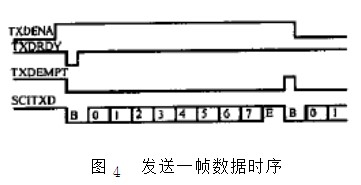

發(fā)送數(shù)據(jù)時序

發(fā)送器與接收器工作原理基本相同,在TXDRDY為低時,向發(fā)送數(shù)據(jù)緩沖寄存器寫入一個數(shù)據(jù)后啟動發(fā)送;然后數(shù)據(jù)進入TXSHF,同時TXDRDY為高,表示TXBUF可以寫入新值,并產(chǎn)生一個中斷請求。數(shù)據(jù)發(fā)送時序如圖4所示。

VerilogHDL實現(xiàn)

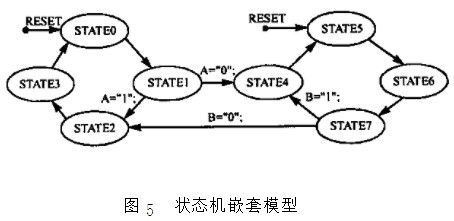

狀態(tài)機嵌套模型

由于SCI接口牽涉到復雜的狀態(tài)機描述,需要采用有限狀態(tài)機的嵌套,形成樹狀的控制邏輯。這一點和所提倡的層次化、結構化的自頂向下的設計方法相吻合。圖5是一種簡單的狀態(tài)機嵌套模型。

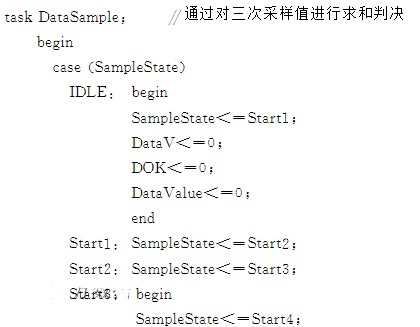

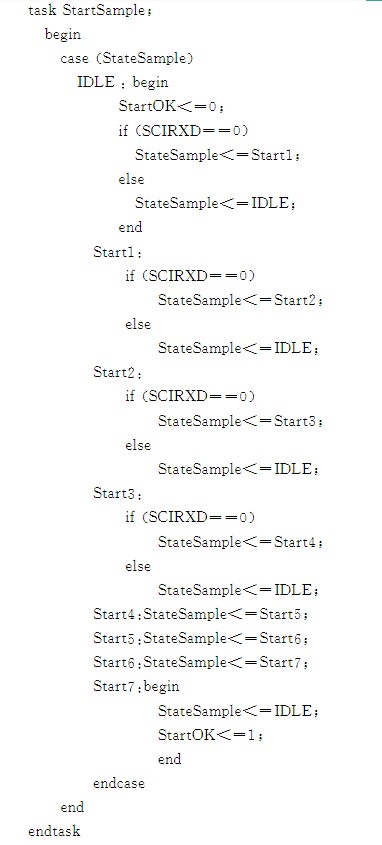

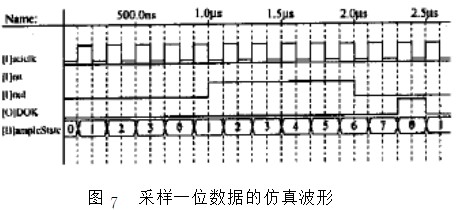

采樣一位數(shù)據(jù)的狀態(tài)機

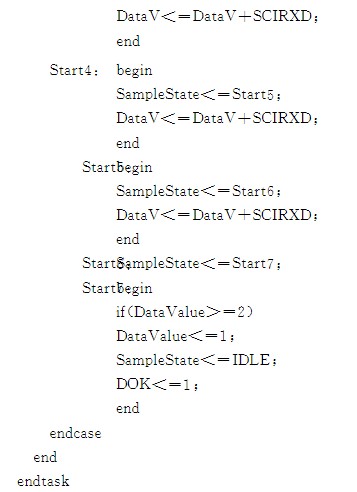

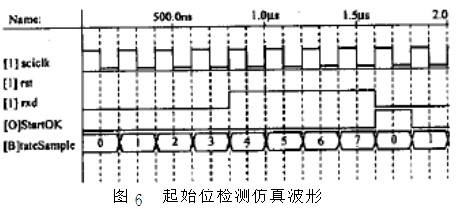

接收數(shù)據(jù)起始位檢測狀態(tài)機

仿真結果

由圖7仿真波形可知,采樣一位數(shù)據(jù)的狀態(tài)機在數(shù)據(jù)位的第4、5、6個內(nèi)部sclk時鐘進行。位值由多數(shù)采樣的值決定,圖中rxd在第4、5、6圖7采樣一位數(shù)據(jù)的仿真波形個sclk時的值為1,故dok在第8個sclk時鐘輸出1,表示此次采樣的一位數(shù)據(jù)為1。

圖7采樣一位數(shù)據(jù)的仿真波形

結論

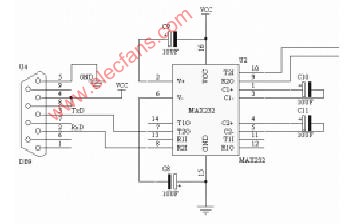

SCI接口電路由VerilogHDL語言描述,可讀性好,便于修改與測試,可方便地嵌入到用戶的FPGA系統(tǒng)。利用Xilinx公司的Spartan ⅡFPGAXC2S100成功地實現(xiàn)了FPGA與PC機的串行通信。如在此基礎上增加其它的控制寄存器,則可設計出功能更為完善的SCI接口電路。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614619 -

存儲器

+關注

關注

38文章

7637瀏覽量

166536 -

通信

+關注

關注

18文章

6182瀏覽量

137424

發(fā)布評論請先 登錄

怎么使用FPGA實現(xiàn)SPI總線的通信接口?

FPGA SERDES接口電路怎么實現(xiàn)?

通過FPGA實現(xiàn)溫控電路接口及其與DSP通信接口的設計

如何實現(xiàn)Simulink與DSP 28335之間的SCI通信

基于FPGA的通信接口模塊設計與實現(xiàn)

使用FPGA器件實現(xiàn)SCI通信接口電路的連接設計

使用FPGA器件實現(xiàn)SCI通信接口電路的連接設計

評論