MTM總線(Module Testing and Maintenance bus,MTMbus)是一種同步、串行、用于系統級的背板測試及維護總線,可以實現IEEE1149.5標準所規定的故障檢測、容錯以及擴展的命令集。該技術已經被美軍"寶石柱"和"寶石臺"計劃的航空電子系統體系結構采用。

當前MTM總線主模塊有限狀態機主要采用VerilogHDL程序編寫的狀態機描述,Verilog HDL語言并不可以進行系統級的硬件描述。

VHDL是一種標準化的硬件描述語言,不僅可以用于系統級的硬件描述而且在設計系統硬件時沒有嵌入與工藝有關的信息,在工藝更新時無須修改原設計程序。文中設計的狀態機采用"單進程"式狀態機描述,與"三進程"和"雙進程"式相比可以有效地節省FPGA芯片的資源,從而進一步減少功耗,提高系統的穩定性。

通過簡要分析MTM總線的基本結構、各模塊間的通訊方式、主模塊有限狀態機模型基于VHDL語言設計了主模塊有限狀態機;并且利用QuartusⅡ9.0版本軟件和Cyclone系列EP1C60240C6芯片對所設計的MTM總線主模塊狀態機的VHDL代碼進行了時序仿真和功能仿真。

1 MTM總線結構設計

1.1 MTM總線的基本結構

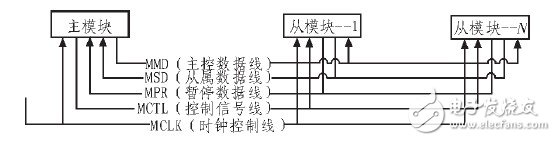

MTM總線的基本結構如圖1所示,總線定義了4條必選信號線和一條可選信號線,即MCTL(控制信號線)、MMD(主模數據信號線)、MSD(從模塊數據信號線)、MCLK(時鐘信號線)和MPR(請求暫停信號線)。

圖1 MTM總線結構圖

MTM總線上的所有模塊采用主從結構的通訊協議,該總線有且只能有一個主模塊,最多可以有250個能夠被獨立尋址的從屬模塊。MTM總線多站點結構和尋址能力允許主模塊一次可以尋址一個從模塊、多個從模塊(多點尋址方式)和所有的從模塊(廣播尋址方式),并且與之通訊。M TM總線的主模塊有限狀態機是MTM總線主模塊的核心控制單元,它控制著整個信息傳輸過程。MTM總線控者使用消息交換的方式與從模塊進行通訊,消息是由一系列的包組成,包括一個頭包,一個可選答應包和一系列數據包,包的長度為17位,高16位數據信息,最低位用于奇校驗,消息包的控制必須由主模塊控制。

1.2 MTM主模塊

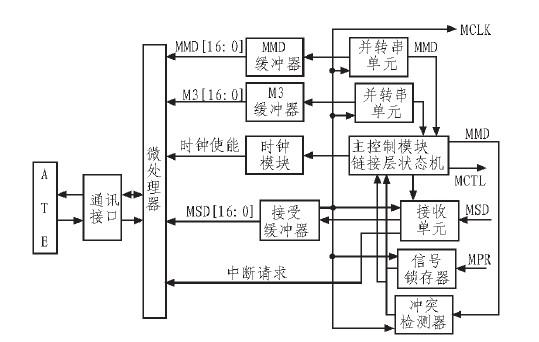

主控制模塊設計如圖2所示。主控制模塊在MTM總線協議中處于主控地位,主要功能是將來自微處理器的數據按照IEEE1149.5標準定義的消息格式進行打包送到指定的從控制模塊;同時將來自指定從控制模塊的消息包進行解包,并且提取有用數據傳回微處理器,供微處理器分析和處理。

圖2 主控制模塊設計

主狀態機是主控制模塊的核心單元,它的作用是控制整個信息傳輸過程。

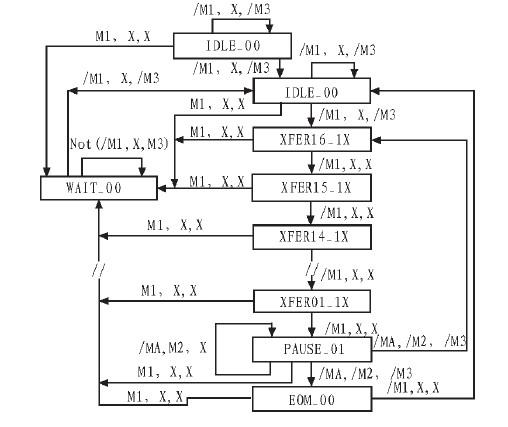

主狀態機的狀態轉換圖如圖3.當主狀態機處于某個給定的狀態時,MCTL和MMD信號的邏輯值在MCLK的上升沿產生;在每個MCLK信號周期,主狀態機根據控制信號的只發生狀態轉換;在主狀態機的17個傳送狀態下發送17位的數據包,其他狀態不發送數據,同時接收MSD上的數據;在每個數據包發送后,主狀態機至少保持在暫停狀態不少于4個MCLK周期,若當前接收的MSD數據有效則使接收單元使能信號有效;當主狀態機進入結束狀態時,當前消息傳送結束。

圖3 主狀態機的狀態轉換圖

2 基于VHDL的主模塊有限狀態機的的設計

VHDL主要用于描述數字系統的結構、行為、功能和接口,同時支持層次化和模塊化設計,并且可以進行仿真和綜合。

數字電路分為組合邏輯電路和時序邏輯電路兩種。組合邏輯電路的輸出只與當前輸入有關,時序邏輯電路的輸出與當前輸入和過去輸入都有關。狀態機是一種廣義的時序電路,一般包括用于狀態譯碼和產生輸出信號組合邏輯和存儲狀態的寄存器邏輯兩部分。

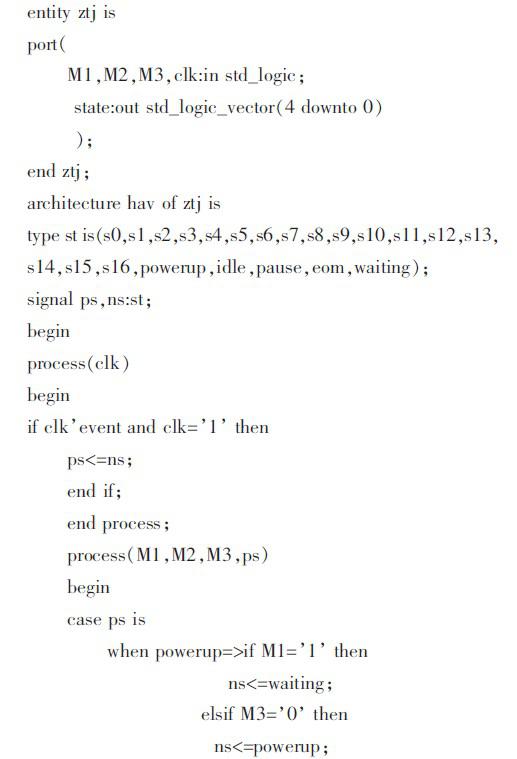

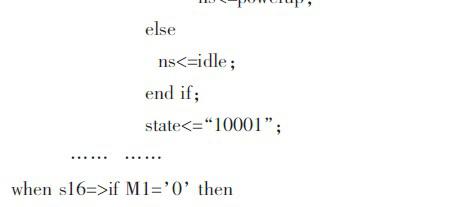

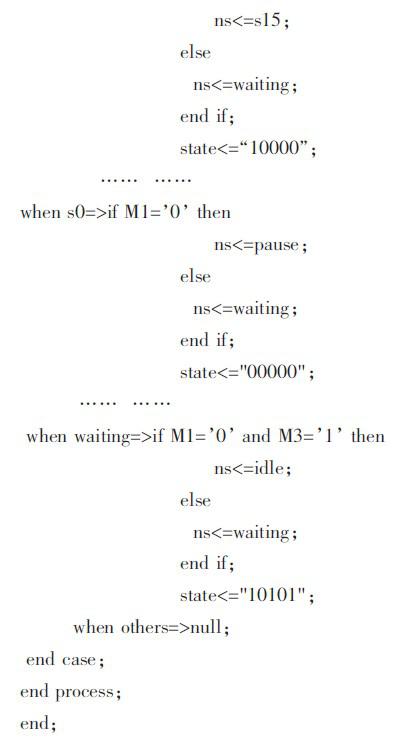

根據MTM總線主模塊的狀態轉換圖,其基于VHDL有限狀態機的代碼如下:

3 仿真驗證

QuartusⅡ是Altera公司推出的集成開發軟件,使用QuartusⅡ可以完成從設計輸入、綜合適配、仿真到編程下載整個設計過程,Quart usⅡ也可以直接調用Synplify Pro、以及ModelSim等第3方EDA工具來完成設計任務的綜合和仿真。

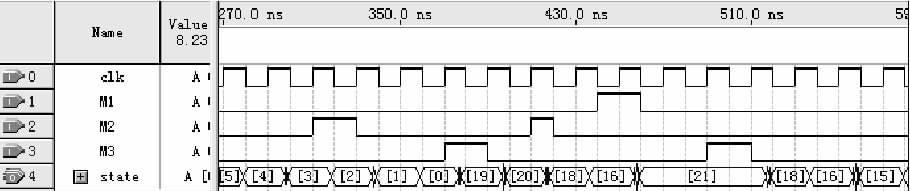

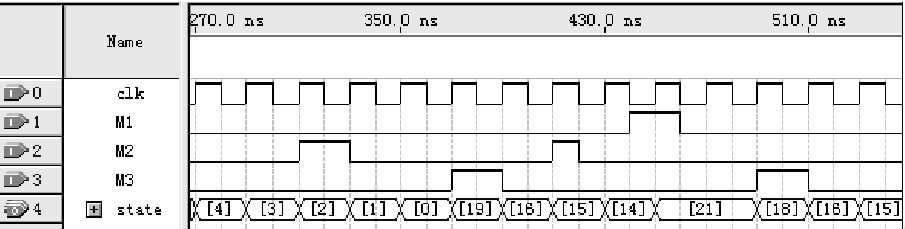

文中利用QuartusⅡ9.0版本軟件和Cyclone系列EP1C6Q240C6芯片對所設計的MTM總線主模塊狀態機的VHDL代碼進行了時序仿真和功能仿真,分別如圖4、圖5所示。

圖4 時序仿真波形圖

圖5 功能仿真波形圖

通過波形圖可以觀察到,該狀態機可以很好的實現主狀態機的狀態轉換。當M1輸入為"0"時(此時M2、M3為無關狀態),MTM總線主模塊按照從高到低進行消息傳送,直到進入"PAUSE"(暫停狀態)然后狀態回到"xfer16"(S16)繼續進行消息傳送;當M1輸入為"1"時,主模塊無條件進入"waiting"(等待狀態);在主模塊處于"waiting"狀態時若M3輸入為"1"狀態轉入"idle"(空閑狀態)再次由高到低位的消息傳送。

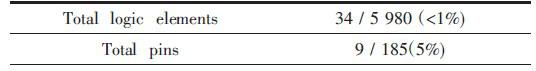

使用VHDL語言描述,語法更為嚴謹,描述更為清晰簡潔;采用"單進程"式狀態機描述可以有效地節省FPGA芯片的資源(表1),從而進一步減少功耗,提高系統的穩定性。

表1 編譯報告

4 結束語

文中通過研究MTM總線的基本結構和主從模塊間的通訊協議,分析了主狀態機的狀態轉換,并使用VHDL語言設計了該有限狀態機,并使用QuartusⅡ開發軟件對該狀態機進行了仿真和驗證,仿真結果表明該程序可以正確描述主狀態機的狀態轉換,該有限狀態機使用"單進程"式描述,與"三進程"和"雙進程"式相比程序簡潔明了并且能夠有效地節省資源,減少功耗,提高系統的穩定性。

-

仿真

+關注

關注

51文章

4241瀏覽量

135332 -

微處理器

+關注

關注

11文章

2371瀏覽量

83863 -

總線

+關注

關注

10文章

2952瀏覽量

89373 -

vhdl

+關注

關注

30文章

819瀏覽量

129581

發布評論請先 登錄

fsm有限狀態機pdf

有限狀態機的硬件描述語言設計方法

有限狀態機的建模與優化設計

VHDL有限狀態機設計-ST

初學者對有限狀態機(FSM)的設計的認識

通過采用VHDL語言進行MTM總線主模塊有限狀態機的設計與仿真驗證

通過采用VHDL語言進行MTM總線主模塊有限狀態機的設計與仿真驗證

評論