與傳統模擬示波器相比.數字存儲示波器不僅具有可存儲波形、體積小、功耗低,使用方便等優點,而且還具有強大的信號實時處理分析功能。在電子測量領域,數字存儲示波器正在逐漸取代模擬示波器。但目前我國使用高性能數字存儲示波器主要依靠國外產品,而且價格昂貴。因此研究數字存儲示波器具有重要價值。借于此,提出了一種簡易數字存儲示波器的設計方案,經測試,性能優良。

2數字存儲示波器基本工作原理

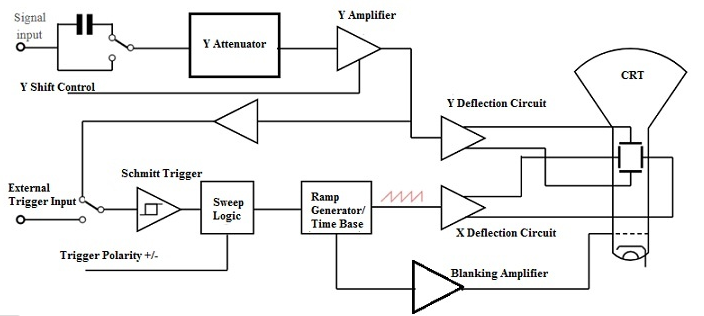

數字存儲示波器與模擬示波器不同在于信號進入示波器后立刻通過高速A/D轉換器將模擬信號前端快速采樣,存儲其數字化信號。并利用數字信號處理技術對所存儲的數據進行實時快速處理,得到信號的波形及其參數,并由示波器顯示,從而實現模擬示波器功能,而且測量精度高。還可存儲信號,因而,數字存儲示波器可以存儲和調用顯示特定時刻信號。

3系統分析論證

3.1A/D實時采樣

根據奈奎斯特采樣定理,采樣速率必須高于2倍的信號最高頻率分量。對于正弦信號,一周期內應有2個采樣點。為了不失真恢復被測信號,通常一周期內需要采樣8個點以上。為了配合高速模數轉換器,采用FPGA控制M/D轉換器的采樣速率,以實現高速實時采樣。實時采樣可以實現整個頻段的全速采樣,本系統設計選用ADI公司的12位高速A/D轉換器AD9220,其最高采樣速率可達10MHz。

3.2雙蹤顯示

本系統設計的雙蹤顯示模塊是以高速切換模擬開關選通兩路信號進入采樣電路,兩路波形存儲在同一個存儲器的奇、偶地址位。雙蹤顯示時,先掃描奇地址數據位,再掃描偶地址數據位。采用模擬開關代替一個模數轉換器,避免兩片高速A/D轉換器相互干擾,降低系統調試難度,并且實現系統功能。

3.3觸發方式

采用FPGA內部軟件觸發方式,通過軟件設置觸發電平,所設置的施密特觸發器參數易于修改,從而抑制比較器產生的毛刺。當采樣值大于觸發電平,則產生一次觸發。該方式充分利用了FPGA的資源,減少外圍電路,消除硬件毛刺產生的干擾,易于調整觸發電壓。

3.4波形顯示位置的調節

3.4.1行掃描調節

通過控制FPGA內部雙口RAM(1KB)的起始地址的偏移量確定來控制波形的移動。其具體方法是將滑動變阻器R上的電平通過模數轉換器轉換為數字信號傳輸給FPGA,再與初始電平數字信號(顯示位置復位時,滑動變阻器R的電平采樣值)相比較決定起始地址ADR0的偏移量。該方法可易于實現波形滿屏和自動顯示功能。

3.4.2列掃描調節

MAXl97采樣A、B通道的Position電位器值,所得采樣值經FPGA送至16位串行D/A轉換器,MAX542產生直流電平,該直流電平與列掃描波形相加送至模擬示波器顯示,實現波形上下移動。為分離A、B通道,在讀A通道波形數據時,FPGA必須將PositionA電位器的值送至D/A轉換器;而在讀B通道波形數據時,也必須將PositionB電位器的值送至D/A轉換器,這樣可在調節某一電位器時,實現相應通道波形上下移動。

3.5波形數據存儲

數字示波器存儲波形數據可采用外接的雙口RAM或通用靜態RAM,同時FPGA可控制RAM的地址線,從而實現波形數據的存儲。雙口RAM可同時進行讀寫操作,由于本系統設計采用FPGA,因此可充分利用FPGA的邏輯陣列和嵌入式陣列,可將雙口RAM寫入FPGA內部,從而無需外接RAM,減少硬件電路,提高簡易數字示波器的可靠性。

4系統設計方案

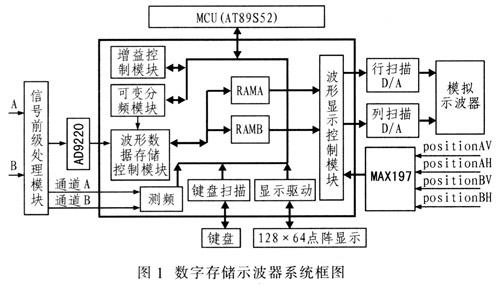

本系統設計框圖如圖1所示。整個系統是以FPGA為核心,包括前端模擬信號處理模塊、單片機模塊、顯示模塊和鍵盤輸入模塊。而信號的前級處理模塊又包括射級跟隨器、程控放大電路、整形電路。A、B通道的信號經前級處理變為O~4V,AD9220對其采樣。波形存儲控制模塊將其采樣數據寫入FPGA內部RAM,再由波形顯示控制模塊進行顯示。FPGA通過編程設置實現測頻、鍵盤掃描、顯示驅動、波形存儲控制等功能。單片機AT89S52控制整個系統鍵盤和點陣液晶模塊實現人機交互。通過面板按鍵可方便調整波形顯示方式。

5硬件電路設計

5.1程控放大電路

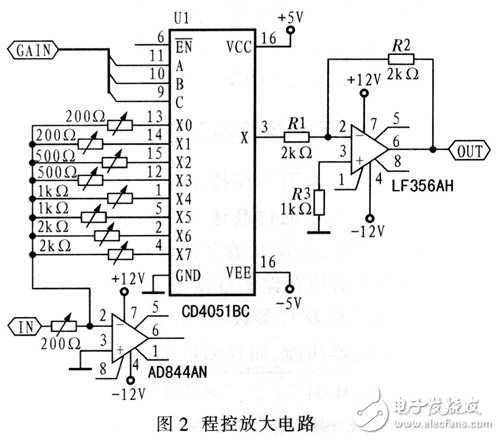

采用模擬開關CD4051、寬帶運算放大器AD844及精密電位器實現10mV/div~2V/div的多檔垂直分辨率。FPGA含有通道選擇寄存器模塊,通過單片機寫入通道號控制模擬開關以選通不同的反饋電阻,實現不同放大倍數,將信號調理在滿足AD9220的0~4V的范圍內,具體電路如圖2所示。

5.2數據采集模塊

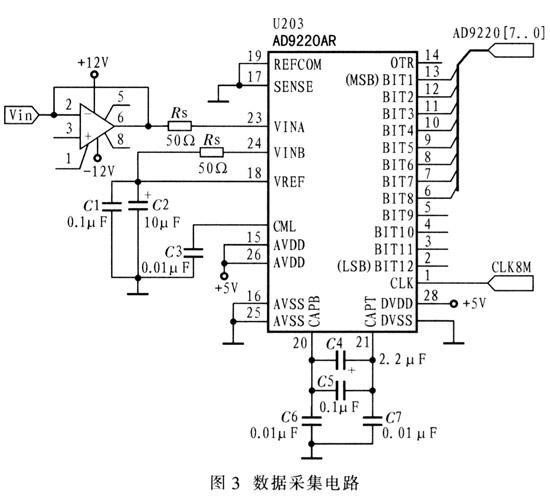

本系統設計采用ADI公司的高速模數轉換器AD9220實現波形信號的采集,AD9220最高采樣速率可達10MHz,采用外部晶體振蕩器8MHz,FPGA內部通過采樣實現波形存儲。AD9220有直流耦合和交流耦合兩種輸入方式。本系統設計采用直流耦合,0~5V的輸入方式。采用內部2.5V參考電壓。由于系統垂直分辨率只需255級,故采用AD9220的高8位。數據采集電路如圖3所示。

5.3FPGA設計

系統采用VerilogHDL語言,在QuartusII軟件下對FPGA進行邏輯電路的描述編程,可靈活實現系統所需電路和控制模塊。

5.3.1觸發模塊

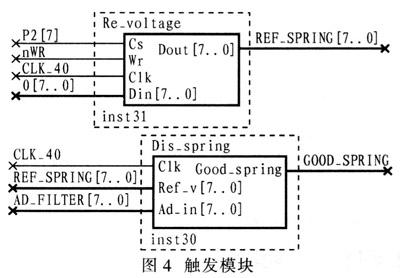

單片機先向FPGA模塊寫入設置的觸發電壓,FPGA內部相比較后,當采樣值大于該觸發電壓時,則產生一次觸發。圖4為觸發模塊。

5.3.2程控放大控制模塊

單片機首先以100mv/div的檔位對信號采樣,通過比較與該信號最近的模擬開關的通道號,然后寫入控制字,產生相應通道號,實現垂直分辨率的調整。

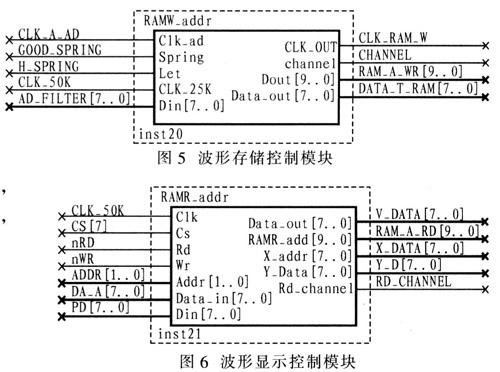

5.3.3波形存儲控制模塊

該模塊為RAM模塊的寫地址累加器,可控制波形的存儲。H_sering為單次和多次觸發控制引腳,當為高電平時,單次觸發,停止向RAM寫入數據,所顯示波形為存儲波形;為低電平時,多次觸發,當檢測到一次觸發時,即向RAM寫一次數據,共lK個點,并在寫操作時屏蔽觸發。寫地址先寫奇地址,存入通道一采樣后的波形數據,后寫偶地址,存入通道二采樣后的波形數據。如果連續多次檢測不到觸發時,向RAM中寫入全0,顯示一條直線,即實現自動捕捉功能。波形存儲控制模塊如圖5所示。

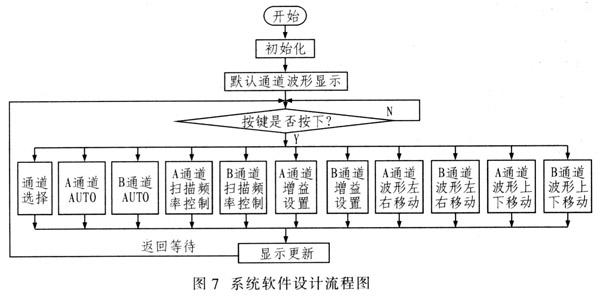

5.3.4波形顯示控制模塊

該模塊為讀地址累加器,從RAM中讀取數據,并產生行掃描和列掃描數據。通過單片機寫入累加器基地址,改變讀取數據的起始位,實現波形的平移。該模塊還可計算波形的峰峰值、平均值,單片機可直接讀回數值。波形顯示控制模塊如圖6所示。

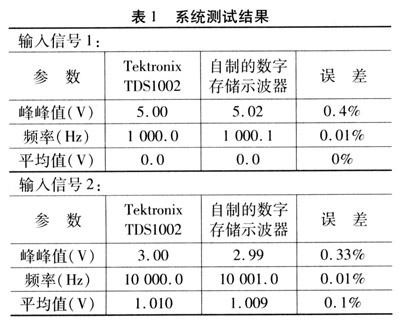

6系統軟件設計

系統軟件設計實現人機交互、信息提示、系統啟動與復位等功能。首先系統初始化,顯示默認通道波形,再等待按鍵按下。當按鍵按下后,完成相應功能,顯示相應波形,然后循環等待。系統軟件設計流程如圖7所示。

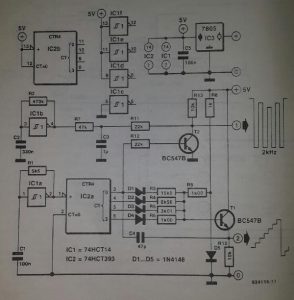

7測試結果

使用自制的數字存儲示波器和tektronixTDSl002型數字示波器測量輸入信號,其中部分測量數據如表1所列。

通過對比測試和結果分析,各種輸入信號在自制數字存儲示波器上可精確顯示波形,并且實現波形的雙蹤顯示及波形水平、垂直平移,頻率、平均值、峰峰值的測量,誤差小,達到一定的精度要求。

8結語

本系統設計采用單片機作為核心控制器,充分利用FPGA的可編程邏輯功能,完成相關電路設計。軟硬件有機結合實現簡易數字存儲示波器的設計,系統總體功能完善,穩定性高,使用方便。

-

轉換器

+關注

關注

27文章

8949瀏覽量

150714 -

示波器

+關注

關注

113文章

6534瀏覽量

188174 -

存儲器

+關注

關注

38文章

7633瀏覽量

166390

發布評論請先 登錄

嵌入式系統軟硬件基礎知識大全

【ZDS2024 Plus示波器申請】機械手軟硬件調試

數字存儲示波器的工作原理及軟硬件系統的設計

嵌入式軟硬件系統的工作原理是什么

單片機測控系統的軟硬件平臺技術

基于EDA 的嵌入式系統軟硬件劃分方法

軟硬件協同設計是系統芯片的基礎設計方法學

為什么要從“軟硬件協同”走向“軟硬件融合”?

數字存儲示波器的工作原理

軟硬件融合的概念和內涵

基于MSP430F13X的溫度采集儀的工作原理及軟硬件設計方法

數字存儲示波器的工作原理及軟硬件系統的設計

數字存儲示波器的工作原理及軟硬件系統的設計

評論