隨著社會的發展,無線通信已成為日益重要的信息傳遞方式。伴隨著深亞微米CMOS工藝的成熟,采用藍牙技術接收發送射頻電路已可實現單片集成。然而,一個好的射頻接收發送芯片必須有盡可能低的成本和優良的性能,后者通常需要通過合適的測試方法來檢測和保證。在傳統的設計流程中,往往在芯片設計接近尾聲的時候才會考慮到可測性設計。再加上射頻電路本身難以測試的特點,不佳的可測性設計不但會大大增加后期芯片測試驗證的難度,還會使得芯片的整體制作成本顯著升高。為了能有效控制測試成本,必須在設計開始階段就考慮系統的可測性,甚至在確定系統架構和規范之前,就應將各種可測性問題、測試設備的成本以及測試所需要的時間考慮在內。通過對系統架構和規范的調整,合理的可測性設計可以內嵌于系統之中,這樣不僅可以有效控制因測試而導致的硬件成本增加,而且還大大提升了芯片的可測性。

本文介紹了一種基于藍牙射頻電路可測試性設計的8位逐次逼近型ADC,該電路結構簡單緊湊,功耗較低,專門針對將可測性設計嵌入系統架構而設計。通過ADC可以方便地檢測藍牙電路中各模塊的直流工作點,在輸入中加以簡單的激勵信號,還可以對部分模塊的性能參數予以檢測。該方法使得芯片的可測性問題變得易于實現,并且只是有限地增加了芯片的整體硬件成本。

ADC的體系結構

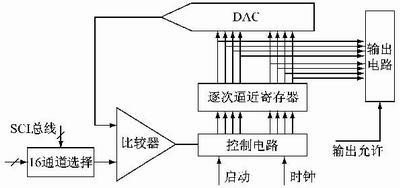

針對可測性的設計,本文中的ADC體系結構示意圖如圖1所示。

圖1 ADC體系結構

整個電路工作原理比較簡單:由數字電路組成的逐次逼近寄存器和控制電路將DAC每位依次置1”,DAC的輸出值與輸入模擬電壓通過比較器進行比較,并確定“1”是否保留。當8位完全確定后,就可以得到一個最逼近輸入模擬電壓的數字值。與傳統的逐次逼近型ADC的不同之處在于,為了能對多路信號進行測試,用一個十六選一的選擇器代替原本的采樣保持電路,在系統SCI總線控制下,可以選擇不同通道的信號進行測試。

rail-to-rail輸入比較器和R-2R網絡DAC的設計

比較器設計

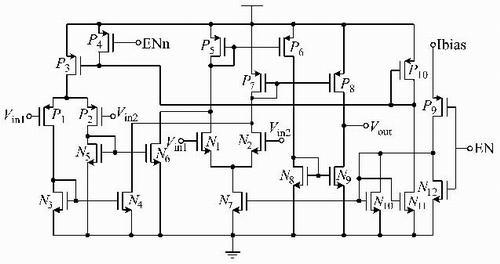

由于測試信號本身幅度的關系,ADC的動態輸入范圍必須在0~3.3V,為此,在本設計中對比較器采用了rail-to-rail的輸入設計。圖2是比較器的電路圖。

圖2 rail-to-rail輸入比較器

該比較器電路由22個MOS晶體管構成。電路采用折疊對稱結構,P9、N12作為開關控制電路的偏置電流。對于PMOS差分對,其共模輸入范圍VCM可表示為:

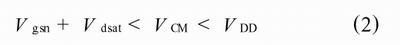

式中VCM為共模輸入電平,VDD為電源電壓,Vdsat為差分輸入級中源漏飽和壓降,Vgsp為PMOS輸入管的柵源電壓。同理,對于NMOS差分對,其共模輸入范圍可表示為:

式中Vgsn為NMOS輸入管的柵源電壓。將上述PMOS和NMOS差分對并聯起來,則整個電路的共模輸入范圍可寫成:

從而實現了輸入級的rail-to-rail,工作電壓的最小值為:

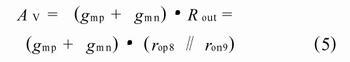

當共模輸入電平接近VDD或0時,只有NMOS或PMOS差分輸入對處于放大狀態;當共模輸入電平處于中間狀態時,PMOS和NMOS差分對都處于放大狀態。因此,比較器的增益可以表示成:

N管和P管跨導的疊加,可以大大提高增益,從而使得比較器的精度也顯著提高。但是當共模輸入電平從0到VDD變化時,總的等效跨導gmeff變化很大,會使電路的單位增益帶寬受到一定影響。

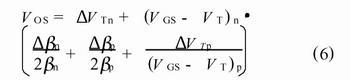

比較器的分辨率還與差分輸入對的失調電壓有很大關系,在現在的CMOS工藝中,一般為幾~幾十毫伏,這會嚴重影響比較器的精度。一般失調可分為系統失調和隨機失調,前者可以通過采用合適的結構來消除;后者由于受工藝條件限制,往往較難避免。以N管差分對為例,隨機失調可近似表示如下:

通常人們使用數字校正,自動補償等方法來減少失調,但這樣會引入額外的硬件消耗和功耗。為了降低成本,便于實現,本設計主要通過對管子的優化設計來減少隨機失調。在式(6)中(VGS-VT)n、(VGS-VT)p分別為N管和P管的有效偏置,ΔVTn、Δβn和ΔβP都跟√WL成反比。顯然采用較大的管子面積,較小的輸入管(VGS-VT)和較大的負載管(VGS-VT)可以有效減少失調。因此,在設計中,差分輸入對都取了較大的尺寸,并通過設置合適的工作點,使得輸入管的(VGS-VT)保持在0.2V左右。

在版圖設計時,則采用幾何共中心的交叉結構,使得差分輸入對盡可能對稱,并且添加了Dummy管,使管子的周邊環境保持相同。此外,在比較器的輸出端還增加了兩個反向器,使得高低電平分別趨向于VDD和0仿真結果顯示,僅用一級放大的比較器增益可達52dB,最小分辨率達4mV,足以滿足藍牙射頻電路可測性設計的要求。

DAC設計

為了使電路盡可能的簡單,本設計中DAC采用經典的R-2R梯形網絡結構。由于整個ADC內嵌入藍牙接收發送系統,電路的參考電壓可由公共通道中的帶隙基準源統一提供,這樣既減少了ADC的功耗,又保證了精度.R-2R網絡的最大缺點是由于工藝制作中存在的偏差,諸如雜質擴散,溫度漂移等問題會使得電阻的阻值產生一定誤差。通常多晶硅電阻可以做到較為精確,但由于在本工藝中該方塊電阻只有2歐姆左右,會使得面積太大。而阱電阻雖然方塊電阻很大,但精度較差。因此,在考慮面積和性能折衷的情況下,我們選用受工藝因素影響相對較小的P型擴散電阻,其方塊電阻為153歐姆。單位電阻條寬取為5μm.該電阻受擴散腐蝕引起的誤差可由下式計算:

式中etch,vc1和vc2都是工藝提供的參數。通過計算可知由工藝產生的電阻值絕對誤差雖然有15%左右,但相對1μm或2μm的工藝,采用TSMC0.35μm的工藝,在5μm條寬的情況下,可以將相對誤差做到±0.4%以內。同時,在版圖設計時采用單位電阻及增加Dummy填充電阻的方法,可以有效地提高R-2R網絡中電阻的匹配性,從而滿足8位的精度要求。

ADC在藍牙射頻電路中的可測性應用

測試芯片是否符合設計規范有兩種方法:即基于構成系統的獨立模塊級的測試和系統級的測試。本設計綜合兩者優點,將測試內嵌于接發器架構中,通過一個結構簡單,實現容易的ADC,就可完成芯片部分功能的測試。

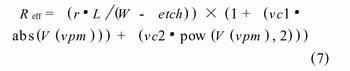

ADC的應用有兩方面:第一用于檢測各模塊的直流工作點。在電路工作時,高頻信號的干擾及其他因素會影響帶隙基準源的準確性。一旦偏置電壓或偏置電流不準,會直接導致各模塊不能正常工作。通過ADC的多通道就能直接檢測各模塊的直流工作點。第二用于測試一些在高頻情況下無法直接測得的性能參數,如信號幅度、噪聲等。通過輸入簡單的激勵信號,可以將被測參數轉為直流電平,經模數轉化后就可方便讀出。例如可以用ADC檢測藍牙射頻接收通道中的帶通濾波器是否符合圖3所示的藍牙協議定義的濾波器的部分指標。將圖中特殊點的信號幅度用直流電平表示,通過ADC的模數轉換,就可以方便地觀測到不同點的衰減是否符合要求。但是,在2MHz和3MHz頻率時,信號幅度很小且很接近,給觀測帶來困難。這種情況可以通過調節自動增益控制,適當增加增益,使信號幅度增大且易于區分,但要求不能使ADC飽和。

圖3濾波器性能

測試結果

圖4是ADC的芯片照片,該芯片由0.35μm標準CMOS工藝制造,芯片面積是0.5mm×0.3mm.

圖4ADC芯片照片

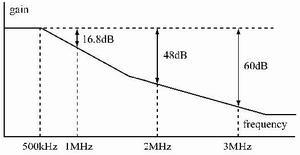

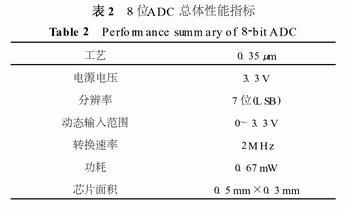

表1給出了藍牙射頻電路中帶隙基準源,帶通濾波器以及低噪放的理想直流工作電壓與經ADC測試到的值,從中可以看到ADC的精度基本達到要求。表2給出了ADC的總體性能指標。

結論

本文設計了基于藍牙射頻電路可測性設計的8位逐次逼近型ADC.芯片測試結果顯示,在3.3V工作電壓下,ADC的分辨率可達7位。在設計中,輸入級采用rail-to-rail結構,利用PMOS差分對和NMOS差分對并聯的方法有效提高了電路的共模輸入范圍。通過對比較器電路和版圖的優化設計使失調影響減到最小,大大提高了精度。針對可測性設計的要求,整個電路結構簡單,易于實現,與同種功能ADC相比,芯片面積較小,僅0.5mm×0.3mm,功耗也較低。該ADC可以方便地內嵌入藍牙射頻電路的體系結構中,以用于檢測各模塊電路的部分功能與性能,這樣的可測性設計,在使射頻電路變得易于測試的同時,也大大減少了測試成本。由于在版圖設計中較好地采用了隔離技術,電路在2.4GHz的高頻環境下正常工作,表現出了良好的抗干擾能力。另一方面,測試結果顯示ADC實際精度為7位,第8位在測試時跳動不確定,造成該結果的原因可能是由于參考電壓對地有一定波動并且比較器的輸入存在失調。在今后的工作中,將采用比較器的輸入失調電壓補償等技術,使得電路和版圖進一步優化,從而使結果更理想。同時,怎樣更好地利用ADC進行藍牙射頻電路的可測性研究也將成為下一步研究的工作.

-

芯片

+關注

關注

459文章

52253瀏覽量

436951 -

射頻

+關注

關注

106文章

5733瀏覽量

169845 -

藍牙

+關注

關注

116文章

6042瀏覽量

173288

發布評論請先 登錄

CSR BC05立體聲藍牙模塊

如何利用DSP Builder設計一種適合于軟件無線電使用的可控數字調制器

這種高密度工藝特別適合于 最小化導通電阻

如何設計一款適合于果園應用的激光雷達

適合于嵌入式系統的C語言單元測試框架是什么

基于藍牙的遠程控制方法的實現

NJR開發GaAs MMIC NJG1139UA2,適合于便

適合于溫室控制系統的CAN總線應用層協議開發

適合于片上PWM模塊的一種易于實現中心對齊SVPWM的方法詳細概述

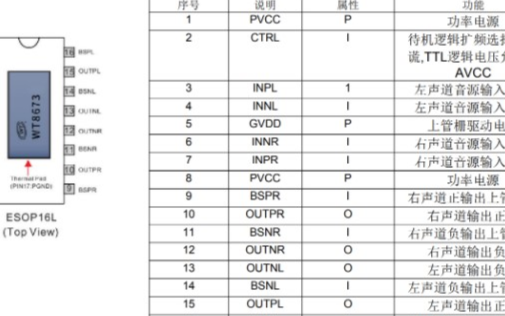

適合于藍牙音響的功放芯片WT8673介紹

基于ADC適合于藍牙射頻電路的測試方法

基于ADC適合于藍牙射頻電路的測試方法

評論