同步時序設計時一下事項應值得注意:

異步時鐘域的數據轉換。

組合邏輯電路的設計方法。

同步時序電路的時鐘設計。

同步時序電路的延遲。

同步時序電路的延遲最常用的設計方法是用分頻或者倍頻的時鐘或者同步計數器完成所需的延遲,對比較大的和特殊定時要求的延時,一般用高速時鐘產生一個計數器,根據計數產生延遲;對于比較小的延遲,可以用D觸發器打一下,這樣不僅可以使信號延時了一個時鐘周期,而且完成了信號與時鐘的初次同步。在輸入信號采樣和增加時序約束余量中使用。

另外,還有用行為級方法描述延遲,如“#5 a<=4’0101;”這種常用于仿真測試激勵,但是在電路綜合時會被忽略,并不能起到延遲作用。

Verilog 定義的reg型,不一定綜合成寄存器。在Verilog代碼中最常用的兩種數據類型是wire和reg型,一般來說,wire型指定的數據和網線通過組合邏輯實現,而reg型指定的數據不一定就是用寄存器實現。

-

信號

+關注

關注

11文章

2842瀏覽量

77887 -

計數器

+關注

關注

32文章

2284瀏覽量

96025 -

同步時序

+關注

關注

0文章

12瀏覽量

7947

原文標題:同步時序設計時應值得注意的事項

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

兩線制接近開關的幾大要素

請問電視機起振的幾大要素什么?電壓流程是什么順序呢?

哪幾大要點是眼部除皺后必須注意的呢

智能消防巡檢柜應用的幾大要求

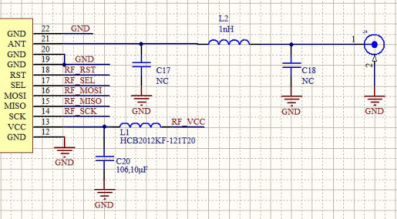

LoRa天線電路設計四大要點

成功解決FPGA設計時序問題的三大要點

同步時序設計時應注意的幾大要點

同步時序設計時應注意的幾大要點

評論