SiFive發布低功耗32位內核 E2系列,包含SiFive E20和E21,適用于低功耗應用。注意目前發布的是內核,不是芯片。

RISC-V是一個開放的指令集架構(ISA),最初由加州大學伯克利分校的計算機科學系開發。它基于流行的精簡指令集(RISC),和ARM、MIPS和其它常見的商業處理器架構一樣。

目前已有超過100個機構成為了RISC-V組織的成員,包括三星/高通/谷歌/NXP/蘋果/特斯拉/晶心科技等

SiFive是基于RISC-V指令集架構提供快速開發式處理器核心IP的領先供應商,核心團隊就是由RISC-V研發團隊所創立。通過開放式架構處理器核心及自主式開發基于RISC-V架構芯片來幫助SoC設計。

SiFive發布低功耗32位內核 E2系列,包含SiFive E20和E21,適用于低功耗應用。注意目前發布的是內核,不是芯片。

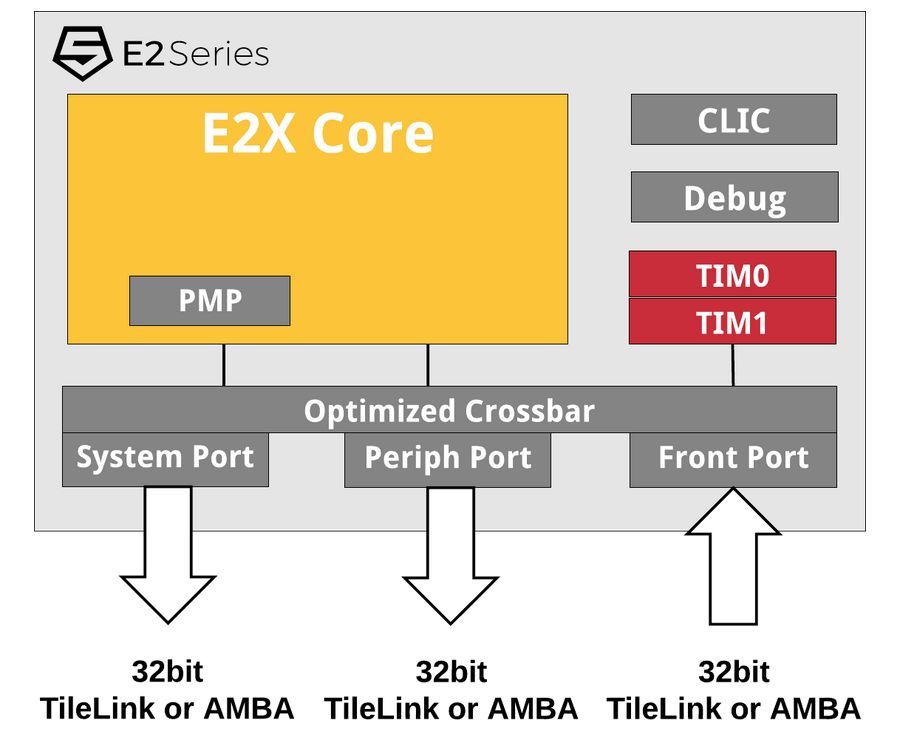

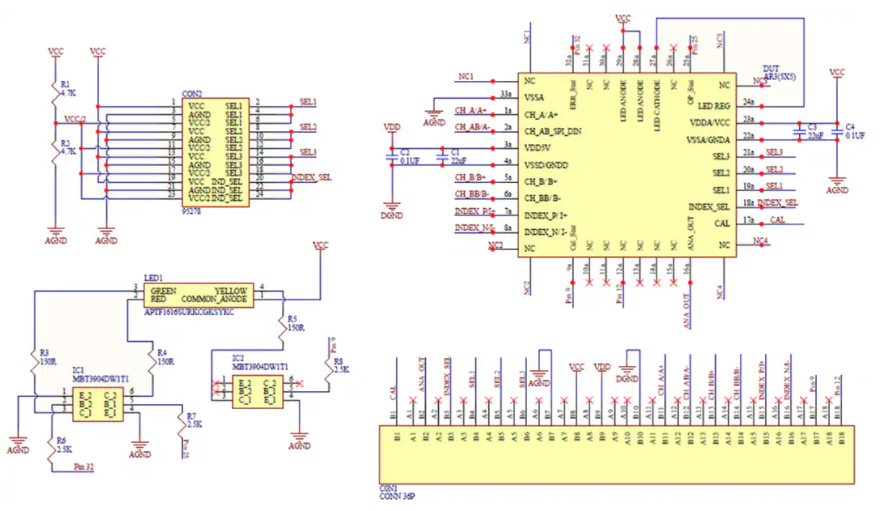

E2系列框圖如下:

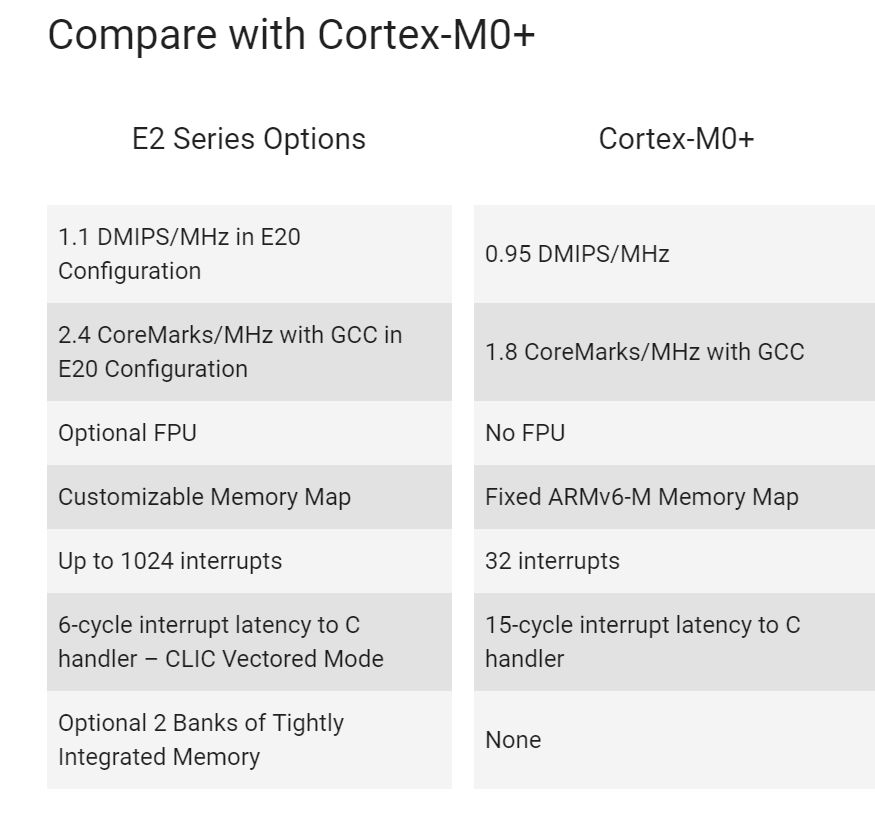

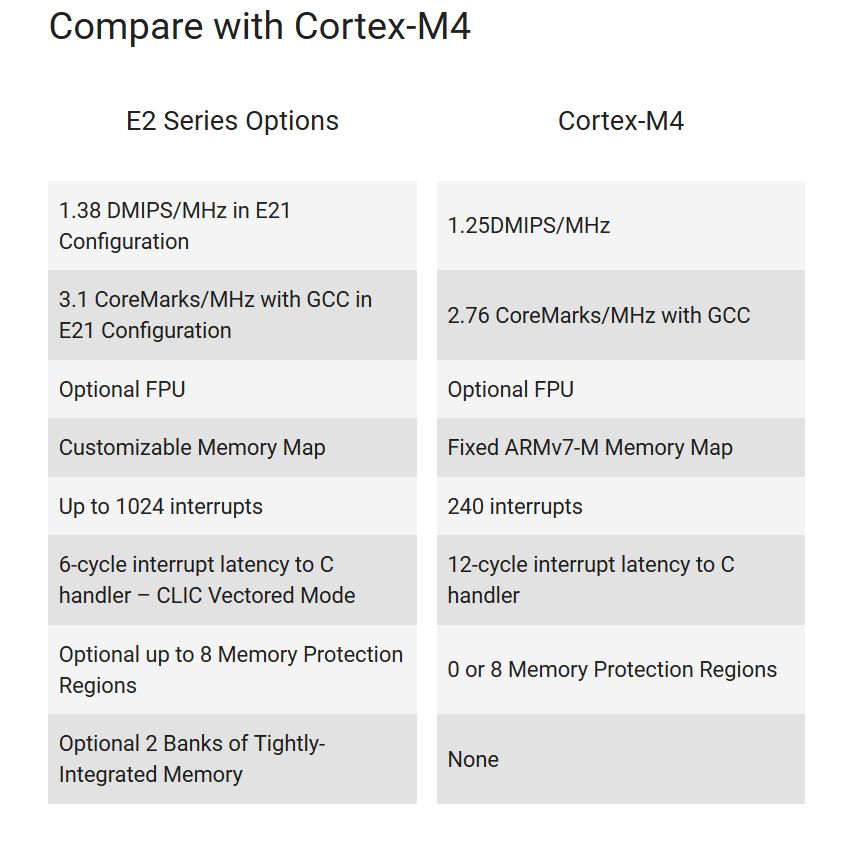

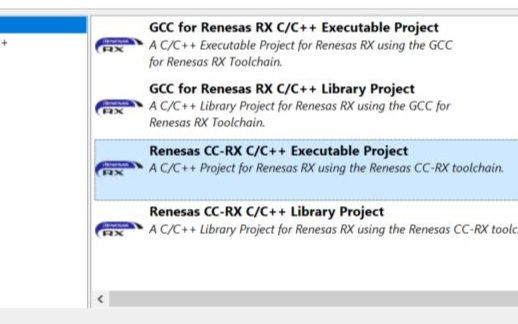

同時還給出了E20和Cortex-M0+、E21和Cortex-M4的對比

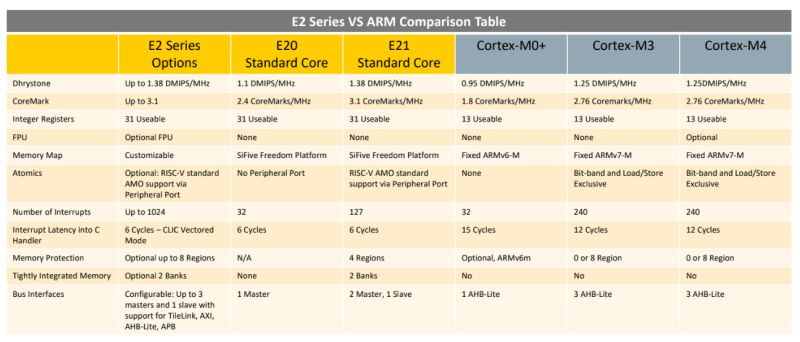

E2系列和ARM Coretex-M對比表

你怎么看E2系列內核?

-

處理器

+關注

關注

68文章

19813瀏覽量

233619 -

RISC-V

+關注

關注

46文章

2502瀏覽量

48294

原文標題:SiFive發布低功耗32位內核 E2系列,欲PK ARM Cortex-M

文章出處:【微信號:eedesigner,微信公眾號:eeDesigner】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Broadcom HEDS-9930 (E2/E2L) 評估板與AEDR_9930E2光學編碼器數據手冊

新品 | RA0系列MCU喜添新成員RA0E2,0.25uA超低功耗待機,支持5v、125c

e2studio和Keil簡介及如何安裝e2studio開發環境

RISC-V 領軍企業 SiFive 成立中國分公司,中文名稱定為“芯伍科技”

微星發布MAG 325CQRXF E2游戲顯示器

SiFive發布MX系列高性能AI加速器IP

RA0E1 MCU低功耗演示例程

SiFive發布低功耗32位內核 E2系列,包含SiFive E20和E21

SiFive發布低功耗32位內核 E2系列,包含SiFive E20和E21

評論