ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)領(lǐng)導(dǎo)廠商智原科技(Faraday Technology Corporation)宣布推出可支持第三至第五代DDR/LPDDR的通用物理層IP,適用于聯(lián)電(UMC)22ULP與14FFC FinFET工藝。智原持續(xù)致力于提供優(yōu)化的自有IP解決方案,協(xié)助ASIC客戶提升開發(fā)效率與產(chǎn)品成本競(jìng)爭(zhēng)力。

智原的DDR/LPDDR物理層IP解決方案,已廣泛應(yīng)用在多項(xiàng)SoC設(shè)計(jì)案中,已通過(guò)硅驗(yàn)證及單芯片系統(tǒng)整合驗(yàn)證,其高度穩(wěn)定性與兼容性完全符合JEDEC規(guī)范,可確保與內(nèi)存芯片間資傳輸效能,同時(shí)也優(yōu)化了功耗表現(xiàn)。22ULP PHY支持低至0.8V的操作電壓,特別適用在行動(dòng)裝置、5G與物聯(lián)網(wǎng)等功耗敏感的應(yīng)用。14nm物理層支持DDR5/LPDDR5,提供高達(dá)6400Mbps的傳輸速率,并內(nèi)建參數(shù)調(diào)整機(jī)制、阻抗匹配校正與DFE等功能,確保訊號(hào)傳輸?shù)馁|(zhì)量與穩(wěn)定性。

智原科技營(yíng)運(yùn)長(zhǎng)林世欽表示:"隨著SoC設(shè)計(jì)日益復(fù)雜,市場(chǎng)對(duì)高效能與低功耗的內(nèi)存解決方案需求不斷提升。智原提供涵蓋控制電路、物理層及子系統(tǒng)整合服務(wù)的完整DDR/LPDDR IP解決方案,協(xié)助客戶加速設(shè)計(jì)時(shí)程、降低開發(fā)風(fēng)險(xiǎn),并以高質(zhì)量且可靠的內(nèi)存子系統(tǒng),滿足先進(jìn)應(yīng)用的設(shè)計(jì)需求。"

關(guān)于智原科技

智原科技(Faraday Technology Corporation, TWSE: 3035)以提供造福人類、支持永續(xù)發(fā)展的芯片為使命,發(fā)展完整的ASIC解決方案,包含3D先進(jìn)封裝、Arm Neoverse CSS設(shè)計(jì)、FPGA-Go-ASIC與芯片實(shí)體設(shè)計(jì)服務(wù)。同時(shí),智原擁有豐富的硅智財(cái)數(shù)據(jù)庫(kù),涵蓋I/O、Cell Library 、 Memory Compiler 、 Arm-compliant CPUs 、DDR/LPDDR、MIPI D-PHY、V-by-One、USB、Ethernet、SATA、PCIe、及可程序設(shè)計(jì)高速SerDes等數(shù)百個(gè)IP。

-

asic

+關(guān)注

關(guān)注

34文章

1250瀏覽量

122538 -

DDR

+關(guān)注

關(guān)注

11文章

733瀏覽量

66925 -

物理層

+關(guān)注

關(guān)注

1文章

156瀏覽量

35094 -

智原科技

+關(guān)注

關(guān)注

0文章

24瀏覽量

11313

原文標(biāo)題:智原推出DDR/LPDDR通用物理層IP解決方案 適用于聯(lián)電22ULP與14FFC工藝

文章出處:【微信號(hào):faradaytech,微信公眾號(hào):智原科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Cadence推出LPDDR6/5X 14.4Gbps內(nèi)存IP系統(tǒng)解決方案

芯動(dòng)科技獨(dú)家推出28nm/22nm LPDDR5/4 IP

智原科技推出最新SerDes IP持續(xù)布局聯(lián)電22納米IP解決方案

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內(nèi)存IP系統(tǒng)解決方案

燦芯半導(dǎo)體推出DDR3/4和LPDDR3/4 Combo IP

是德科技正式發(fā)布LPDDR6設(shè)計(jì)與測(cè)試解決方案

是德科技推出LPDDR6設(shè)計(jì)和測(cè)試解決方案

MultiGABSE-AU物理層PMA子層及PMD子層的相關(guān)機(jī)制

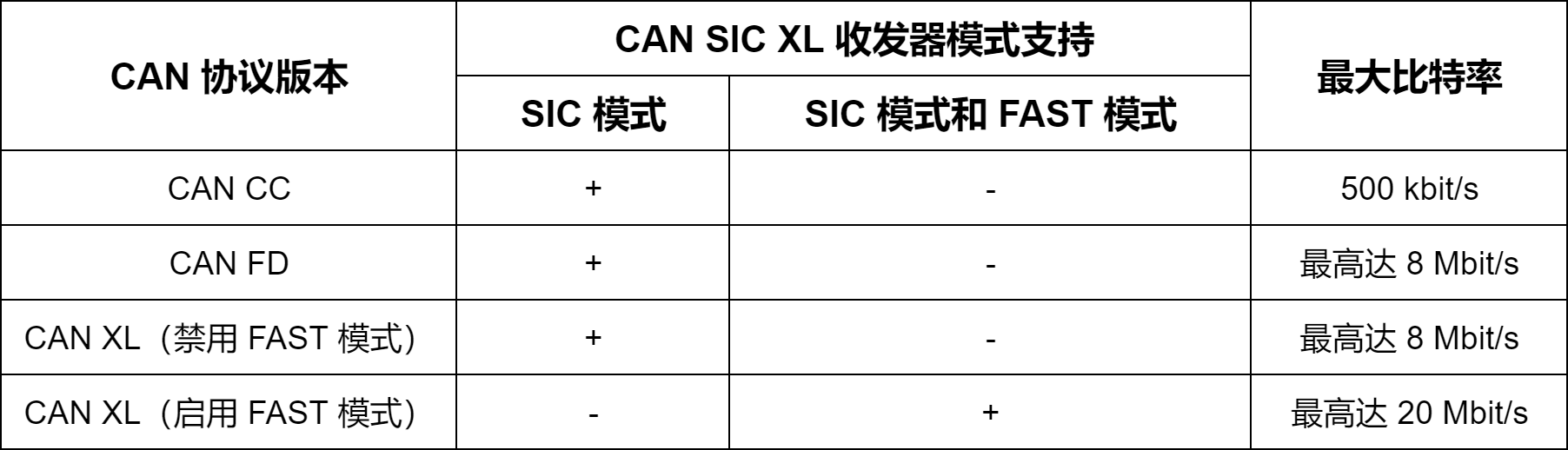

CAN XL物理層揭秘(下):物理層組合與兼容性

SD3.0物理層規(guī)格書中文版

IEEE 1394物理層用晶體的選擇和規(guī)范

智原科技推出DDR/LPDDR通用物理層IP解決方案

智原科技推出DDR/LPDDR通用物理層IP解決方案

評(píng)論