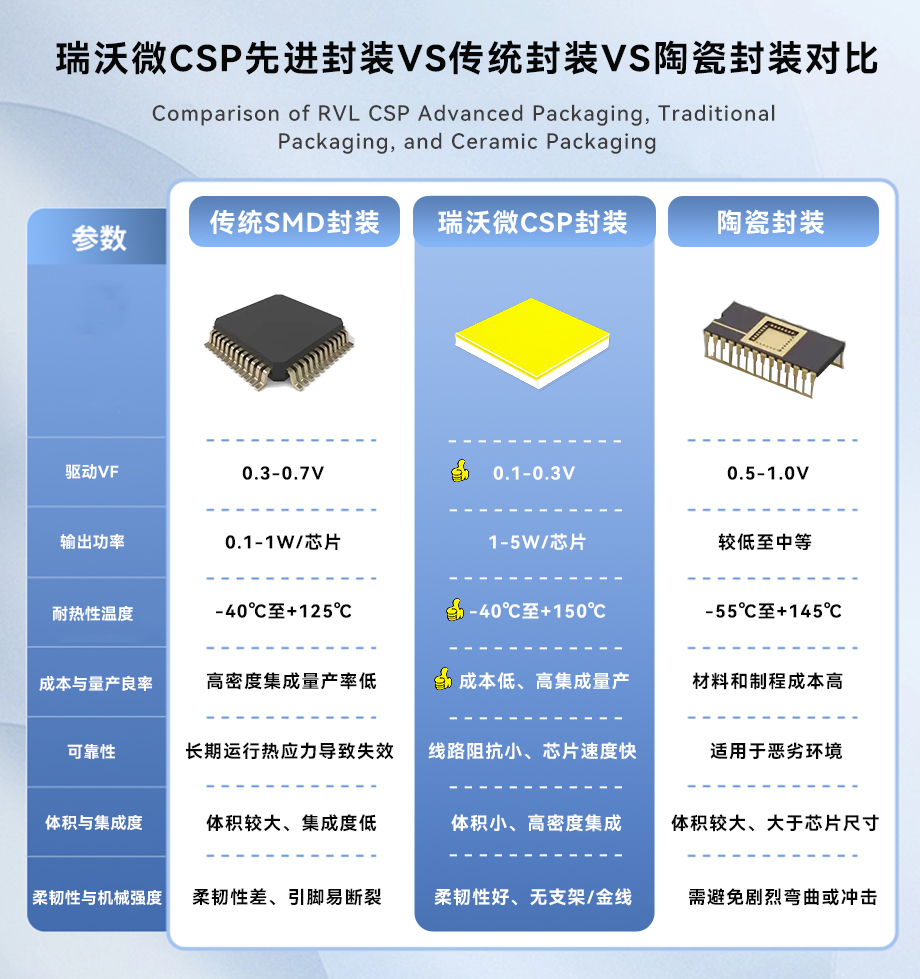

在半導體產業的宏大版圖中,封裝技術作為連接芯片與應用終端的關鍵紐帶,其每一次的革新都推動著電子產品性能與形態的巨大飛躍。當下,瑞沃微 的CSP先進封裝技術在提升良率和量產成本方面展現出了突破傳統技術的絕對優勢,使其在眾多場景中漸成 “前朝遺老”。

傳統封裝技術,如 BGA(球柵陣列封裝)、TSOP(薄小外形封裝)等,在長期發展中形成了成熟體系,但隨著電子產品向小型化、高性能、高可靠性方向邁進,弊端日益凸顯。以 BGA 為例,其多層結構復雜,在制造過程中易因焊球焊接缺陷、芯片與基板熱膨脹系數不匹配等問題,導致封裝良率受限,一般良率徘徊在 80% - 85%。在 5G 基站、高性能計算等對芯片可靠性要求極高的領域,傳統封裝技術高溫下熱阻大、信號傳輸延遲明顯等不足,更是嚴重制約產品性能與穩定性,難以滿足需求。

而瑞沃微 CSP 技術則帶來了新突破和新的路線改變。從結構設計上,瑞沃微CSP先進封裝打破了傳統封裝的繁復框架,將芯片與 PCB 的連接范式重構,極大簡化了內部結構。通過先進的倒裝芯片技術,瑞沃微 CSP 減少了焊點數量,降低了焊接缺陷產生概率,有效提升了封裝良率。在實際生產中,瑞沃微 SMD0201 系列 CSP 產品通過持續優化工藝,良率成功超越傳統封裝技術水平。在性能表現上,瑞沃微 CSP 優勢顯著。其熱阻可低至 4.2℃/W,僅為傳統 QFP(四方扁平封裝)封裝的 36%,出色的散熱能力減少了因芯片過熱導致的性能衰減與失效風險,進一步保障了產品可靠性與良率。在高集成度方面,瑞沃微 CSP 憑借 5D 模塊化設計,實現了三維堆疊與異構集成,單芯片 I/O 密度突破 5000 個 /mm2,單位面積算力密度提升 3 倍以上,在有限空間內集成更多功能,且未因復雜集成降低良率。

在成本效益層面,瑞沃微 CSP 同樣表現卓越。一方面,高良率意味著更低的生產成本,減少了因不良品產生的資源浪費與返工成本;另一方面,其小型化、高性能特點,使得電子產品在設計上可減少外圍元件數量,精簡 PCB 布線,從而降低整體物料與制造成本。在汽車電子領域,瑞沃微 CSP 封裝的芯片在滿足汽車 15 年設計壽命要求的同時,憑借高良率與成本優勢,為車企帶來顯著經濟效益,正逐步取代傳統封裝芯片。

瑞沃微 CSP 技術憑借在提升良率、優化性能、降低成本等多方面的卓越表現,在半導體封裝領域掀起了一場革命。它不僅重新定義了封裝技術的性能邊界,更讓傳統封裝技術在眾多先進應用場景中難以望其項背,正引領封裝業邁入全新發展階段,成為推動半導體產業持續進步的核心力量。

-

半導體

+關注

關注

335文章

28909瀏覽量

237799 -

封裝

+關注

關注

128文章

8677瀏覽量

145478 -

CSP

+關注

關注

0文章

128瀏覽量

28765

發布評論請先 登錄

Hyperabrupt 結調諧變容二極管陶瓷封裝 skyworksinc

突變結變容二極管陶瓷封裝 skyworksinc

IC封裝產線分類詳解:金屬封裝、陶瓷封裝與先進封裝

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

解鎖照明新境界,瑞沃微 CSP1111 以卓越性能引領未來

瑞沃微:一文詳解CSP(Chip Scale Package)芯片級封裝工藝

納芯微推出全新CSP封裝MOSFET產品

瑞沃微CSP封裝技術:重塑手機閃光燈,引領照明創新革命

京瓷光源用的陶瓷封裝產品介紹

封裝業“成本分水嶺”——瑞沃微CSP如何讓傳統、陶瓷封裝漸成 “前朝遺老”?

封裝業“成本分水嶺”——瑞沃微CSP如何讓傳統、陶瓷封裝漸成 “前朝遺老”?

評論