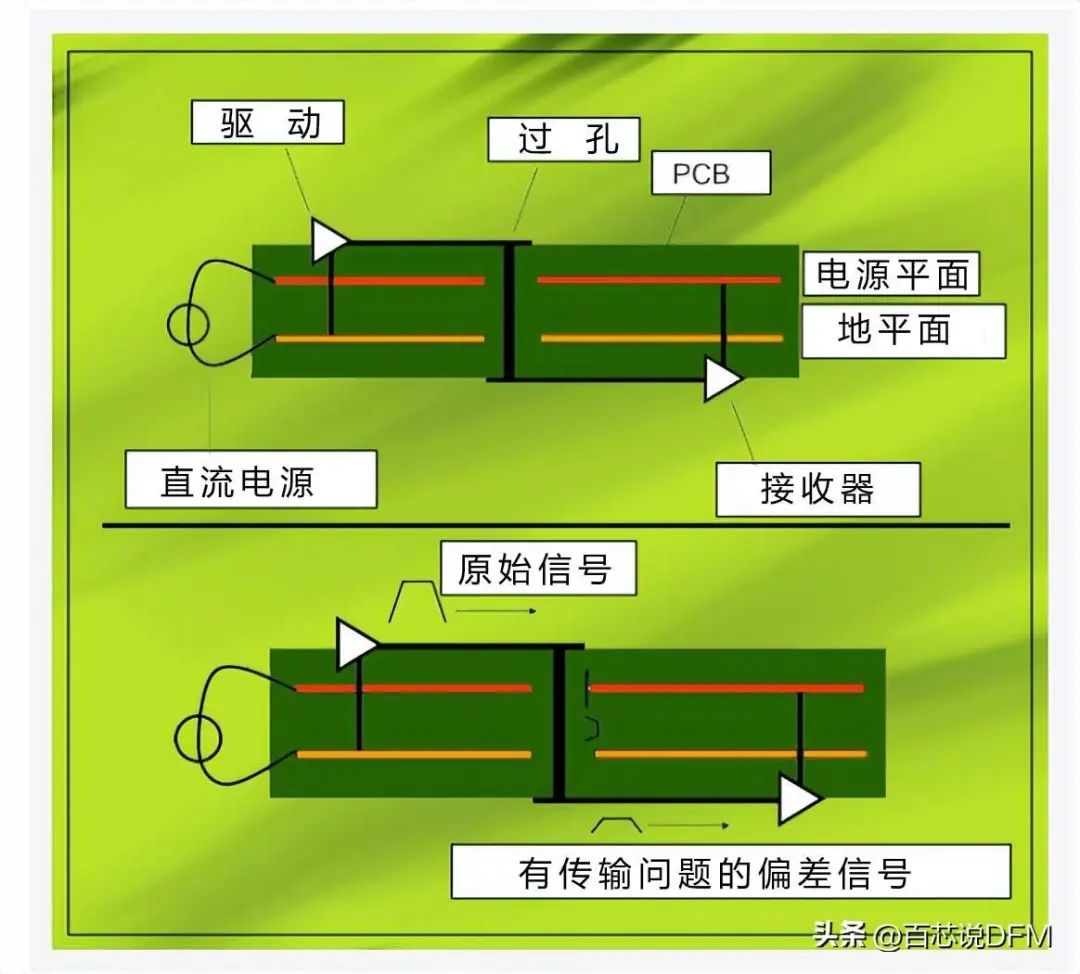

據統計,超過60%的硬件返修源于信號反射、串擾或時序偏差,而傳統依賴仿真的設計方法往往耗時且成本高昂。本文揭示7種經過實測驗證的走線拓撲調整策略,無需深度仿真即可實現90%的信號質量優化,尤其適用于DDR、PCIe、SerDes等高頻場景。

1、點對點直連優先

適用場景:PCIe/USB超高速信號

操作要點:路徑長度差<5mil,過孔數≤1個,差分對間距恒定

2、菊花鏈拓撲適配低速總線

適用場景:I2C/SPI/CAN

操作要點:分支長度差<50mil,末端加1kΩ上拉電阻

3、星型拓撲控負載均衡

適用場景:多負載總線(如RGB LED驅動)

操作要點:主干線寬+20%,分支等長誤差<2mil

4、蛇形線等長補償技術

適用場景:DDR地址/控制信號

操作要點:振幅≤2倍線寬,相位誤差<5mil,間距≥3倍線寬

5、端接電阻降反射策略

適用場景:單端50Ω/差分100Ω信號

操作要點:電阻距接收端≤50mil,阻抗匹配誤差±2%

6、分層隔離提升隔離度

適用場景:模擬/數字混合電路

操作要點:敏感信號布內層,與電源層間距≤4mil,隔離度提升18dB

7、3W原則升級版

適用場景:高頻平行走線(>500MHz)

操作要點:間距擴展至5倍線寬,串擾衰減達15dB

-

pcb

+關注

關注

4367文章

23485瀏覽量

409528 -

PCB設計

+關注

關注

396文章

4801瀏覽量

90376 -

拓撲結構

+關注

關注

6文章

328瀏覽量

40078 -

信號完整性

+關注

關注

68文章

1445瀏覽量

96733

原文標題:PCB如何調整拓撲結構,以此提高信號完整性?

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

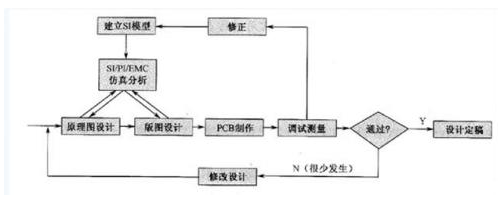

基于信號完整性分析的高速PCB設計

提高信號完整性的PCB材料

基于信號完整性的高速PCB設計流程解析

PCB如何調整拓撲結構,以此提高信號完整性?

PCB如何調整拓撲結構,以此提高信號完整性?

評論