本文要點(diǎn)

了解 EMI 與 EMC 之間的區(qū)別。

采用低功耗器件、隔離技術(shù)、PCB 防護(hù)以及熱管理,減少 EMI 來源。

借助約束管理、信號(hào)完整性分析和實(shí)時(shí) DRC 更新等工具,創(chuàng)建 EMI 優(yōu)化設(shè)計(jì)。

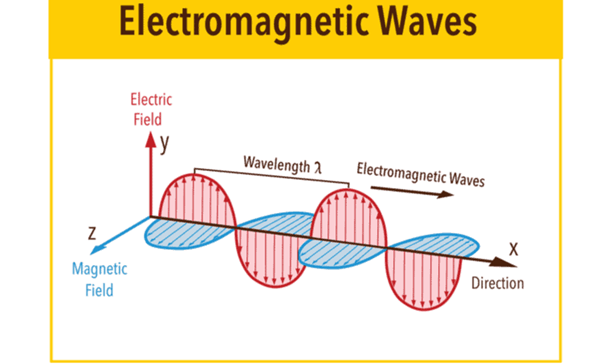

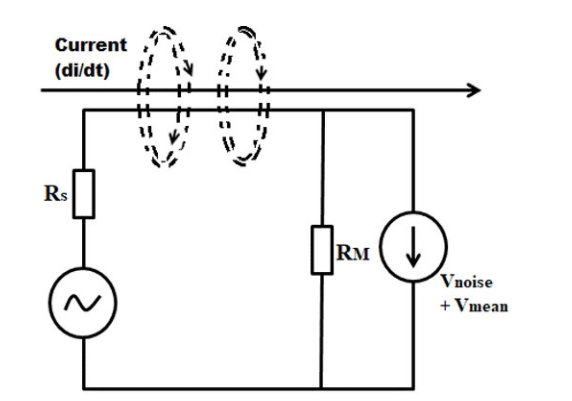

所有電子電路板都用于實(shí)現(xiàn)甚至增強(qiáng)電子流動(dòng),從而達(dá)成特定的性能目標(biāo)。電流沿閉合路徑流動(dòng),會(huì)產(chǎn)生一個(gè)向外擴(kuò)展并垂直于電流方向的磁場(chǎng)。當(dāng)該磁場(chǎng)附近有電子元件或信號(hào)路徑時(shí),就會(huì)發(fā)生電磁干擾(EMI,Electromagnetic Interference)。

許多 PCBA 設(shè)計(jì)首先要考慮的便是如何控制 EMI,尤其是高速電路板。對(duì)于帶有輻射器分類器件的電路板,常見的方法是采用EMI 濾波器設(shè)計(jì)。雖然濾波器效果顯著,但電路板設(shè)計(jì)師還應(yīng)掌握更多 PCB 設(shè)計(jì)方法,這些都是降低 EMI 的重要工具,常常需要靈活運(yùn)用。

電磁干擾的構(gòu)成

EMC 與 EMI:有什么區(qū)別?

大多數(shù) PCBA 并非產(chǎn)品中唯一的電子或電氣設(shè)備。因此,在深入探討單板 EMI 問題之前,最好先從宏觀或系統(tǒng)層面了解 EMI 問題。

正如電磁能量會(huì)從單個(gè)器件、導(dǎo)體或走線中散發(fā)出去,電路板本身也可能向外環(huán)境中釋放電磁波;如果將高斯計(jì)放在 PCB 附近,就能測(cè)量到相關(guān)數(shù)值。當(dāng)多塊電路板緊密相鄰時(shí),實(shí)現(xiàn)電磁兼容性(EMC,Electromagnetic Compatibility) 就顯得尤為重要。

EMC 旨在確保器件之間的 EMI 最小化,從而確保設(shè)備的正常運(yùn)行。雖然 EMI 無法完全消除,但可以實(shí)現(xiàn) EMC。EMI 通常指單塊 PCBA 上的干擾,降低 EMI 有助于提高電路板周圍環(huán)境的 EMC 水平。

EMI 來源分類

聲源 | 描述 |

器件 | 電子器件,尤其是處理器、FPGA、放大器、發(fā)射器、天線等高功率設(shè)備,往往是 EMI 的重要來源。開關(guān)器件也可能產(chǎn)生電磁干擾,對(duì)整個(gè)系統(tǒng)造成破壞。 |

信號(hào)與走線 | EMI 可以沿著走線傳播,也可能在引腳和連接器點(diǎn)處產(chǎn)生。不當(dāng)?shù)牟罘謱?duì)布線可能會(huì)引起信號(hào)衰減和反射,從而影響信號(hào)完整性,甚至導(dǎo)致電路異常行為。此外,雜散電容可能會(huì)導(dǎo)致信號(hào)路徑與接地平面之間出現(xiàn)不必要的耦合 |

外部來源 | 如果電路板距離輻射源(例如其他電路板或元件)太近,則可能會(huì)引入 EMI。電路板周圍其他設(shè)備或裝置的振動(dòng)或移動(dòng)也可能產(chǎn)生諧波。 |

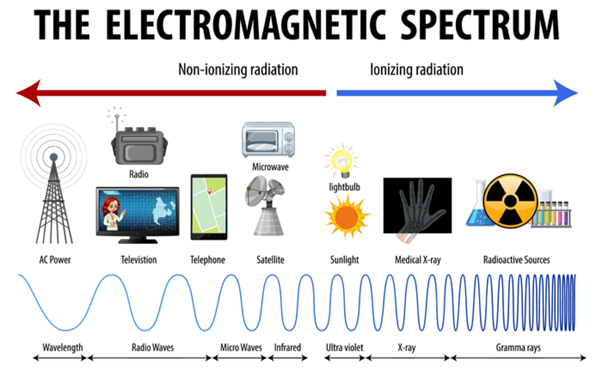

電磁覆蓋無限的頻率范圍,幾乎無處不在。如下圖所示,我們?nèi)粘J褂玫脑S多工具、電器和產(chǎn)品都會(huì)產(chǎn)生電磁輻射。

電磁波譜

如何降低 PCB 器件的 EMI?

如前所述,器件往往是電磁輻射的主要來源,不僅會(huì)影響電路板操作,還可能干擾外部 PCBA 和電子電路。因此,為有效降低 EMI,制定減輕其負(fù)面影響的措施至關(guān)重要,如下所述。

EMC 與 EMI:有什么區(qū)別?

措施 | 描述 |

選擇低功耗器件 | 選擇低功耗器件,降低 EMI。高功耗器件通常會(huì)產(chǎn)生更多的 EMI,低功耗器件即可維持功能。 |

隔離不同類型的器件 | 將處理同類信號(hào)的器件分為一組。將數(shù)字器件彼此靠近放置,并遠(yuǎn)離模擬器件。 |

使用 PCB防護(hù) | 在器件或子電路周圍使用 PCB 保護(hù)環(huán)、法拉第籠或類似的防護(hù),可以有效降低 EMI,同時(shí)防止輻射影響周圍環(huán)境。 |

采用散熱技術(shù) | 使用散熱器和過孔,有效管理器件產(chǎn)生的熱量,最大限度地降低 EMI。 |

EMI 最小化的 PCB layout 設(shè)計(jì)

在電路板布局過程中,間距是重要考量因素之一,包括確保導(dǎo)電元件之間有足夠的間隙和爬電距離。

對(duì)于多層電路板而言,導(dǎo)電平面與接地平面之間的層疊順序和距離也很重要,如下表所示。

如何降低來自信號(hào)和平面的 EMI

措施 | 描述 |

在信號(hào)線之間留出足夠的間隙 | 為有效降低走線之間的 EMI,首要考量因素是間距或間隙。遵循基于 IPC 標(biāo)準(zhǔn)的規(guī)則管理器的建議。 |

確保去耦電容器和旁路電容器接地 | 雜散電容難以完全消除,但可以將電容器盡可能靠近引腳接地,有效減輕此類電容所帶來的影響。 |

采用良好的 EMI 濾波設(shè)計(jì) | 大多數(shù)設(shè)計(jì),尤其是使用數(shù)字信號(hào)的設(shè)計(jì),都包含可能產(chǎn)生信號(hào)失真的開關(guān)器件。在這些情況下,采用濾波器是提高信號(hào)保真度的最佳措施。 |

返回路徑長(zhǎng)度最小化 | 地回路應(yīng)盡可能短。 |

確保差分走線相同 | 對(duì)于差分信號(hào)路徑,走線應(yīng)保持鏡像對(duì)稱,包括走線長(zhǎng)度、銅重量和恒定的間距。如有必要,應(yīng)采用蛇形走線來保持長(zhǎng)度和間距。 |

避免銳角 | 布線時(shí)應(yīng)使用圓角,避免使用銳角,因?yàn)殇J角可能會(huì)改變特性阻抗,導(dǎo)致信號(hào)反射。 |

避免導(dǎo)電層相鄰堆疊 | 在 PCB 堆疊中,切勿將兩個(gè)導(dǎo)電層相鄰放置。最好用接地平面將它們分開。 |

小心處理分割地平面 | 對(duì)于不同類型的信號(hào),最好使用單獨(dú)的接地層。但如果采用了分割接地平面,務(wù)必確保通過單點(diǎn)接地的方式將各接地層連接起來。 |

PCB layout(包括器疊層結(jié)構(gòu))有助于確保良好的信號(hào)完整性和降低 EMI。然而,任何旨在降低 EMI 的 PCB 設(shè)計(jì)指南,如果不涉及外部 EMI 的抑制措施,都是不完整的。

避免外部 EMI

最大限度地減少外部 EMI對(duì)于電路板上的信號(hào)完整性和電路運(yùn)行非常重要,并且有助于 PCBA 安裝環(huán)境的 EMC。以下是可以采取的措施。

如何降低外部來源的 EMI

使用屏蔽裝置:屏蔽裝置通常用于覆蓋特定的器件或子電路。與圍欄不同,屏蔽裝置通常由絕緣材料制成,放置在器件頂部或?qū)⑵渫耆忾]。

使用外殼:外殼通常被視為安全裝置。然而,外殼也能有效保護(hù)電路板免受碎屑和外部 EMI 的影響。

以上關(guān)于器件、layout 和外部來源的 PCB 設(shè)計(jì)指南,均有助于降低電路板上的 EMI,并改善電路板運(yùn)行環(huán)境的 EMC。此外,要高效地實(shí)施這些設(shè)計(jì)指南,往往需要借助專門的設(shè)計(jì)工具。點(diǎn)擊下圖查看白皮書,了解 Cadence 提出的自動(dòng)化仿真工作流程,并且能夠高效地創(chuàng)建 EM 仿真設(shè)計(jì),來實(shí)現(xiàn)快速上市的產(chǎn)品開發(fā)過程。

-

pcb

+關(guān)注

關(guān)注

4358文章

23446瀏覽量

407789 -

emi

+關(guān)注

關(guān)注

53文章

3732瀏覽量

130558 -

emc

+關(guān)注

關(guān)注

172文章

4135瀏覽量

186252

發(fā)布評(píng)論請(qǐng)先 登錄

在設(shè)計(jì)PCB時(shí)應(yīng)該考慮EMC、EMI的哪些規(guī)則

PCB板EMC/EMI 的設(shè)計(jì)技巧

PCB設(shè)計(jì)中EMC/EMI的仿真

數(shù)字電路PCB設(shè)計(jì)中的EMI控制技術(shù)

數(shù)字電路PCB設(shè)計(jì)中的EMC/EMI控制技術(shù)介紹

FPGA-PCB優(yōu)化技術(shù)降低制造成本

分享:PCB板EMC/EMI 的設(shè)計(jì)技巧

如何在PCB設(shè)計(jì)階段處理好EMC及其EMI的問題呢?

PCB設(shè)計(jì)中EMC/EMI的仿真

怎樣降低PCB的EMI

如何在降壓轉(zhuǎn)換器設(shè)計(jì)中降低EMI的實(shí)用技巧

技術(shù)資訊 I 如何在 PCB 中降低 EMI 并優(yōu)化 EMC?

技術(shù)資訊 I 如何在 PCB 中降低 EMI 并優(yōu)化 EMC?

評(píng)論