CMOS的邏輯門如何應用在電路中

前言

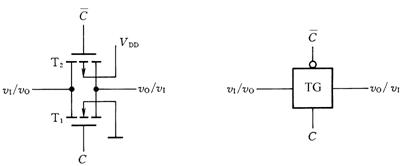

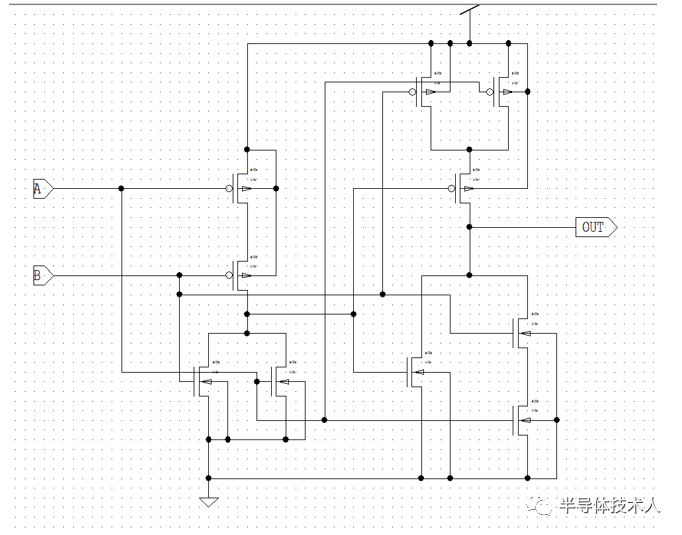

在如今的電子電路中,CMOS邏輯門有著接近零靜態功耗和超高集成度的特點,是數字電路不可或缺的存在。其獨特之處在于PMOS與NMOS晶體管的互補設計:當輸入低電平時,PMOS導通實現電流上拉;輸入高電平時,NMOS導通完成信號下拉。兩種晶體管交替工作,構成無直流通路的完美配合。合科泰采用的溝槽屏蔽柵工藝優化了晶體管性能,讓CMOS互補管在開關切換的電路降低,滿足現代互聯網和人工智能的能耗要求。

CMOS邏輯門

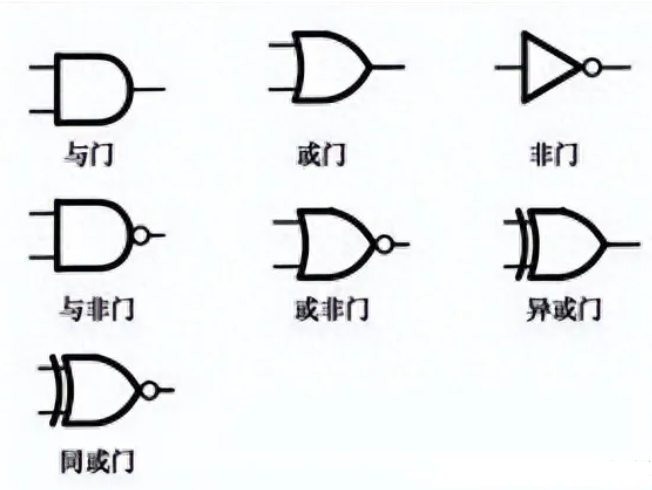

CMOS通過晶體管的不同組合,構建起基礎的邏輯功能:

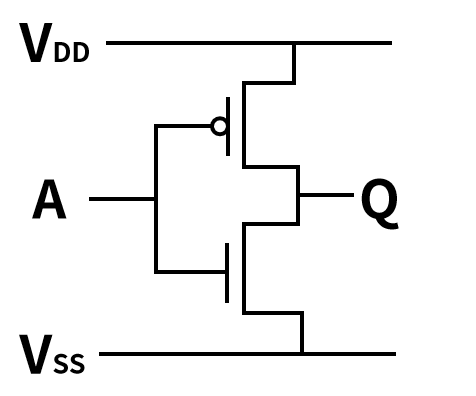

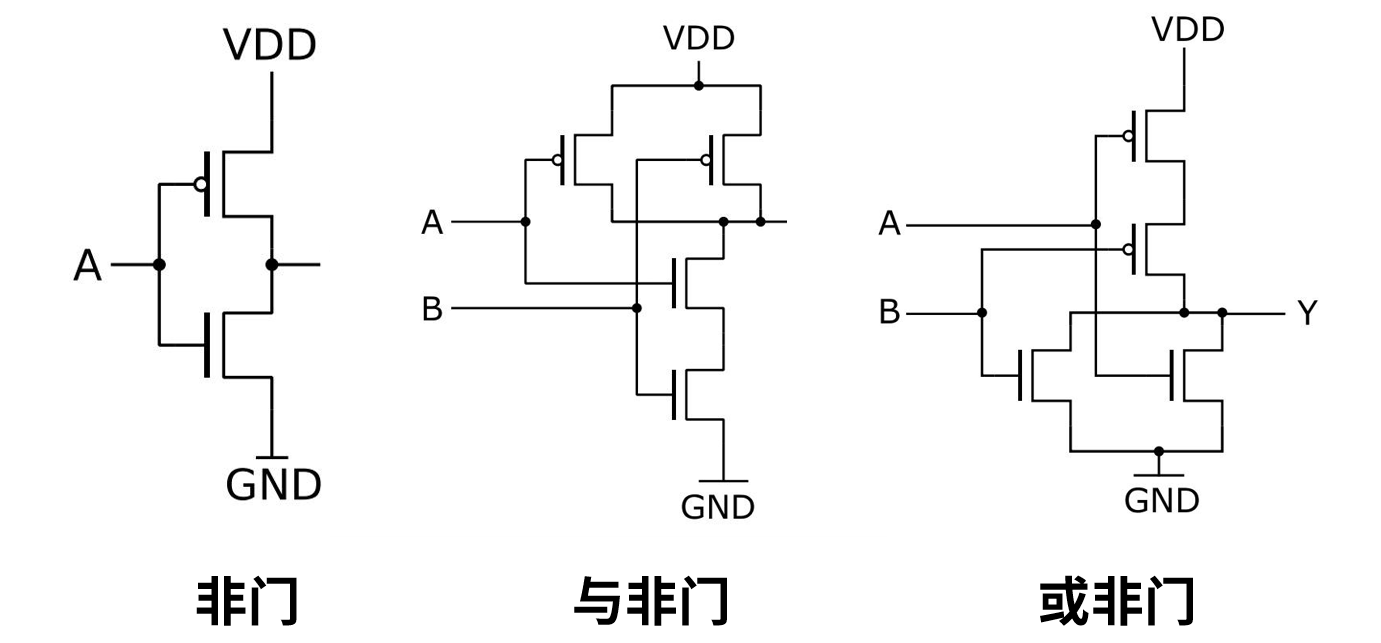

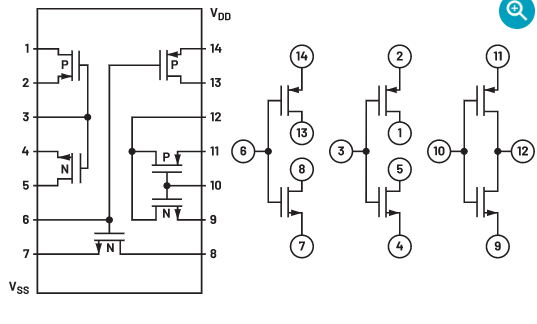

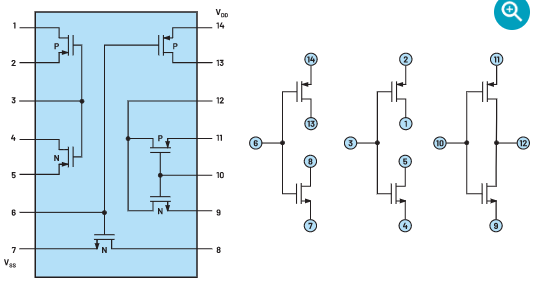

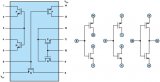

非門(反相器):當輸入高電平時,NMOS導通,而PMOS截止,輸出低電平;輸入低電平的時候則相反,輸出接高電平。無論輸入高或低,只有一個管導通,且沒有直流的通路,靜態時幾乎為0功耗。

與非門(NAND):當兩個輸入信號都是高電平時,串聯的NMOS將輸出牢牢拉向低電平;只要任一輸入為低,并聯的PMOS立即將輸出推回高電平。這種"全高得低,有低得高"的特性,幫助處理器解碼指令。

或非門(NOR):任一輸入是高電平時,并聯的NMOS將輸出下拉至低;只有當所有輸入歸零,串聯的PMOS才會輸出高電平。這種設計常在內存存取控制看見。

CMOS的電路設計挑戰

CMOS電路設計的物理挑戰兩個,一個是尺寸縮小后短溝道電場滲透、漏電流導致靜態功耗高等問題。而在實際應用中,CMOS電路面臨著功耗控制、噪聲與信號完整等挑戰:

功耗控制挑戰:高頻應用如手機處理器中,其開關損耗會伴隨頻率變化,而線性增加,進一步會加強芯片發熱。而MOS管的低漏電流,可以降低處理器靜態時的能耗損失,由此增強續航。

信號傳輸完整和速度:電路的布線密度高,相鄰的電容、電感耦合會產生信號的干擾。如數據中心中的信號傳輸,要求兆赫茲級別的開關頻率。

電源噪聲:工廠電機開啟和關閉的時候,電源電路的變化導致電壓的波動,進而產生噪聲。如MOS管HKTQ50N03通過穩定噪聲的容限,從而控制信號的準確與可靠性。

這些特性讓CMOS可以運用在很多電路上,智能手環通過微型與非門的陣列去處理傳感器的信號;電動汽車控制器用或非門的陣列來管理電池狀態;甚至在衛星通信的設備當中,數百萬個邏輯門就在方寸之間完成數據的編碼和解碼。

結語

CMOS邏輯門的性能需要每個晶體管的高品質決定。其中的PMOS需要有高正電壓響應的能力,NMOS則需要具備快速導通的特性,這兩者還需要在毫秒級的開關當中進行協同。這對MOS管提出了更高的要求和穩定性表現。深耕半導體領域數十年的合科泰,正以此為目標精進MOS管技術。

審核編輯 黃宇

-

CMOS

+關注

關注

58文章

6001瀏覽量

238287 -

邏輯門

+關注

關注

1文章

143瀏覽量

24873

發布評論請先 登錄

CMOS的邏輯門如何應用在電路中

CMOS的邏輯門如何應用在電路中

評論