概要

本文主要基于 Altera Stratix10 和 Agilex 7 FPGA 在客戶實(shí)際應(yīng)用中遇到的電源管理及配置問題,系統(tǒng)梳理了典型故障案例、解決方案與調(diào)試建議。內(nèi)容主要涵蓋:

電源與配置的流程

6 大實(shí)戰(zhàn)案例解析

關(guān)鍵檢查方向與調(diào)試建議

Stratix10 和 Agilex 7 是 Altera 的兩款高端 FPGA (現(xiàn)場(chǎng)可編程門陣列) 產(chǎn)品系列。

Stratix10:

Altera Stratix系列可幫助交付性能高端、品質(zhì)優(yōu)異的產(chǎn)品。Stratix10 FPGA 和 SoC FPGA 在性能、能效、密度和系統(tǒng)集成方面都具有創(chuàng)新優(yōu)勢(shì),工藝為 Altera 14nm 器件。Stratix10 器件采用變革性的英特爾Hyperflex FPGA 架構(gòu),并結(jié)合英特爾 Embedded Multi-Die Interconnect Bridge (EMIB) 專利技術(shù)、Advanced Interface Bus (AIB) 和不斷壯大的芯粒產(chǎn)品組合,性能比上一代高性能 FPGA 提升高達(dá) 2 倍。

Agilex 7:

Altera Agilex 7 FPGA 為 Altera 10nm 器件,采用第二代 Hyperflex FPGA 架構(gòu),支持 PCIE Gen5 X16,116Gpbs PMA4,32GBHBM2E,400G 硬 MAC,DDR5,最大 4.1 百萬(wàn)門邏輯資源等,廣泛應(yīng)用于數(shù)據(jù)中心加速、邊緣計(jì)算、高帶寬網(wǎng)絡(luò)通信、高端儀器儀表等行業(yè),以優(yōu)異的性能廣受客戶喜愛。

Altera Stratix10 和 Agilex 7電源配置流程詳解

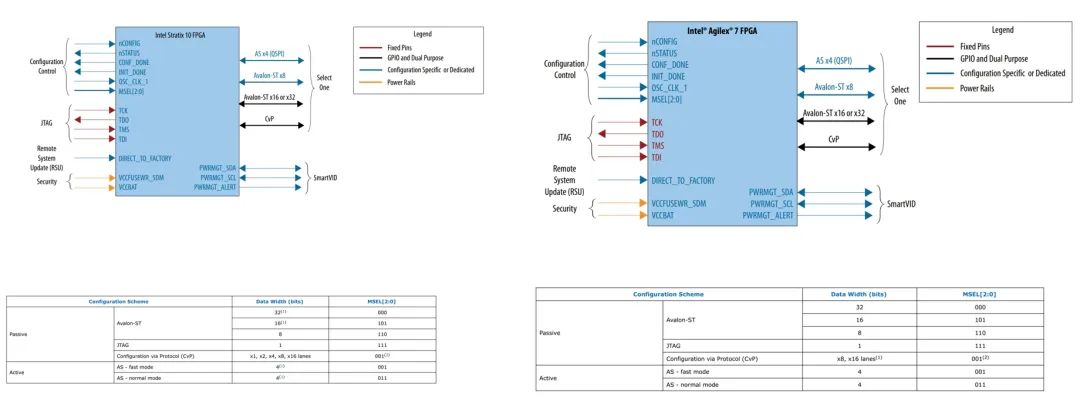

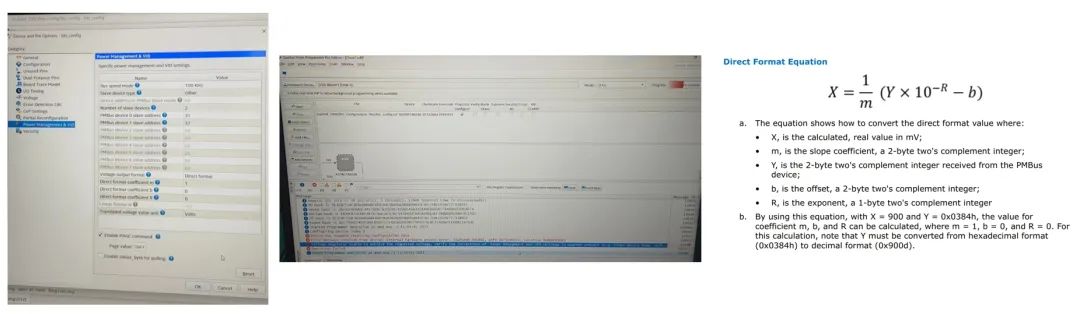

下圖 (圖1) 為 Altera Stratix10/Agilex 7 電源管理及配置的界面。該系列支持的配置模式如下:

Avalon streaming (Avalon-ST)

JTAG

Configuration via Protocol (CvP)

Active Serial (AS) normal and fast modes

圖1 Altera Stratix 10/Agilex 7電源管理及配置界面

Altera Stratix10/Agilex 7 配置流程如下:

Step1:上電 (Power UP)

Altera Stratix 10/Agilex 7 電源需根據(jù)電源管理用戶指南中的器件的上電順序要求進(jìn)行供電。

電源達(dá)到正確操作電壓后,一個(gè)器件范圍 Power on Reset (POR) 會(huì)置位。在電源達(dá)到操作電壓之前,外部電源斜坡 (ramp) 不得慢于最小斜坡速率 (ramping rate)。

配置期間,內(nèi)部電路從內(nèi)部拉低 SDM_IO0, SDM_IO8 和 SDM_IO16。內(nèi)部電路將剩下的 SDM_IO 管腳拉至一個(gè)弱高電平。

POR 之后,內(nèi)部電路也將所有的 GPIO 管腳拉至一個(gè)弱高電平,直到器件進(jìn)入用戶模式 (user mode)。

Step2:SDM 啟動(dòng) (SDM Startup)

SDM 在上電期間對(duì) MSEL 管腳進(jìn)行采樣。

如果 MSEL 設(shè)置為 JTAG,那么 SDM 保持在 Startup 狀態(tài)。

SDM 運(yùn)行存儲(chǔ)在 on-chip boot ROM 中的固件,然后進(jìn)入 Idle 狀態(tài),直到主機(jī)驅(qū)高 nCONFIG。在所有時(shí)鐘穩(wěn)定之前,主機(jī)不應(yīng)該驅(qū)高 nCONFIG。

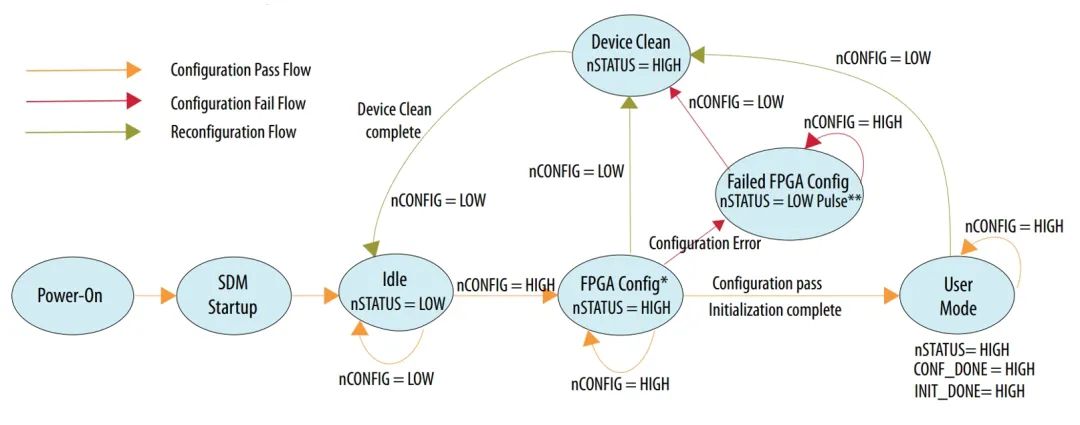

Step3:空閑 (Idle)

在外部主機(jī)通過將 nCONFIG 管腳從低電平驅(qū)動(dòng)為高電平來(lái)啟動(dòng)配置之前,SDM 一直保持在 IDLE 狀態(tài)。或者 SDM 在退出錯(cuò)誤狀態(tài)后進(jìn)入空閑狀態(tài)。

Step4:配置開始 (Configuration Start)

SDM 接收到一個(gè)配置啟動(dòng)請(qǐng)求(nCONFIG = HIGH)后, SDM 通過驅(qū)高 nSTATUS 管腳來(lái)表明配置開始。

接收到配置數(shù)據(jù)時(shí), SDM 執(zhí)行認(rèn)證,解密和解壓縮。

nCONFIG 管腳在配置期間和用戶模式下保持為高電平。主機(jī)持續(xù)監(jiān)控 nSTATUS 管腳以查找配置錯(cuò)誤。

Step5:配置通過 (Configuration Pass)

SDM 在成功接收到完整比特流后驅(qū)高 CONF_DONE 管腳。

CONF_DONE 管腳向外部主機(jī)發(fā)出信號(hào),表示比特流傳輸成功。

Step6:配置錯(cuò)誤 (Configuration Error)

nSTATUS 管腳上的一個(gè)低脈沖表明一個(gè)配置錯(cuò)誤。

錯(cuò)誤要求重配置。

一個(gè)低脈沖 (表明一個(gè)錯(cuò)誤) 后,配置停止。nSTATUS 管腳保持高電平。

發(fā)生錯(cuò)誤后,SDM 在外部主機(jī)驅(qū)低 nCONFIG 之后驅(qū)低 nSTATUS。

nSTATUS 管腳恢復(fù)到初始預(yù)配置低狀態(tài)后,器件進(jìn)入 Idle 狀態(tài)。

Step7:用戶模式 (User Mode)

初始化內(nèi)部寄存器后,SDM 將 INIT_DONE 管腳驅(qū)動(dòng)為高電平,并從高阻抗?fàn)顟B(tài)釋放 GPIO 管腳。器件進(jìn)入用戶模式。整個(gè)器件不會(huì)同時(shí)進(jìn)入用戶模式。Altera 要求在設(shè)計(jì)中包括 Reset Release。使用 Reset Release Altera FPGA IP 的 nINIT_DONE 輸出將應(yīng)用邏輯保持在復(fù)位狀態(tài),直到整個(gè) FPGA 架構(gòu)處于用戶模式。如果此 IP 沒有包含在設(shè)計(jì)中,那么可能會(huì)導(dǎo)致間歇性的應(yīng)用邏輯故障。

nCONFIG 管腳應(yīng)該在用戶模式下保持高電平。

通過將 nCONFIG 管腳從低電平驅(qū)動(dòng)到高電平,可以對(duì)器件進(jìn)行重配置。

Step8:器件清理 (Device Clean)

在 Device Clean 狀態(tài)中,設(shè)計(jì)停止運(yùn)行。

器件清理 (device cleaning) 清除所有配置數(shù)據(jù)。

器件驅(qū)低 CONF_DONE 和 INIT_DONE。

當(dāng)器件清理 (device cleaning) 完成后,SDM 驅(qū)低 nSTATUS 管腳。

圖2 配置流程

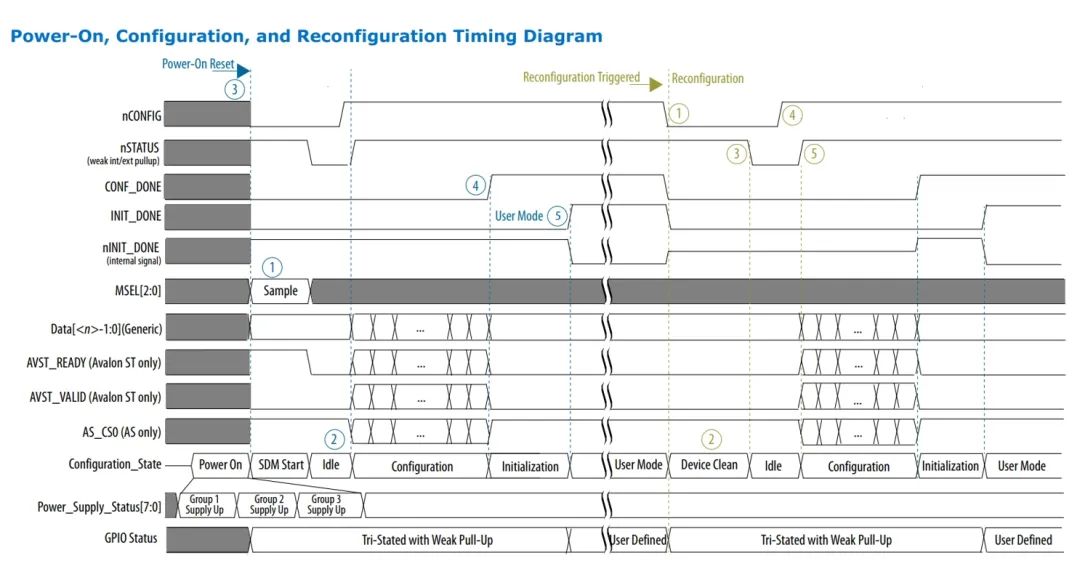

如下圖 (圖3) 所示為配置時(shí)序。圖的第一部分顯示了正常上電復(fù)位后初始配置的預(yù)期時(shí)序。最初,應(yīng)用邏輯驅(qū)低 nCONFIG 信號(hào) (POR)。在正常情況下,nSTATUS 在nCONFIG 后面,因?yàn)?nSTATUS 反映了當(dāng)前配置狀態(tài)。nCONFIG 的值只有在與 nSTATUS 的值相同時(shí)才可以更改。當(dāng)出現(xiàn)錯(cuò)誤時(shí),nSTATUS 拉低大約 1ms,當(dāng)器件準(zhǔn)備好接受重配置時(shí)置位高電平。時(shí)序圖中的初始配置部分中的數(shù)字標(biāo)記以下事件:

1. SDM 啟動(dòng)并采樣 MSEL 信號(hào)以確定指定的 FPGA 配置方案。在下一次上電之前,SDM 不再對(duì) MSEL 管腳進(jìn)行采樣。

2. 當(dāng) nCONFIG 信號(hào)為低電平時(shí),SDM 引導(dǎo)后進(jìn)入 Idle 模式。

3. 當(dāng)外部主機(jī)驅(qū)高 nCONFIG 信號(hào)時(shí),SDM 啟動(dòng)配置。SDM 驅(qū)高 nSTATUS 信號(hào),表示 FPGA 配置的開始。SDM 接收 MSEL 總線在 Step 1中指定的接口上的配置比特流。上圖顯示了 AVST_READY 和 AVST_VALID 持續(xù)為高電平。AVST_READY 可以置低,這要求 AVST_VALID 在六個(gè)周期內(nèi)置低。

4. SDM 驅(qū)高 CONF_DONE 信號(hào),表明 SDM 成功接收到了比特流。

5. 當(dāng) FPGA 置位 INIT_DONE,表明 FPGA 已經(jīng)進(jìn)入用戶模式 (user mode)。GPIO 管腳退出高阻抗?fàn)顟B(tài)。CONF_DONE 與INIT_DONE 的置位之間的時(shí)間是可變的。對(duì)于 FPGA 第一次配置,INIT_DONE 在 FPGA 架構(gòu)的初始化 (包括寄存器和狀態(tài)機(jī)) 后置位。對(duì)于 HPS 第一次配置,HPS 應(yīng)用控制 CONF_DONE 與 INIT_DONE 之間的時(shí)間。運(yùn)行在 HPS 上的軟件 (如 U-Boot) 或者操作系統(tǒng) (OS) 啟動(dòng)配置,F(xiàn)PGA 配置并進(jìn)入用戶模式后, INIT_DONE 才置位。

圖3 配置時(shí)序圖

典型問題案例解析與解決方案

案例一:JTAG 識(shí)別器件異常 (PCN:1SX085H3F43E2VG)

問題描述:

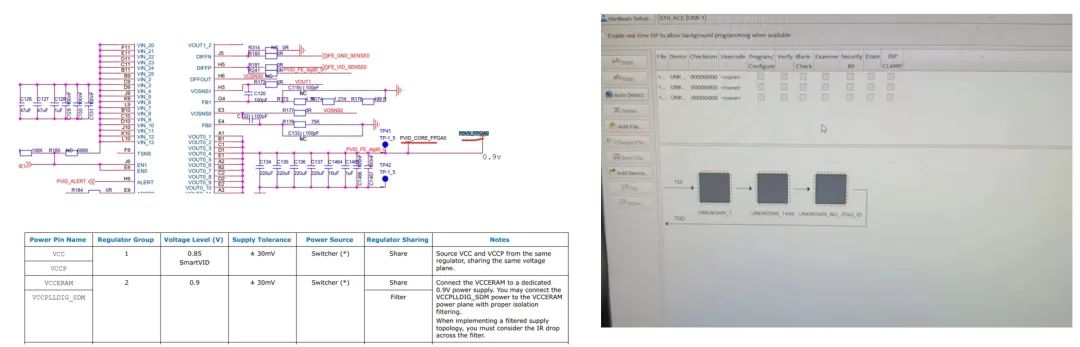

在客戶設(shè)計(jì)中,SmartVID 電源 VCC/VCCP 與 0.9V 電源 VCCERAM/VCCPLLDIG_SDM 共用電源軌,導(dǎo)致 JTAG 識(shí)別不到器件。

解決方案:

把兩個(gè)電源軌分開即可正常識(shí)別器件。

圖4 案例一圖示

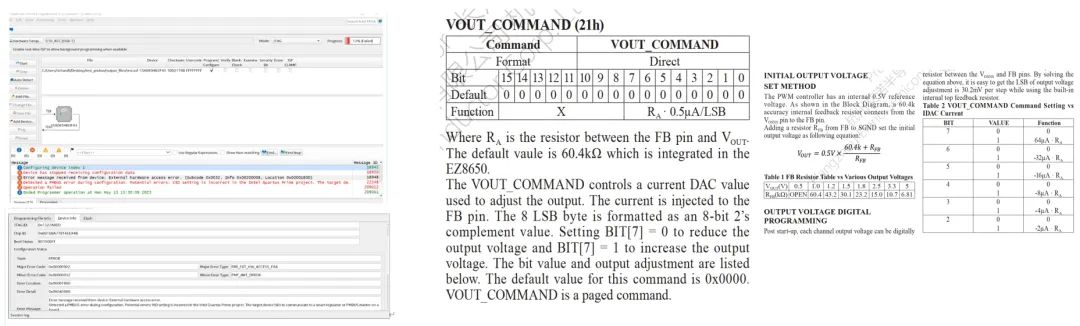

案例二:PMBUS 調(diào)壓失敗 (PCN:1SX085H3F43E2VG)

問題描述:

客戶選用的某國(guó)產(chǎn)電源芯片,電源芯片支持的調(diào)壓方式為 Step,其調(diào)壓步長(zhǎng)定義為 1LSB = RA*0.5uA,一般的電源芯片是 1LSB = 1mV,我們器件通過 PMBUS 設(shè)置的為 Final Vout,導(dǎo)致調(diào)壓不成功。

解決方案:

目前短期通過 INI 文件繞過 PMBUS,手動(dòng)設(shè)置固定電壓,后續(xù)更換為兼容 PMBUS 的電源芯片。

圖5 案例二圖示

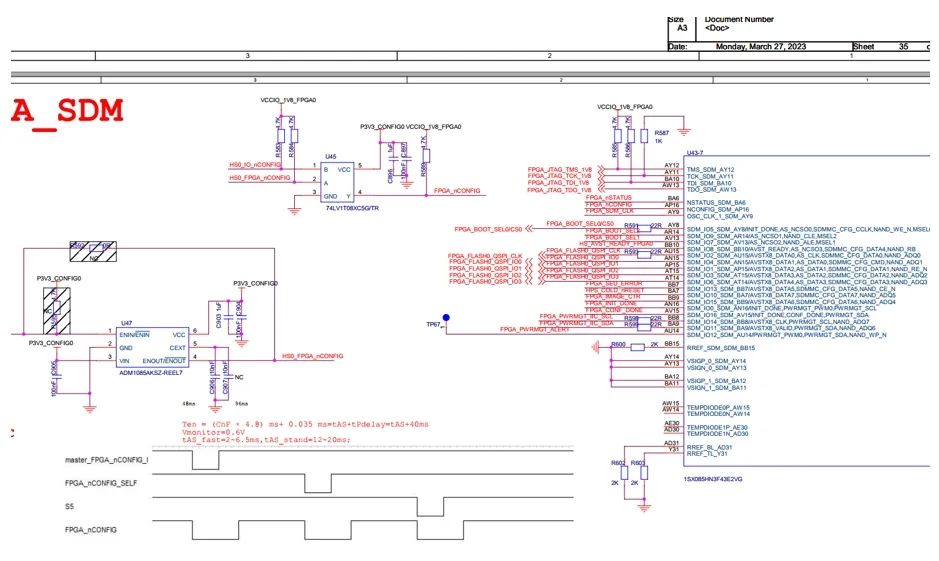

案例三:FPGA 斷電重啟失效 (PCN:1SX085H3F43E2VG)

問題描述:

加載 JIC 配置文件后,設(shè)備斷電重啟時(shí) FPGA 無(wú)法正常完成配置。經(jīng)分析,故障原因?yàn)榭蛻綦娐钒迳系闹骺匦酒瑢?duì)上電時(shí)序邏輯處理異常。具體表現(xiàn)為:

電源時(shí)序沖突:

(1) 系統(tǒng)上電順序?yàn)橹骺匦酒瑑?yōu)先啟動(dòng),目標(biāo) FPGA (Stratix10) 延遲上電。

(2) 主控芯片完成初始化后,立即將 nCONFIG 信號(hào)置為高電平,而非在 FPGA 的 IDLE 狀態(tài)階段觸發(fā)該信號(hào)。

配置流程失效:

目標(biāo) FPGA 在 IDLE 階段未檢測(cè)到 nCONFIG 的有效上升沿,導(dǎo)致配置狀態(tài)機(jī)未能激活,后續(xù)配置過程中斷。

解決方案:

主控芯片上電不要去操作 nCONFIG,通過外部電路操作,上電 Flash 能夠加載,需要 reconfig 時(shí)再通過主控芯片進(jìn)行操作。

圖6 案例三圖示

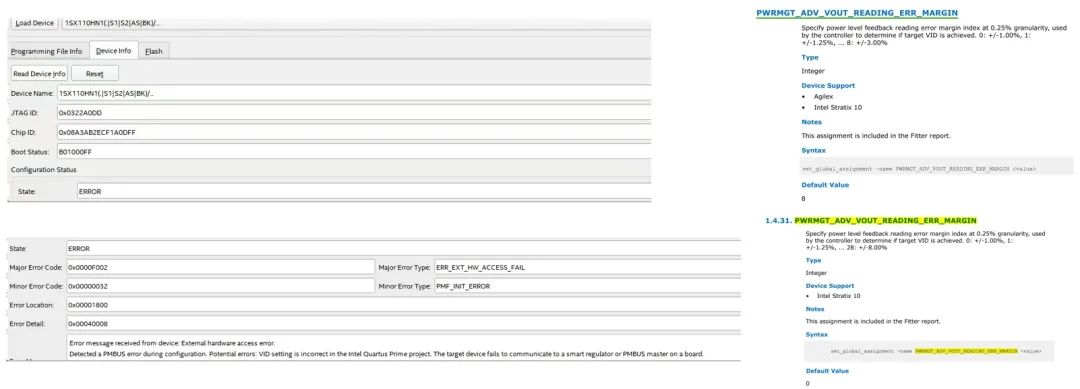

案例四:HPS First 模式加載概率性失敗 (PCN:1SX110H1F43E2VG)

問題描述:

在 HPS First 啟動(dòng)模式下,系統(tǒng)通過 HPS 加載 FPGA 程序,F(xiàn)PGA 程序存儲(chǔ)在 NAND flash。在測(cè)試中發(fā)現(xiàn):

在測(cè)試中的 10 塊板子中,有兩塊存在斷電重啟之后 FPGA 概率性無(wú)法啟動(dòng)現(xiàn)象,有時(shí)候可以啟動(dòng),有時(shí)無(wú)法啟動(dòng)。但通過 JTAG 加載 FPGA first 模式后,都能夠啟動(dòng)。

所有的板子初始供電電壓都是 0.9V,通過示波器觀察異常板子 VID 調(diào)壓后,實(shí)際電壓被調(diào)到了 0.94V,初始電壓值和調(diào)壓值壓差過大,超過了默認(rèn)的 ±3% (老版本最大限制為 ±3%,22.4 版本之后可以調(diào)到 ±8%)。

解決方案:

確認(rèn)異常板卡固件版本,若低于 22.4 需更新版本到 22.4 或者 23.1,通過添加約束 set_global_assignment -name PWRMGT_ADV_VOUT_READING_ERR_MARGIN 28,把壓差擴(kuò)大到 8%。

Intel Quartus Prime Pro Edition Settings File Reference Manual(點(diǎn)擊閱讀原文此處了解)

圖7 案例四圖示

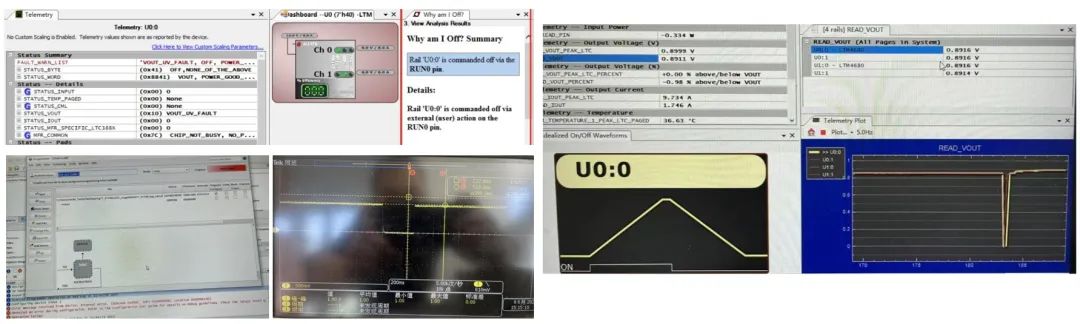

案例五:電源瞬態(tài)欠壓保護(hù) (PCN:AGFB027R24C2E1V)

問題描述:

本案例中使用到的電源芯片為:ADI LTM4680,當(dāng) FPGA 在下載大邏輯資源量 *.sof 的情況時(shí) (60%以上),下載到 99% 時(shí)會(huì)顯示失敗。經(jīng)過排查發(fā)現(xiàn),當(dāng)下載失敗時(shí),F(xiàn)PGA 的整板四組電源 RUN 使能管腳均被拉低斷電。

由于板級(jí)存在上電時(shí)序管理芯片,一旦第一組核電發(fā)生異常,上電時(shí)序管理芯片會(huì)觸發(fā)保護(hù)機(jī)制,后級(jí)將全部被關(guān)閉。為驗(yàn)證此問題,我們將上電時(shí)序改為 CPLD 獨(dú)立控制。在此配置下,發(fā)現(xiàn)核電會(huì)出現(xiàn)短暫的“掉坑”現(xiàn)象,大約持續(xù) 240ms。通過與 ADI 電源廠家溝通,利用上位機(jī)工具對(duì) FPGA 下載過程中的電源狀態(tài)進(jìn)行實(shí)時(shí)監(jiān)控,成功復(fù)現(xiàn)了這一現(xiàn)象。

經(jīng)過反復(fù)測(cè)試,抓取到電源異常時(shí)報(bào)出的一個(gè)輸出欠壓警告信息,經(jīng)過 ADI 的 AE 和我們的 AE 一起分析,確認(rèn)問題的根本原因?yàn)椋涸谪?fù)載劇烈變化時(shí),電源輸出電壓出現(xiàn)瞬態(tài)欠壓,進(jìn)而觸發(fā)保護(hù)機(jī)制。

解決方案:

通過調(diào)整電源管理器的輸出欠壓保護(hù)閾值,將欠壓門限從默認(rèn)值降低至 0.2V,邏輯版本為 66% 和 70% 的資源量均可成功下載,電源系統(tǒng)也未再出現(xiàn)瞬態(tài)“掉坑”現(xiàn)象。

圖8 案例五圖示

案例六:MBR 配置錯(cuò)誤導(dǎo)致 JTAG 加載失敗 (PCN:AGFB014R24B2E2V)

問題描述:

通過 jtag 加載 sof 文件時(shí),加載到 35% 時(shí)會(huì)顯示失敗。經(jīng)過分析,將問題定位在 MBR 配置不對(duì),具體表現(xiàn)為:客戶使用的電源芯片精度為 1LSB = 2mV,而當(dāng) MBR = 100 時(shí),實(shí)際需要 1LSB = 1mV 的精度,兩者存在規(guī)格不匹配的情況。

解決方案:

目前為客戶提供了繞過 PMBUS 的 ini 文件,確保客戶可先正常調(diào)試功能,同時(shí)也與電源芯片供應(yīng)商進(jìn)行技術(shù)溝通,以確定 MBR 參數(shù)的最佳配置方案。

圖9 案例六圖示

Altera Stratix10 和 Agilex 7

電源配置問題檢查方向

檢查方向

jtag 加載失敗問題:首先要檢查 quartus 配置參數(shù)是否與電源芯片相符,包括電源引腳,PMBUS 地址,MBR 參數(shù)設(shè)置值以及 valid unit 和 mode 等

器件識(shí)別異常:確認(rèn)供電是否滿足 datasheet 要求以及 pcg 要求

Flash 加載異常和加載之后不工作:檢查 MSEL 配置是否正確,以及 nconfig,nstatus,configdone,initial done 是否正常

Debug

每家電源廠家都有上位機(jī)軟件監(jiān)控電源狀態(tài),異常時(shí)可以通過電源上位機(jī)軟件抓取電源狀態(tài),查看異常情況

Quartus 提供了config debug 工具,異常時(shí)可以看到在什么階段異常,錯(cuò)誤碼是什么,然后進(jìn)行分析

如果是 PMBUS 問題,且暫時(shí)沒有解決方案,可以提供繞過 PMBUS 的方法讓客戶先進(jìn)行功能調(diào)試,這樣不會(huì)阻塞客戶調(diào)試進(jìn)度 (該方案實(shí)測(cè)在最新版本 23.2 以及 agilex 上可用)

最重要一點(diǎn)是客戶投板之前一定要進(jìn)行原理圖 review 和 pin map 驗(yàn)證

總結(jié)

本文通過列舉 Altera Stratix10 和 Agilex 7 FPGA 在客戶實(shí)際應(yīng)用中遇到的電源管理及配置問題案例,為大家系統(tǒng)梳理了典型的故障問題分析,同時(shí)給出相應(yīng)的解決方案與調(diào)試建議,供工程師們參考。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21989瀏覽量

615195 -

英特爾

+關(guān)注

關(guān)注

61文章

10182瀏覽量

174128 -

電源管理

+關(guān)注

關(guān)注

117文章

6411瀏覽量

145891 -

Altera

+關(guān)注

關(guān)注

37文章

803瀏覽量

155630 -

Agilex

+關(guān)注

關(guān)注

0文章

15瀏覽量

3839

原文標(biāo)題:Altera Stratix?10 和 Agilex? 7 電源配置問題案例解析

文章出處:【微信號(hào):駿龍電子,微信公眾號(hào):駿龍電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于Altera Agilex? 7 400G Ethernet IP 與FPC202芯片控制使用手冊(cè)

淺析Altera公司Stratix V FPGA芯片

二手FPGA

Stratix 10 MX FPGA是什么?Stratix 10 MX FPGA有哪些功能?

Altera Stratix IV FPGA助推XDI db

Altera推出面向Stratix IV FPGA的最新開發(fā)

Altera Stratix IV FPGA繼續(xù)廣受全球媒體

Altera推出業(yè)界帶寬最大的28nm Stratix V

Altera助推客戶啟動(dòng)14 nm Stratix 10 FPGA和SoC設(shè)計(jì)

業(yè)界密度最大的Stratix IV EP4SE820 FPGA(Altera)

深度解讀:Intel最新的FPGA Agilex

具有LVDS輸出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

Altera Agilex 7 M系列FPGA正式量產(chǎn)出貨

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

Altera Stratix 10和Agilex 7 FPGA的電源管理及配置問題案例

Altera Stratix 10和Agilex 7 FPGA的電源管理及配置問題案例

評(píng)論