3D 異質(zhì)集成 (3DHI) 技術(shù)可將不同類型、垂直堆疊的半導(dǎo)體芯片或芯粒 (chiplet) 集成在一起,打造高性能系統(tǒng)。因此,處理器、內(nèi)存和射頻等不同功能可以集成到單個芯片或封裝上,從而提高性能和效率。隨著 3DHI 系統(tǒng)越來越復(fù)雜,UCIe (Universal Chiplet Interconnect Express) 標(biāo)準(zhǔn)變得非常重要,對于未來的先進(jìn)封裝和半導(dǎo)體系統(tǒng)設(shè)計而言極為關(guān)鍵。由于這些技術(shù)的專業(yè)性,以及呈指數(shù)級增長的計算需求,設(shè)計周期變慢,產(chǎn)品的上市時間線也被拉長。

Cadence 專門為簡化設(shè)計流程而開發(fā)的解決方案可提供 UCIe 全方位信號完整性分析和異構(gòu)集成的合規(guī)性檢查。本文詳細(xì)介紹了該分析解決方案和設(shè)計架構(gòu),并分享了來自 Cadence 及其客戶的各種測試案例,這些客戶在不斷推動該行業(yè)標(biāo)準(zhǔn)的發(fā)展,也使得現(xiàn)有的分析能力面臨挑戰(zhàn)。

異構(gòu)集成

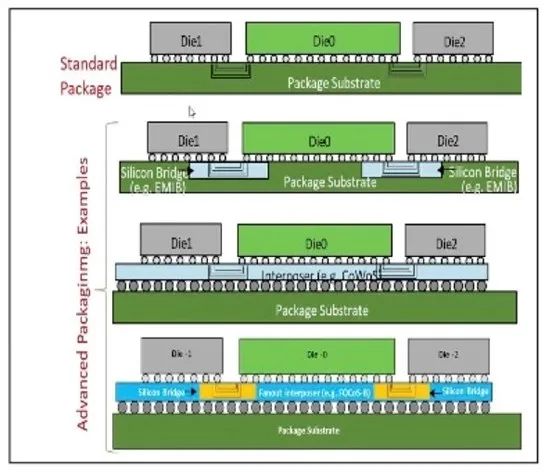

許多行業(yè)領(lǐng)導(dǎo)者目前都在進(jìn)入異構(gòu)集成領(lǐng)域,努力開拓新的機(jī)遇。下圖顯示了標(biāo)準(zhǔn)和先進(jìn)封裝的 2D 和 3D 應(yīng)用場景。

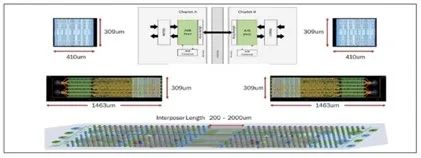

Chiplet(小芯粒)得到大規(guī)模使用的一個先決條件是出現(xiàn) UCIe 等互連標(biāo)準(zhǔn),以及擁有強(qiáng)大工具和設(shè)計流程,用于專門解決 chiplet 面臨的問題。本文討論了一種硅基板的異構(gòu)集成,針對使用 UCIe 接口的 960Gbps 數(shù)據(jù)傳輸進(jìn)行了優(yōu)化。設(shè)計和驗證 chiplet上的輸入/輸出(I/O)和 μbump 陣列時遵循了標(biāo)準(zhǔn)集成電路開發(fā)流程,而 chiplet 在硅基板上的集成則需要一個新的設(shè)計流程,以完整模擬中介層造成的信號失真。下圖展示了 UCIe 接口的關(guān)鍵元件。

完整的信號完整性流程

信號和電源完整性 (SI/PI) 的完整的仿真和分析是系統(tǒng)設(shè)計不可或缺的一部分(見下圖)。

Cadence Sigrity Signal and Power Integrity 和 Clarity 3D Solver 多物理場系統(tǒng)分析 (MSA) 軟件可用于對設(shè)計進(jìn)行全面仿真。Sigrity X SystemSI UCIe 合規(guī)工具包和晶體管到行為 (T2B) 模型轉(zhuǎn)換功能可提供 UCIe 全方位信號完整性分析,并對異構(gòu)集成進(jìn)行合規(guī)性檢查。Sigrity X SystemSI 用于瞬態(tài)(時域)分析和自動 UCIe 合規(guī)工具包檢查。Clarity 3D Layout 用于對布設(shè)在中介層上的 UCIe 接口進(jìn)行全波 3D 有限元法 (FEM) S 參數(shù)提取。

結(jié)論

本文介紹了一個利用 Cadence Sigrity X Platform/Clarity 3D Solver、Allegro X Platform 和 Virtuoso 平臺實現(xiàn)的詳細(xì)解決方案,其中包含一個完整的流程,包括對一個 8 層硅基板進(jìn)行全 3D 提取,該硅基板已針對使用 UCIe 接口的 960Gbps 數(shù)據(jù)傳輸進(jìn)行優(yōu)化。該流程提供了 UCIe 完整的信號完整性分析,并對異構(gòu)集成進(jìn)行了合規(guī)性檢查,還可以詳細(xì)模擬 interposer 上的傳輸線效應(yīng)。

-

芯片

+關(guān)注

關(guān)注

459文章

52253瀏覽量

436917 -

信號完整性

+關(guān)注

關(guān)注

68文章

1437瀏覽量

96490

發(fā)布評論請先 登錄

信號完整性與電源完整性的仿真分析與設(shè)計

信號完整性與電源完整性仿真分析

技術(shù)資訊 I 完整的 UCIe 信號完整性分析流程和異構(gòu)集成合規(guī)性檢查

技術(shù)資訊 I 完整的 UCIe 信號完整性分析流程和異構(gòu)集成合規(guī)性檢查

評論